# A SAR Pipeline ADC Embedding Time Interleaved DAC Sharing for Ultra-low Power Camera Front Ends

Anvesha Amaravati, Manan Chugh, Arijit Raychowdhury

# ▶ To cite this version:

Anvesha Amaravati, Manan Chugh, Arijit Raychowdhury. A SAR Pipeline ADC Embedding Time Interleaved DAC Sharing for Ultra-low Power Camera Front Ends. 23th IFIP/IEEE International Conference on Very Large Scale Integration - System on a Chip (VLSI-SoC), Oct 2015, Daejeon, South Korea. pp.131-149, 10.1007/978-3-319-46097-0\_7. hal-01578616

# HAL Id: hal-01578616 https://inria.hal.science/hal-01578616

Submitted on 29 Aug 2017  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Distributed under a Creative Commons Attribution 4.0 International License

# A SAR Pipeline ADC Embedding Time Interleaved DAC Sharing for Ultra-Low Power Camera Front Ends

Anvesha Amaravati, Manan Chugh & Arijit Raychowdhury

School of Electrical & Computer Engineering, Georgia Institute Of Technology

Abstract. The growing need for ultra-low power cameras for sensors, surveillance and consumer applications has resulted in significant advances in compressed domain data acquisition from pixel arrays. In this journal we present a novel 64-input Successive Approximation (SAR) Pipeline analog-to-digital converter (ADC) suitable for compressed domain data acquisition in camera front-ends. The proposed architecture features a time interleaved capacitive digital-to-analog converter (DAC) shared between column parallel ADCs for area savings (2.28X); and a shared amplifier stage for power savings (60%), achieving 4X throughput as compared to traditional architectures. Simulations on a 130nm foundry process shows that the proposed SAR Pipeline ADC draws  $31\mu$ W at 2MS/s having a target Figure-of-Merit (FOM) of 87fJ/conv. per step at Nyquist rate. The proposed compressive sensing front end achieves per patch energy per patch of 0.9nJ.

#### 1 Introduction

Mobile devices for IOT (Internet of Things) require CMOS image sensor (CIS) with low power and area [1]. Traditional CIS for wearable devices consume power more than 50mW[2].In a CMOS image sensor system the most power consuming blocks are: digital image processing back end & column parallel ADCs[3][4]. In most of the reported image sensors, column parallel ADCs draw 50-65% of the power of the entire image sensor signal acquisition chip[5][1]. The power consumed by column parallel ADCs is proportional to the number of measurements to be performed by the ADC. It increases with the number of pixels. For next generation IoT devices like "always on" Camera based image sensors, human machine interface systems with built in machine intelligence, low power is the key enabler.

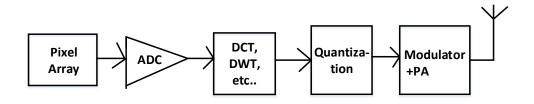

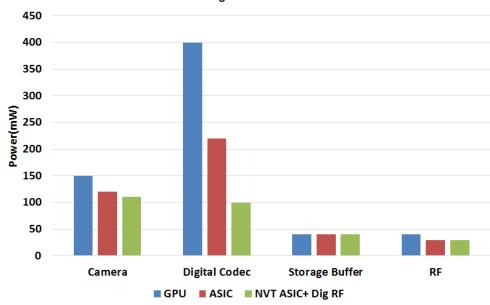

Fig. 1 shows the traditional nyquist domain signal processing. Pixel voltages are digitized using high speed column parallel ADCs. Digitized image is encoded using algorithms like discrete cosine transform (DCT), discrete wavelet transform (DWT) etc. The power budget for transmitter blocks is shown in in Fig. 2. We can observe that encoding part like DCT, DWT consumes significant amount of power followed by Analog to Digital signal acquisition etc. As the resolution of the image goes up the number of measurements per ADC goes up and hence the encoding power also increases. This places huge power constraint on acquisition device and transmitter.

Fig. 1. Traditional nyquist signal acquisition and transmission

Power budget for various blocks

Fig. 2. Power budget for various blocks in transmitter

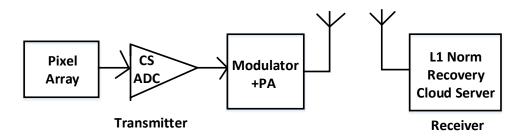

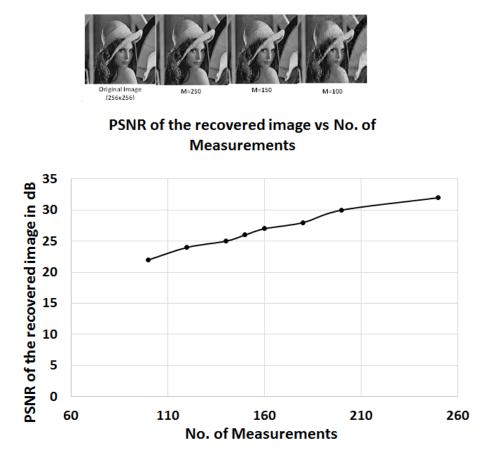

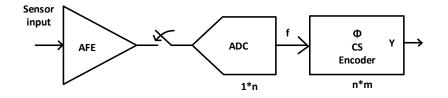

Recently developed algorithms of compressive sensing (CS) promise to reduce the number of measurements with non-linear recovery at the back-end [6]. The signal processing chain for compressing sensing is shown in Fig. 3. This approach makes the encoding done at the transmitter simpler by completely eliminating power hungry blocks like DCT, DWT. If the pixel values in a camera are represented as a discrete time signal  $X = [x_1 x_2 x_3 x_4 \cdots x_n]^T$ , the number of measurements needed in traditional column parallel ADCs will be equal to n. Instead of n samples, CS needs only m linear measurements ( $m \ll n$ ). Fig. 4 shows the plot of PSNR of the recovered image w.r.to number of measurements done at receiver. We can observe that to achieve PSNR of 30dB, 250 measurements are sufficient. PSNR of 30dB is sufficient for classifying objects[11]. Therefore the value of m can be as small as n/250. Therefore compressive sensing achieves significant reduction is encoding power & transmission bandwidth. The CS measurement matrix is given by Eq. 1.

$$Y[m] = \phi[m, n] \times X[n] = \begin{pmatrix} 0 \ 1 \cdots \ 1 \\ 1 \ 1 \cdots \ 0 \\ \vdots \vdots \ddots & \vdots \\ 1 \ 0 \cdots \ 0_{m,n} \end{pmatrix} \times \begin{pmatrix} x_1 \\ x_2 \\ \vdots \\ x_n \end{pmatrix}$$

(1)

Fig. 3. Compressed domain signal acquisition & transmission

Here Y[m] is the *m*-dimensional measured array,  $\phi$  is a random binary matrix of size m \* n and follows the "Independent and Identically Distributed (IID)" property. X is traditionally recovered at the back-end using an optimization algorithm, like determining the  $L_1$  norm[6].

In this paper we present a novel pipeline-SAR ADC architecture with capacitive DAC sharing with the capability of acquiring linear combinations of 64 pixel data in a single conversion cycle. This is suitable for such compressed domain data acquisition.

### 2 ADC Architectures for CS Image Acquisition

In prior work for obtaining compressed domain data, both analog and digital techniques have been used to perform compressive measurements from the raw data. Typically, analog implementations of compressed sensing require an analog to digital converter to improve accuracy & digital transmission[7][8]. Resistor based compressed sensing multiplexor reported in [9], suffers from static power dissipation and the number of inputs (n) is limited, making it suitable for RF receiver applications only.

Fig. 4. Recovered image using L1 norm

To overcome some of the disadvantages of analog CS circuits, [10] has proposed compression in the digital domain after Analog to Digital Conversion. Fig. 5. a) shows the technique proposed in [10]. The entire analog signal is converted into the digital domain by high-speed ADCs and the CS encoder does compression in the digital domain. This is primarily suited for low bandwidth application like bio-medical signal processing. However, for CIS of a typical 256 \* 256 size, ADCs would need to acquire all the samples and then convert to the digital domain. The number of measurements by the ADC will not be reduced and it defeats the purpose of compressed domain data acquisition. Therefore ADC power will remain the same for image acquisition. Further, the size of digital CS encoder grows exponentially with the number of inputs. CS encoders will further add significant power along with the ADC making it infeasible for "always on" imaging front-end applications.

Fig. 5. CS encoder on acquired samples of ADC[10]

Fig. 6. Simultaneous compression and quantization within [5]

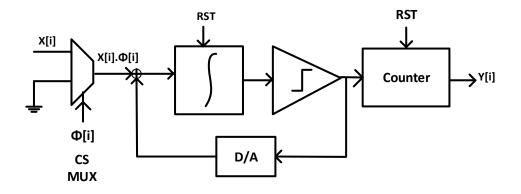

To overcome the limitations of data acquisition followed by compressed domain measurements, Oike et.al, has proposed a CS camera through simultaneous averaging and quantization of pixels using a  $\Sigma - \Delta$  ADC [5]. Fig. 5. b) shows the schematic of the resetting  $\Sigma - \Delta$  ADC used for such linear measurements. Pixel values are multiplied with random numbers (from the  $\phi$  matrix) sequentially and passed to the input of the  $\Sigma - \Delta$  ADC. This approach requires m measurements; however it requires n conversion cycles for one measurement. This architecture requires a 16 \* 16 block for linear measurement. For each measurement of the block, the resetting  $\Sigma - \Delta$  ADC needs 256 clock cycles. For m measurements  $\Sigma - \Delta$  ADC needs n\*256 clock cycles. During this conversion period, all the high gain amplifiers will remain on and consume power. Hence, for lowering the total power dissipation, faster conversion with the opportunity for power gating once the conversion is complete, will be critical.

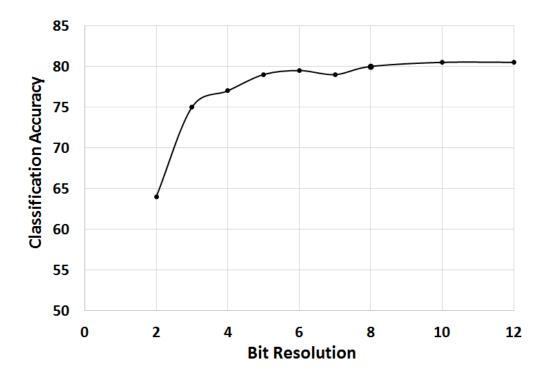

Once compressed domain data is acquired, the image is often used for online classification to detect potential trigger signals. For such in-situ classification [16] and trigger identification, 8bits of inputs are sufficient. We have plotted classification accuracy vs Bit resolution for MNIST data base in Fig. 7. We can observe that recognition accuracy becomes constant after more than 6 bits of

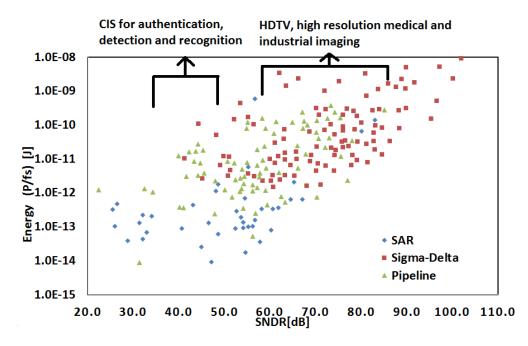

resolution. Further, it has been shown that for most of the machine learning applications moderate resolution (6-8bits) is sufficient[1][11]. Fig. 8 shows the Energy per conversion with respect to the Signal to Noise and Distortion ratio (SNDR) for state of the art SAR, Pipeline and  $\Sigma - \Delta$  ADCs. SNDR is related to effective number of bits (ENOB = SNDR - 1.76/6) [19]. From this plot we can observe that SAR ADC has best FOM (order of 10 - 1000 f J/conv) for moderate resolution (6-8 bits). Pipeline ADCs also have competitive FOM for moderate and high speed applications. Since most of the image sensors speed varies from 1MS/s to 10MS/s and we are interested in 8b of resolution for in-situ image processing applications, we propose a SAR-Pipeline ADC which achieves ultra-low power and high area efficiency.

Fig. 7. Classification accuracy vs Bit resolution for MNIST database

#### **3** SAR-Pipeline ADC Architecture for CS Measurements

For most of the low power applications SAR ADCs are used since they consume ultra-low energy per conversion(Fig. 8). However, for portable image front-end applications resolution more than 4-5 bits SAR ADC occupies huge area since

Fig. 8. Energy vs SNDR for state of the art reported SAR, Pipeline and  $\Sigma - \Delta$  ADCs[15]

the MSB capacitance grows as  $2^N$ . Since there will be many column parallel ADCs each will have capacitance of  $2^N$ . To alleviate this problem two-stage SAR Pipeline ADCs are proposed[20][21]. SAR-Pipeline uses two stage SAR-ADC and an amplifier which is used for amplifying residue generated by stage 1 SAR ADC (Fig. 9). Both the SAR ADC stages operates in parallel and each stage has to resolve lesser number of bits (lesser DAC settling time & capacitance (hence lesser area) as compared to traditional SAR). Therefore, SAR-Pipeline ADCs can operate at much higher speeds with high area efficiency [21]. One of the inherent advantage of SAR-Pipeline is residue voltage of Stag-1 SAR ADC is generated within its DAC after conversion phase. Hence this avoids extra DAC and clock phase to generate residue of Stag-1 unlike in traditional flash based Pipeline ADCs[21].

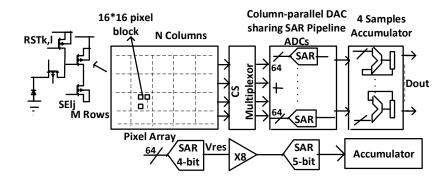

Fig. 9 illustrates the proposed ADC architecture. The design operates on a block size of 16 \* 16 (256 elements in pixel array). We propose SAR-Pipeline ADC consisting of 64-inputs Stage-1 SAR ADC resolving 4 bits ( with 1bit redundancy) and Stage-2 SAR ADC resolving 5 bits. We propose time-interleaved DAC sharing for Stage-1 SAR ADC which provides a linear measurement of 64-inputs in a single conversion cycle. We also share the amplifier (used for residue amplification) between 2 neighboring column parallel ADCs to save power. 64 inputs are simultaneously averaged and quantized using the SAR-Pipeline ADC. Post-conversion, 4 consecutive samples are averaged using a 10 bit accumulator

and shift register. This allows us to average 256 samples in 4 ADC conversion cycles. For m random measurements ADC takes m\*4 conversion cycles.

Fig. 9. Proposed CS front-end architecture for CIS

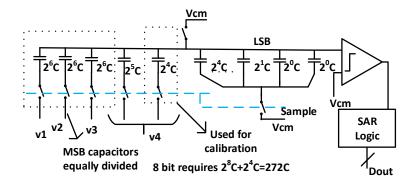

Fig. 10 shows a previously reported multi-input SAR ADC used for compressed sensing (with 8 bit resolution). It uses charge sharing. The MSB capacitor is equally divided among the inputs. Because of charge sharing the inputs will get averaged after the sampling cycle. [17] demonstrates a 4 input CS SAR ADC for wireless applications. This technique requires  $(2^8 + 2^4 = 272C)$  number of capacitors for an 8 bit ADC and measures 256 inputs (C is the unit capacitor). One of the main limitations of the proposed SAR ADC architecture for portable imaging application is the area occupied by the sampling capacitors[18]. Dividing the MSB capacitors to accommodate 256 inputs requires 256 switches. For portable applications limited supply  $\approx 1 - 1.3V$  provides high  $R_{ON}$ . This provides us the time constant  $(\tau_{conv})$  for conversion (min. sized capacitor of 50fF) of  $\approx 220$  nsecs (DAC settling time). This allows a maximum sampling frequency of 730KHz. Hence, for high speed cameras (with 30frames/sec) the proposed ADC architecture will not be able to meet latency requirements. Further, [17] uses calibration for capacitor mismatch, a requirement for more than 6-bits of resolution.

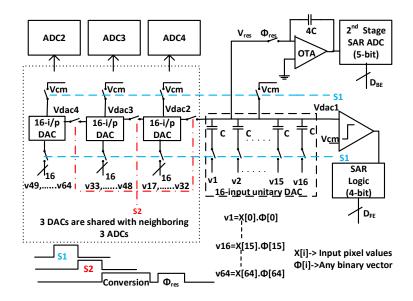

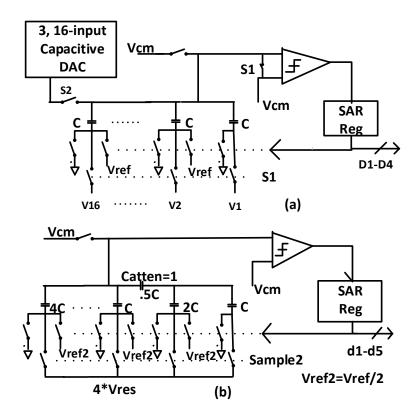

Fig. 11 is the proposed SAR-Pipeline with DAC sharing. We use 4 bit ADC as the first stage. Since 4-bit ADC has 16C capacitors, all the capacitors are divided into equal value of C and 16 inputs are applied. We have 3 instances of the same DAC which is used for accessing additional 48 inputs. Sampling is done in two phases. During sampling phase (S1) all 4 DAC's sample 16 inputs each. During second phase of sampling charge is redistributed between them. The averaged voltages across 4 DAC's during S1 phase given by Eq. 2.

Fig. 10. Reported multi-input SAR-ADC[17]

$$V_{dac1} = \frac{(v_1 + v_2 + \dots + v_{16})}{16}$$

$$\vdots$$

$$V_{dac4} = \frac{(v_{48} + v_2 + \dots + v_{64})}{16}$$

(2)

During the second sampling phase S2, averaging of  $V_{dac1}$  to  $V_{dac4}$  takes place. Therefore, the final voltage across DAC is given by Eq. 3.

$$V_{dacf} = \frac{(V_{dac1} + \dots + V_{dac4})}{4}$$

$$V_{dacf} = \frac{(v_1 + \dots + v_{64})}{64}$$

$$V_{dacf} = \frac{(X[0].\phi[0] + \dots + X[63].\phi[63])}{64}$$

(3)

We can observe form Eq. 3 that the final accumulated output represents the dot-product of the input pixel vector X with the sampling matrix,  $\phi$ .  $\phi$  can be random or programmed so that both random as well as structured compressed measurements can be obtained. As soon as S2 is done 3 DAC's are shared with neighboring column parallel ADC. Once the conversion in 4-bit SAR ADC is complete, we amplify the residue by 4x and pass it to a 5-bit fine ADC to resolve the LSBs. Ideally a gain of 16 is required for residue amplification. We use 1-bit digital redundancy in Stage 1 and half reference scaling for Stage 2 to reduce the gain requirement which helps to reduce the power in the high-gain op-amp [20].

Since all the capacitors we use are identical and of value C, calibration is not required (more details in section III). As 3 DAC's are shared with 4 ADC's, we need an additional capacitance of 12C. With 12C extra capacitance we can acquire linear measurements of 64 inputs in each conversion cycle. This DAC shared method significantly improves area efficiency and enables simultaneous

acquisition of multiple inputs. In this architecture, the conversion time-constant  $(\tau_{conv})$  is determined by the 4-bit ADC settling time even tough we are sampling 64-inputs. This makes the architecture suitable for high speed sensing with large number of inputs.

Fig. 11. Proposed multi-input DAC sharing SAR ADC

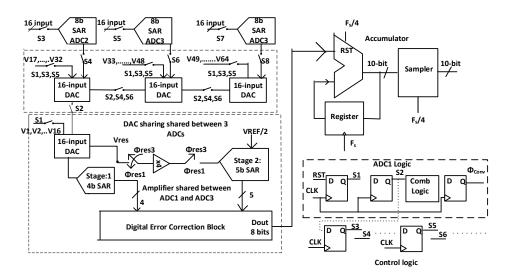

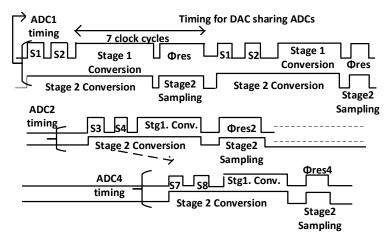

Fig. 12 shows how the sampling schemes are time-interleaved for the entire column parallel ADC architecture. Conversion cycle for ADC is 8 clock cycles. During this period we share 3 DACs with 3 of the neighboring ADCs. S3 to S8 are sampling phases of ADC2 to ADC4. S3 to S8 phase operates during conversion period of ADC1. Pipelining facilitates overlapping of Stage-1 and Stage-2 conversion phases. 1-bit redundancy is added in the first stage to accommodate capacitor mismatch and offsets of the comparator, amplifiers [20]. We also share residue amplifier between two neighboring ADCs to reduce the total power[21]. Accumulator (10 bit) used to average 4 consecutive ADC output samples. The accumulator is reset after every 4 sampling cycles  $(F_s)$ . The sampler operating at quarter sampling rate is used to capture the averaged output. The averaged output contains random measurement of 256 inputs. Fig. 12 also shows the control logic used for proposed CS front-end ADC architecture. Global reset (RST) is used generate S1, S2 and conversion phase for ADC1. S2 phase of ADC1 is used to trigger sampling phase for neighboring column parallel ADC. This process is continued for all 4 ADCs. Falling edge of S2 phase triggers the conversion phase of individual ADCs.

Fig. 12. Proposed SAR ADC with time-interleaved DAC sharing

Fig. 13. Timing for proposed SAR Pipeline Architecture

### 4 Design Components

In this section, the design details of the first and the second state of the ADC are discussed.

### 4.1 Stage 1 ADC and residue amplification

Fig. 14 shows the Stage 1 of the proposed SAR-Pipeline ADC. 64 inputs are acquired from S1 and S2. Residue is fed into an amplifier with gain of 4. Stage

1 of the ADC has 4 bit resolution with 1 bit digital redundancy. 1 bit redundancy is used to accommodate the residual offset of the comparator, op-amp and capacitor mismatch errors.

Fig. 14. Stage 1 and Stage 2 of the proposed ADC

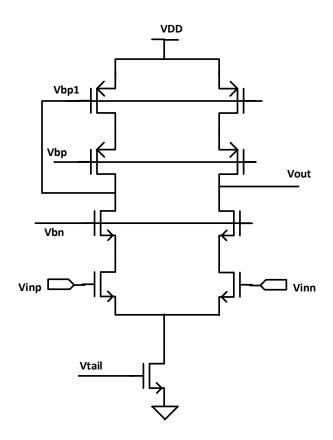

The Op-amp open loop gain  $(A_{OL})$ , unity gain frequency  $(f_u)$  and swing (Vp - p) target based on the inter-stage gain is given in Table. 1. The required values are derived as per gain error, gain bandwidth (GBW) requirement of the OTA to be within 1/2LSB of the ADC error[21]. The worst case values across process corners is mentioned in the Simulated values of the Table. We can observe that, simulated values across process corners for gain, bandwidth are by a factor of two larger than required values. Fig. 15 shows the telescopic cascode OTA used as interstate amplifier. It is well suited for two stage pipeline SAR since the swing requirement is low and it has high gain bandwidth efficiency.

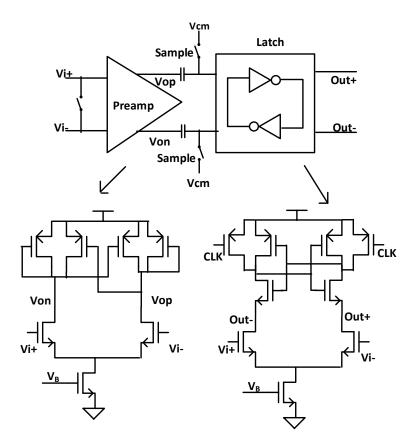

We use pre-amplifier with output offset compensation to limit the offset of Stage 1 SAR ADC. The residual offset  $(V_{os,res})$  is given by Eq. 4.

Fig. 15. Telescopic cascode OTA used as inter-stage amplifier

| $A_{OL} = f_u = Vp - p$           | 0                    |

|-----------------------------------|----------------------|

|                                   | Offset               |

| Required 42dB 42MHz 250mV         | $16.125 \mathrm{mV}$ |

| Simulated values 50dB 80MHz 300mV | $8 \mathrm{mV}$      |

Table 1. Design requirement for amplifier and 2nd Stage offset

$$V_{os,res} = \frac{V_{os,pre-amp}}{A_p} + \frac{V_{os,latch}}{A_p} \tag{4}$$

where  $V_{os,pre-amp}$  and  $V_{os,latch}$  are the pre-amplifier offset and latch offset respectively.  $A_p$  is the pre-amplifier gain. The  $3\sigma V_{os,pre-amp}$  and  $V_{os,latch}$  are 5mV and 30mV respectively. The gain amplifier features a cross coupled load which provides a high gain of 15. The residual offset is 2.33mV which is 0.25LSB of the sub-ADC. We use telescopic cascoded OTA in the proposed design for residue amplification. Telescopic cascoded OTA has high power efficiency for a given gain bandwidth (GBW)[19]. Because of half gain and half reference implementation of the ADC, the open loop gain of the OTA is reduced. The OTA achieves a swing of  $300mV_{p-p}$ .

#### 4.2 Stage 2 ADC

Fig. 16 shows the Stage 2 of the proposed SAR-Pipeline ADC. We use a split capacitor architecture to reduce the area and power for the second ADC. Since the non-linearity of this ADC will get divided by the gain of the amplifier, it can be neglected. For the comparator in stage 2 of the proposed ADC, a pre-amplifier with gain of 3 is used since the offset requirement from it is 15mV. Hence, Stage 2 of the proposed ADC doesn't require the output offset compensation. The total capacitance from the second ADC is 11C.

Fig. 16. 6- bit split cap SAR-ADC for Stage 2

#### 5 Analysis of Capacitor Mismatch

Systematic variations has no effect of capacitor matching since all the capacitance in Stage 1 SAR ADC are equal to C. The capacitance mismatch standard deviation for metal-insulator-metal (MiM) is given by Eq. 5.

$$\sigma_{\Delta C/C} = \frac{A_{\Delta C/C}}{\sqrt{WL}} \tag{5}$$

where  $A_{\Delta C/C}$  is process constant which is 1%. $\mu$  m for 0.13 $\mu$ m CMOS process[22]. W &/ L are width and length of the capacitor. The minimum size allowed in 0.13 $\mu$ m is  $5\mu m * 5\mu m$ . With minimum sized capacitor  $\sigma_{\Delta C/C}$  obtained will be 0.002.

As per [23] maximum allowable capacitor mismatch for a resolution of n is given by Eq. 6.

$$\frac{\Delta C}{C}_{max} = \frac{2^n}{2^{2n} - 2^n + 1} \tag{6}$$

For n=9,  $\Delta C/C_{max}$  reaches close to 0.002. This shows the residue generated by first ADC will fall within the range of 1/8LSB of error. Hence the proposed architecture is robust towards capacitor mismatch.

#### 6 Simulation Results

Performance of the proposed SAR-Pipelined ADC is verified through design and simulations in the  $0.13\mu$ m Mixed-Mode CMOS.

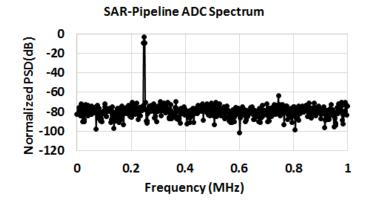

Fig. 17. Frequency spectrum of the proposed ADC (Fin=248.34kHz & Fs=2MHz)

Fig. 17 shows the normalized output frequency spectrum of the proposed ADC for input frequency  $(F_{in})$  of 248.34kHz at sampling rate (Fs) of 1MSPS. A 1024-point FFT shows SNDR of 49.5dB which is equivalent to an ENOB of 7.9.

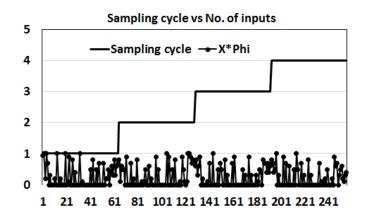

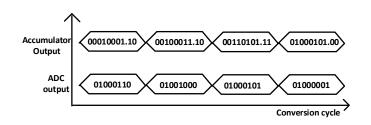

Fig. 18 shows the 64 inputs applied to ADC at each sampling cycle. Each 64 inputs corresponds to CS multiplexor output (Product of input vector with random number). Fig. 19 shows the ADC and accumulator outputs at each conversion cycles. For a particular case study, as shown in the figure, an ideal averaging without quantization results in a output of 270.11mV. The proposed ADC after accumulated 4 samples each provides an output of 269.53mV which is less than 1LSB of error.

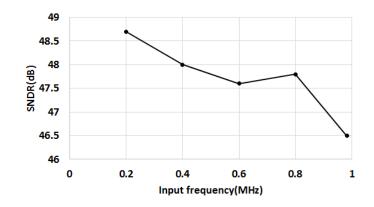

Fig. 20 shows the SNDR of the proposed ADC from input frequency range of 0.2MHz to to 0.98MHz. The ENOB at Nyquist frequency is 7.56. This ENOB achieves Walden FOM [19] of 85fJ/conv. step.

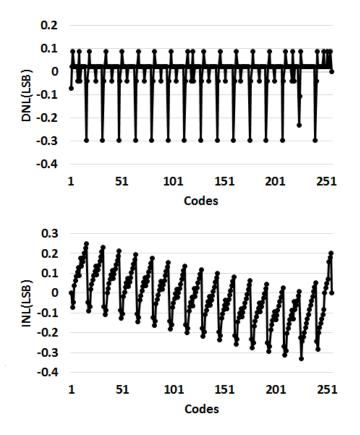

Fig. 21 shows the DNL and INL of the proposed ADC across 256 digital codes. The worst case DNL is within 0.4LSB. INL is within 1LSB across all digital codes.

Fig. 18. 64 inputs for ADC for every 1 sampling cycle

Fig. 19. Output of ADC and accumulator for 4 conversion cycle

Fig. 20. Simulation result of SNDR vs Input frequency at Fs=2MHz

Fig. 21. DNL and INL of the proposed ADC across 256 codes

## 7 Power Budget & Energy Efficiency

The power budget for the proposed ADC is given in Table .2. The power number is w.r.to patch size of 16\*16 and a compression ration (CR) of 16. Even though

the total power consumed from the supply is  $50\mu$ W, since the amplifier is shared between two ADC, the power for individual ADC's is  $31\mu$ W. The number of conversion cycles required for 16 \* 16 patch size with compression ratio of 16 is (16 \* 16 \* 16)/64 = 64.

The energy per patch is given by Eq. 7.

$$Energy_{Patch} = \frac{P * N_c}{F_s} \tag{7}$$

where, P is the power drawn by ADC for each conversion,  $N_c$  is the number of conversion cycles &  $F_s$  is the sampling frequency. The energy per patch for the proposed design is 0.9nJ.

| Block       | Power/      | Capacitance |

|-------------|-------------|-------------|

| SAR Stage1  | $7\mu W$    | 28C         |

| Amplifier   | $41 \mu W$  | 4C          |

| SAR Stage1  | $2.5 \mu W$ | 10C         |

| Accumulator | $0.5 \mu W$ | Nil         |

Table 2. Power and capacitance contribution from individual blocks

## 8 Comparison with Reported Works

Table. 3 shows the comparison of the proposed design with state of the art CS architecture. Proposed design is scalable and can handle a large number of inputs at the same time. Due to parallelism achieved by sharing DACs between columns parallel ADCs high energy efficiency per patch is achieved.

|                 | Oike [5]          | Guo [17]     | Chen [10]    | This work    |

|-----------------|-------------------|--------------|--------------|--------------|

| ADC type        | $\Sigma - \Delta$ | SAR          | SAR          | SAR-Pipeline |

| Technology      | $0.15 \mu m$      | $0.13 \mu m$ | $0.09 \mu m$ | $0.13 \mu m$ |

| Design          | Measured          | Simulated    | Measured     | Simulated    |

| No. of inputs   | 1                 | 4            | 1            | 64           |

| Sampling cycles | 256               | 1            | 256          | 4            |

| $F_s$           | 1MHz              | 1MHz         | 2kHz         | 2MHz         |

| Capacitance     | NA                | 272C         | 256C         | 40C          |

| Power           | NA                | $50\mu W$    | $5\mu W$     | $31\mu W$    |

| Energy/Patch    | NA                | 51 nJ        | 640nJ        | 0.9nJ        |

Table 3. Comparison with reported works

## 9 Conclusion

Multiple techniques are proposed to achieve high throughput in column parallel ADCs used for image sensors. Time interleaved sharing DAC technique reduces the number of measurement required by a factor of 4. Sharing the amplifier between neighboring column parallel ADCs reduces the power by 64%. The proposed architecture can be used for wearable devices with ultra-low power requirements. Our design and simulation results show 87 f J/conv. step with an average power of  $31 \mu$ W.

# Bibliography

[1] Choi, J., Sin, J., Kang, D., Park, D.: A  $45.5\mu$ W 15fps Always-On CMOS image sensor for Mobile and Wearable Devices IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers (2015) 114-117. [2] Deguchi, Jun., Tachibana, F., Morimoto, M., Chiba, M.: A 187.5Vrms-Read-Noise 51mW 1.4Mpixel CMOS Image Sensor with PMOSCAP Column CDS and 10b Self-Differential Offset-Cancelled Pipeline SAR-ADC IEEE ISSCC 2012, 494-496. [3] Park, J., Aoyama, S., Watanabe, T., Isobe, K., Kawahito, S.: A high-speed low-noise CMOS image sensor with 13-b column-parallel single-ended cyclic ADCs IEEE Trans. Electron Devices 2009, 2414-2422. [4] Watabe, T., Kitamura, K., Sawamoto, T., Kosugi, T., Akahori, T., Iida, T., Isobe, K., Watanabe, T. : "A 33 mpixel 120 fps cmos image sensor using 12 b column-parallel pipelined cyclic adcs IEEE ISSCC Dig. Tech. Papers 2012 (388-389). [5] Oike, Y., Gamal, A.: CMOS Image Sensor With Per-Column ADC and Programmable Compressed Sensing IEEE Journal of Solid State Circuits 2013. [6] Donoho, D. : Compressed sensing IEEE Trans. Inf. Theory 2006 (1289-1306). [7] Gruev, V., Cummings, R.: Implementation of Steerable Spatiotemporal Image Filters on the Focal Plane IEEE TCAS-II 2002. [8] Robucci, R.: Compressive sensing on a CMOS separable-transform image sensor Proc. IEEE 2010. [9] J. P. Slavinsky et. al, "The Compressive Multiplexer for Multi-Channel Compressive Sensing ," Proc. IEEE ICASSP, pp.3980 -3983 2011. [10] F. Chen, A. Chandrakasan and V. M. Stojanovic, "Design and Analysis of a Hardware-Efficient Compressed Sensing Architecture for Data Compression in Wireless Sensors," IEEE JSSC, vol. 47, no. 3, March. 2012. [11] Lee, E., Udell, M., Wong, S.: Factorization for Analog-to-Digital Matrix Multiplication Report, Standford University 2013. [12] Chae, Y.: A 2.1Mpixel 120 frame/s CMOS image sensor with column-parallel ADC architecture IEEE JSSC 2011 (236-247).

| f 1  |                                                                          |

|------|--------------------------------------------------------------------------|

| [13] | Lee, E., H.:                                                             |

|      | A 2.5GHz 7.7TOPS/W Switched-Capacitor Matrix Multiplier with Co-         |

|      | designed Local Memory in 40nm IEEE ISSCC 2016 (418-420).                 |

| [14] | Toyama, T:                                                               |

|      | A 17.7 Mpixel 120 fps CMOS image sensor with $34.8 \text{ Gb/s}$ readout |

|      | IEEE Int. Solid-State Circuits Conf. (ISSCC) 2011 (420-422).             |

| [15] | Murmann, B.:                                                             |

|      | ADC Performance Survey 1997-2015                                         |

|      | Available: http://web.stanford.edu/ murmann/adcsurvey.html.              |

| [16] | Zhang, J., Wang, Z., Verma, N.                                           |

|      | A matrix-multiplying ADC implementing a machine-learning classifier di-  |

|      | rectly with data conversion                                              |

|      | ISSCC 2015, (1-3).                                                       |

| [17] | Guo, W.:                                                                 |

|      | A Single SAR ADC Converting Multi-Channel Sparse Signals                 |

|      | Proc. IEEE ISCAS 2013.                                                   |

| [18] | Chen, D.:                                                                |

|      | A 64 fJ/step 9-bit SAR ADC Array With Forward Error Correction and       |

|      | Mixed-Signal CDS for CMOS Image Sensors                                  |

|      | IEEE TCASI 2014.                                                         |

| [19] | Gustavsson, M., Wikner, J., Tan, N.:                                     |

|      | CMOS Data converters for communication                                   |

|      | Kluwer Academic Publishers 2000.                                         |

| [20] | Lee, C., Flynn, M.:                                                      |

|      | A SAR-Assisted Two-Stage Pipeline ADC                                    |

|      | IEEE JSSC 2011.                                                          |

| [21] | Zhu, Y.:                                                                 |

|      | A 50-fJ 10-b 160-MS/s Pipelined-SAR ADC Decoupled Flip-Around            |

|      | MDAC and Self-Embedded Off. Cancel                                       |

|      | IEEE JSSC 2012.                                                          |

| [22] | Diaz, C., Tang, D., Sun, J.:                                             |

|      | CMOS technology for MS/RF SoC                                            |

|      | IEEE Trans. Electron Devices 2003 (81-84).                               |

| [23] | Lin,Z.:                                                                  |

|      | Modeling of capacitor array mismatch effect in embedded CMOS CR SAR      |

|      | ADC                                                                      |

|      | Proc. 6th Int. Conf. ASICs 2005 (979-982).                               |

|      |                                                                          |