# A Hierarchical Model to Manage Hardware Topology in MPI Applications

Brice Goglin, Emmanuel Jeannot, Farouk Mansouri, Guillaume Mercier

## ▶ To cite this version:

Brice Goglin, Emmanuel Jeannot, Farouk Mansouri, Guillaume Mercier. A Hierarchical Model to Manage Hardware Topology in MPI Applications. [Research Report] RR-9077, Inria Bordeaux Sud-Ouest; Bordeaux INP; LaBRI - Laboratoire Bordelais de Recherche en Informatique. 2018, pp.32. hal-01538002v4

# HAL Id: hal-01538002 https://inria.hal.science/hal-01538002v4

Submitted on 6 Mar 2018 (v4), last revised 22 May 2018 (v6)

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Hierarchical Model to Manage Hardware Topology in MPI Applications

Brice Goglin Emmanuel Jeannot Farouk Mansouri Guillaume Mercier

RESEARCH REPORT

N° 9077

June 2017

Project-Team TADaaM

# A Hierarchical Model to Manage Hardware Topology in MPI Applications

Brice Goglin\* Emmanuel Jeannot<sup>†</sup> Farouk Mansouri<sup>‡</sup> Guillaume Mercier<sup>§</sup>

Project-Team TADaaM

Research Report n° 9077 — version 3 — initial version June 2017 — revised version March 2018 — 32 pages

Abstract: The MPI standard is a major contribution in the landscape of parallel programming. Since its inception in the mid 90s it has ensured portability and performance for parallel applications on a wide spectrum of machines and architectures. With the advent of multicore machines, understanding and taking into account the underlying physical topology and memory hierarchy have become of paramount importance. On the other hand, providing abstract mechanisms to manipulate the hardware topology is also fundamental. The MPI standard in its current state, however, and despite recent evolutions is still unable to offer mechanisms to achieve this. In this paper, we detail several additions to the standard for building new MPI communicators corresponding to hardware hierarchy levels. It provides the user with tools to address hardware topology and locality issues while improving application performance.

**Key-words:** Hierarchy, Hardware Topology, Message Passing

RESEARCH CENTRE BORDEAUX – SUD-OUEST

200 avenue de la Vieille Tour 33405 Talence Cedex

<sup>\*</sup> Inria/LaBRI

<sup>†</sup> Inria/LaBRI

<sup>&</sup>lt;sup>‡</sup> Inria/LaBRI

<sup>§</sup> Bordeaux INP/LaBRI

# Un modèle hiérarchique pour la gestion de la topologie dans les applications MPI

Résumé: Le standard MPI est une contribution importante dans le domaine de la programmation parallèle. Il est destiné à l'écriture d'applications parallèles pour un large éventail d'architectures parallèles. L'arrivée des machines multicœur implique une compréhension plus fine de la topologie matérielle sous-jacente, notamment en ce qui concerne les hiérarchies mémoire et réseau. Or, dans son statut actuel, MPI ne permet pas de prendre ces aspects en compte. Nous détaillons dans cet article des modifications à MPI pour permettre la prise en compte de ces aspects afin d'améliorer les performances applicatives.

Mots-clés: Hiérarchie, Topologie Matérielle, Passage de Messages

## 1 Introduction

Parallelizing or writing from scratch a parallel application is a very challenging task and this challenge has become even more important due to the current trend in processors design and supercomputers architecture. Indeed, the hardware that the programmer has to tackle becomes more and more hierarchically organized. For instance, CPUs now feature various levels of memories that have different properties in terms of size, performance and even nature. As a consequence, a parallel application performance is likely to be impacted by the communication occurring between processes and by the way they access data. Thus, if a process accesses some data located in a memory bank physically far from the core it currently executes on, a penalty shall occur (NUMA effect). Also, if two processes share a cache level, they will communicate one with the other more efficiently. This is known as the data locality issue. Indeed, a recent survey on MPI usage for future exascale systems [?] outlines that a significant fraction of applications (18 out of 48) exhibit sensitivity to the hardware topology.

In order to better exploit the underlying hardware, applications need to take this locality phenomena into account. On one hand, they need to get a better grasp of the underlying physical architecture they are running on. The current success of hwloc [2] demonstrates the need for such a tool and the information it allows to gather. This knowledge may offer the possibility of optimize the code, to better exploit the memory hierarchy or the network topology as well as a global and comprehensive view of the hardware (a continuum of hierarchies between the network and the memory). However, on the other hand, it is required, for performance portability reasons and because domain scientists and application programmers are not hardware topology specialists, that the proposed scheme to take locality into account is done through high-level, portable abstractions.

Having efficient yet abstract mechanisms to deal with this issue is a difficult task. To this end, a relevant programming model (along with tools and libraries that implement it) can be of valuable help. The most obvious and natural choice would be to first look at what current parallel programming standards and libraries offer in this area.

In the case of the Message Passing Interface (MPI) [15], some mechanisms are already available that could make it possible for an application to exploit the hardware hierarchy to improve interprocess communication and locality. For instance, in the case of virtual topology management routines, such as MPI\_Dist\_graph\_create, the reorder argument can be used to create a topology where processes are reorganized according to the underlying physical topology of the target architecture.

However, there are several issues with this approach: first, this argument *might* be used in this fashion, but that is not necessarily the case, which means that the expected behaviour is totally implementation-dependent (and thus not standard) hence likely to change from one implementation to the other or even worse from one implementation version to the other. An application cannot rely on a particular MPI implementation version to be able to use the specific features it needs. Then, in absence of dedicated and relevant mechanisms directly within the standard, an application is forced to use some side-effects of already available features, which constitutes an issue in terms of both interface expressiveness and usability.

In this paper, we present abstraction mechanisms that can help programmers to structure their applications based on physical topology criteria. Such structure can then be used to improve data locality or communication performance by taking into account information that would be otherwise unavailable to the underlying MPI implementation. We also present the implementation of this abstraction and mechanisms in the context of the MPI standard.

This paper is organized as follows: the current status of the MPI interface with regard to hardware topology management is discussed in Section 2 and our proposal is detailed in Section

3. Its implementation is described in Section 4 and examples of uses are detailed in Section 5. Section 6 describes the target applications of this work and experimental results are analyzed in Section 7, while Section 8 concludes this paper and give potential future directions.

## 2 Hardware topology management and the MPI Standard

In this section, we shall examine the current possibilities offered by the MPI standard to deal with the issue of hardware topology management in parallel applications. One key-characteristic of the MPI standard is its hardware-agnosticism. Indeed, it makes no assumptions about the hardware on which the application is going to be deployed and run. This behaviour ensures the portability of parallel programs using MPI. It is to be noted also that despite this independence from any hardware considerations in its programming model, the MPI standard and programming model does not prevent from accessing the hardware topology directly from an application.

## 2.1 Interactions with external tools

One way to tackle this issue is precisely to use an altogether different tool or interface, fully external to MPI. That is, one current practice is to deal with tools representing the hardware topology such as hwloc [2], LibNuma [12], or Pthread sched [16]. These libraries could give a relevant representation of the hardware structure and components. However, they are rather low-level tools and need a good knowledge of the underlying hardware to be used correctly and efficiently. In addition, this practice increases the complexity of developing and supporting codes. Last, as these tools or interfaces are not standard, portability is not guaranteed.

## 2.2 Current status in the MPI standard and its implementations

The MPI library even offers some means to better understand the nature of the physical architecture in order to exploit it to its full potential. For instance, the extension of Remote Memory Operations with Shared Memory operations in the standard has allowed programmers to structure their applications to take into account the fact that processes are located on the same machine. This can be seen as an alternative to the use of multithreading when memory consumption is at stake [20, Chapter 16]. In this particular case, the MPI standard acknowledges that some physical resource (e.g. memory) is shareable between processes and offers the tools to actually access this resource.

However, despite the presence of some mechanisms in MPI to better understand and use the hardware, they address the issue only partially. Some MPI implementations offer mechanisms but since they are implementation-dependent they are typically non-standard. Portability is therefore not guaranteed. The bottom line is: an application should not (or cannot) rely on a specific implementation nor on a specific version of an implementation (which is even worse). On the other hand, improving performances and scalability of applications is more efficient when locality is exposed during their design steps rather than only relying on MPI implementation optimizations. Thus, the MPI programming model as specified by the standard needs to offer highlevel abstractions to take into consideration architecture topology at an early stage and before calling implementations features. The following paragraphs describe some of these mechanisms and their shortcomings.

#### 2.2.1 Shared Memory constructs

MPI\_Comm\_split\_type can accept MPI\_COMM\_TYPE\_SHARED as a value for its split\_type ar-

gument. The outcome is a communicator that encompasses all processes in the original communicator that can create a shared memory region <sup>1</sup> By using the communicators produced by this function, it is possible to structure an application in order to take into account the fact that memory is shared: for instance direct memory accesses are possible instead of relying on message-passing exchanges handled by the MPI library. The overheads of the library in case of shared-memory are eliminated. However, the various levels of cache, a major part of the hardware hierarchy, are left unexploited. As explained previously, this memory hierarchy is becoming more and more complex and performance gains are expected from a relevant exploitation of it.

#### 2.2.2 Process topologies and reordering

The various process topologies available in MPI can help to structure an application but they are virtual topologies and quoting the standard itself: "The virtual topology can be exploited by the system in the assignment of processes to physical processor, if this helps to improve the communication performance on a given machine. How this mapping is done, however, is outside the scope of MPI." Some implementations use the reorder parameter of some functions (e.g. MPI\_Dist\_graph\_create [8], etc.) and take the opportunity to retrieve hardware information and make use of it [14, 19, 9]. Some others tailor the topology routine of MPI to a specific hardware [5, 10]. This, of course, falls into the non-standard category as it is implementation-dependent and is a side effect of the function. It is not the primary goal of it and the fact that the underlying hardware is efficiently exploited can be seen as a bonus.

#### 2.2.3 MPI Sessions

MPI sessions are a new concept that is currently being discussed by the MPI Forum. In its current state, the standard only allows to call MPI\_Init and MPI\_Finalize a single time in an application. This can raise some issues when multiple libraries that internally rely on MPI are used concurrently. Sessions can be seen as a lightweight construct, even lighter than groups. A session encompasses MPI processes and some information can be attached to it, for instance about the application or the hardware. In this case, the sharing of hardware resources could be exploited by the application with several different MPI sessions.

## 2.2.4 Process Managers and process mapping

One last critical point regards process managers. They can also be of help when it comes to exploit the underlying hardware. Indeed, through their process mapping and binding options, they can allow the user to finely control the way the various MPI application processes are dispatched and executed [7]. Thanks to an adequate placement policy enforced by both these mapping and binding parameters, it is possible to take into account the physical topology and reduce the communication costs for instance [13, 1]. This is also used to improve collective communication performance [22], Unfortunately, these options are totally non-standard and can even change from one version of a process manager to the other.

Even though we consider this specific point to be outside the scope of this paper, it is strongly tied to the issue of hardware topology management in MPI applications. Indeed, in the absence of a (relevant) mapping/binding of processes, the performance improvements of taking into account the underlying hardware topology are not expected to be as high as if an efficient policy is enforced. For the rest of this paper, we make the assumption that the user knows the consequences of adopting a relevant mapping/binding process policy and chooses one accordingly.

<sup>1</sup> It is obviously the case when they are located on the same machine, but could also be the case if the processes are on different machines linked by a network  $\hat{a}$  la SCI.

## 3 Proposed Extensions to the MPI standard

As exposed in the previous section, there are currently no means in the MPI standard to portably take into account the hardware topology at the application level. We think that it is important/necessary to offer high-level abstractions helping programmers to take care of locality and communication optimizations when they design their applications. This way we anticipate and facilitate an implementation work that optimizes communications according to the target architecture. Therefore, we propose to extend the MPI standard and detail in the rest of this section the relevant mechanisms and features needed to achieve these objectives.

#### 3.1 Guidelines

Since its first version in 1994, the MPI standard has grown steadily in terms of number of available routines and functionalities. We therefore advocate for a minimal amount of changes and prefer to leverage existing mechanisms. We prefer not introducing new functions unless it is unavoidable and rather expand existing mechanisms. MPI is about communications and how they are managed. In this regard, exploiting the underlying topology boils down to be able to organize the various MPI application processes in a way that is both topologically-wise and performance-wise sensible. The same idea has already been used in the case of reordering: the processes that communicate a lot should be bound on two cores physically close to each other. Consequently, the sharing of caches is likely to decrease communication times and improve overall application performance.

The key idea is therefore to group processes into entities where a specific kind of resource is shared by all groups<sup>2</sup> members (i.e. processes). MPI features a concept/construct that perfectly matches our needs: the *communicator*. As a consequence, we propose to make hardware topology information and structure available at the application level through a hierarchy of communicators. We want to help an application developer and guide him/her to build the most relevant communicator (hardware) topologically-wise, without any deep knowledge of the underlying architecture and regardless of the way the application processes are mapped and/or bound on the machine.

In this hierarchy, each communicator corresponds to a specific resource that is shared by all the processes belonging to it. For instance, if a process shares a L2 cache and a L3 cache with other processes, it will be part of the communicator encompassing all processes sharing the same L2 and part of the communicator encompassing all the processes sharing this level 3 cache. Creating communicators also allows the use of collective communications among processes that share a resource. Collective communication operations are a major feature of MPI. It gives the programmer some ability to structure his/her application and encourages him/her to improve the locality factor of the communications.

## 3.2 Communicators creation

There exists a couple of functions in the MPI standard that create communicators, and one in particular if of interest for our purpose: MPI\_Comm\_split. Since the idea supporting our proposal is to create communicators based on the sharing of common hardware resources, splitting some input communicator (MPI\_COMM\_WORLD being obviously a relevant but not a mandatory candidate) is a natural fit for the goal we want to achieve: indeed the information about the sharing of the resource can be conveyed by the color argument. However, the outcome is not likely to be the one expected: let us take for example the case of processes mapped onto different

<sup>&</sup>lt;sup>2</sup>" group" has to be taken in the generic sense, we do not deal with the concept of MPI groups here.

physical nodes (for the sake of simplicity, each core of each node executes its own process). Let us then assume that each node features several L3 caches. If we want to create as many communicators as the number of L3 caches in our configuration, we cannot provide a single color value, otherwise, *all* processes would end up belonging to the same communicator. Ideally, we would like to provide the same color value, but this value has to carry a different meaning in different processes.

## 3.2.1 MPI\_Comm\_split\_type extension

Fortunately, this is exactly the behaviour of MPI\_Comm\_split\_type. Indeed, this function partitions the group associated with the input communicator into disjoint subgroups, based on the type specified by the value assigned to the split\_type parameter. A single value is currently defined in MPI 3.1: MPI\_COMM\_TYPE\_SHARED. When this value is used, the input communicator is split into communicators, where each new communicator represents a shared-memory domain. That is, two processes belonging to the same subcommunicator are able to create a mutually accessible shared-memory region. Obviously, there is no overlap between these new communicators. This function, along with the particular MPI\_COMM\_TYPE\_SHARED value for the split\_type parameter, already allows the user to better understand the way the processes are mapped onto the underlying hardware. It also gives the opportunity to take advantage of it since a different programming model (MPI-3 Shared Memory style) can be used in each new communicator and classical Message Passing between them. The MPI standard stipulates that implementations may define their own values for the split\_type parameter, in order to enforce specific behaviours. The flexibility granted by this approach is counterbalanced by its sheer lack of portability. As a consequence, we propose to enrich the set of possible values for the split\_type argument by adding a new one (MPI\_COMM\_TYPE\_PHYSICAL\_TOPOLOGY for instance<sup>3</sup>). The info argument can be used to pass hints to the implementation about the way the split operation should be done.

### 3.2.2 Proprieties of the hierarchical communicators

A call to MPI\_Comm\_split\_type with this new value shall yield a communicator corresponding to the highest possible level in the hierarchy tree representing the hardware topology. This newly produced communicator can then be used as an input argument in subsequent calls to MPI\_Comm\_split\_type to produce other "child" subcommunicators that correspond to deeper levels (complete examples are detailed in Section 5). Also, the newly produced communicators should retain the following proprieties:

- The last valid communicator produced in this fashion may be identical to MPI\_COMM\_SELF, but not necessarily.

- Each recursively created new communicator should be a strict subset of its parent (input) communicator. That is, a call to

MPI\_Comm\_compare(oldcomm,newcomm)

must return MPI\_UNEQUAL. This propriety ensures that no unnecessary new communicators are created in case of redundancies of levels in the hardware topology. For instance, if a L3 cache and a L2 cache are shared between all processes, there is no need to create a communicator for both resources.

• If no valid communicator is to be created, MPI\_COMM\_NULL should (obviously) be returned.

<sup>&</sup>lt;sup>3</sup>Or any suitable and meaningful name.

These communicators calls will form a kind of hierarchy, mimicking the hardware one, as all new communicators are encompassed (so to speak) in their parent communicator. That is, if a process belongs to the communicator corresponding to the n-th level of the hierarchy, it also belongs to all communicators corresponding to levels 0 to n-1. It is important to note that our abstraction does not make any distinction between the network hierarchy and the nodes internal memory hierarchy. We provide means to organize an application according to the *structure* of the hardware, not its *nature*.

#### 3.2.3 Creation of Roots Communicators

One other useful addition is the ability to create at the same time at each level of the hierarchy yet another communicator which includes all root processes of a hierarchical communicator. This forms another kind of hierarchy of its own and could ease the communication between all the levels of the hierarchy. This function could have the following prototype:

With:

IN oldcomm: communicator (handle)

IN info:info argument (handle)

OUT newcomm: communicator (handle)

OUT rootscomm: communicator (handle)

newcomm is the same communicator created by a call to MPI\_Comm\_split\_type with MPI\_COMM\_TYPE\_PHYSICAL\_TOPOLOGY as value for the split\_type parameter. rootscomm is the communicator containing all processes that are roots in newcomm. A valid roots communicator can only be returned if the root process of oldcomm calls this function. MPI\_COMM\_NULL is otherwise returned by non-root processes. This function prototype shows that both key and color/split\_type parameters are missing, as regularly found in others MPI split routines. In the case of the color/split\_type parameter, since this routine is called to produce a hierarchy of hardware-topologically meaningful communicators, it is therefore unneeded. As for the key parameter, we chose in our design to retain the rank of the calling process in the newly produced communicator. However, should this be considered not flexible enough, the interface could be modified easily, as this point is not influenced whatsoever by the hypotheses formulated on the newly created communicators.

#### 3.2.4 Interaction with process mapping/binding policies

A special care should be taken regarding the current binding of process ranks. Indeed, the deepest level that shall be returned should correspond to the current process binding (e.g if a rank is bound to a L3 cache, no information below this level should be returned since it may use different L2 caches below when moving inside the binding). Any attempt to do so should return MPI\_COMM\_NULL. Moreover, unbound processes may move across an entire shared-memory machine and therefore cannot belong to a communicator split deeper than the "Machine" level: in such a case, the returned communicator shall be the same as the one returned by a call to MPI\_Comm\_split\_type with the MPI\_COMM\_TYPE\_SHARED value for the split\_type parameter.

## 3.3 Communicators characteristics query

The main aspect of our proposal deals with hierarchical communicators creation. However, we need to introduce other functions in order to make the use of these communicators more practical to the application developer. So far, with the proposed abstraction, users are able to leverage the structure of their hardware. However, more information might be needed, for instance in case of data distribution between the various communicators created at a certain level in the hierarchy.

#### 3.3.1 Getting information for a hierarchical level

A process is able to retrieve some information about a specific communicator it belongs to with a call to the following function:

With:

IN comm: communicator (handle)

OUT num\_comms: number of siblings communicators (integer)

OUT index: communicator index (integer)

OUT type: type of communicator (string)

- num\_comms is the number of communicators at the same level and that share the same parent communicator.

- index is a kind of rank for each communicator which should be contiguously numbered and starting from 0. It is the rank of the communicator among all communicators created by its parent communicator.

- type is a string giving information about the kind of resource that the communicator represents. It should be unambiguous, like L2\_Cache, L3\_Cache or NumaNode.

All this information should be cached by the communicator in an info object attached to it containing a set of (key,value) pairs properly defined when the communicator comm is created with a call to MPI\_Comm\_split\_type or MPI\_Comm\_hsplit\_with\_roots. This info object creation would require the use of the MPI\_Comm\_set\_info and MPI\_Comm\_get\_info functions.

#### 3.3.2 Getting the minimal level

Another helpful feature would be the ability for a programmer to know the name (type) of the *lowest level* in the hardware hierarchy that is shared by some processes. To this end, we propose to add the following function:

With:

IN comm: communicator (handle)

IN nranks: number of MPI processes (integer)

IN ranks: list of MPI process ranks (array)

OUT type: type of the resource (string)

This function returns the name of the *lowest* level in the hierarchy shared by all the MPI processes which ranks in the communicator comm are listed in the rank array. If the calling process rank is not among the ranks listed in the array passed as an argument, the type returned should be "Unknown" or "Invalid".

### 3.4 Discussion

In this section, we discuss the design choices, advantages and potential drawbacks of our approach. We propose an abstraction based on existing MPI objects (the communicators), hierarchically modelling the hardware topology in order to improve performance and scalability. Communicators are often used in MPI applications and a well-understood concept to boot. A large majority of application developers are familiar with it (beyond MPI\_COMM\_WORLD). Therefore, using our proposal would require little effort, conceptually speaking. The communicators created do not feature a predetermined name, taken after the underlying resource it is supposed to represent. This ensures that there will be no need to make any change nor modifications in the future in case new levels in the hardware hierarchy should appear. This also justifies why we do not specify a maximal depth for the hierarchy. By creating "recursively" new communicators, the user is able to get all needed objects until the bottom is reached and no new communicator can be produced. The user can of course choose the desirable depth by querying the name/type of the communicator created and deciding to go further or not. This choice also explains why we do not rely on several predetermined values for the split\_type argument 4 (e.g. one value corresponding to a specific hierarchy level) because architectural changes in hardware would require modifications to the standard.

It is important to note that with this proposal, it becomes possible to create a hierarchy of communicators corresponding to the various hardware levels, but not the hierarchy. Indeed, it is not mandatory that this hierarchy has to be exhaustive or complete. As a consequence, a partial implementation that cannot or do not want to expose some levels is totally acceptable. However, the various communicators must comply to the characteristics and proprieties described in Section 3.2.2. The only expected consequence of this lack of levels provided to the user is in terms of performance, as the users will not be able to optimize their code to the full extent of the available hardware.

Currently, our design is based on a "recursive" call to MPI\_Comm\_split\_type in order to create the hierarchy. However, an alternate solution would be to introduce a function that create all communicators at once, returning an array for instance as well as its size (i.e. the hierarchy depth). Such a function is more simple to use, but compels the user to create all the levels, even undesired ones. The chosen design allows for more control at the cost of some ease of use.

One drawback of our approach is the fact that it targets architectures which are hierarchically organized. It is the case for most machines, but there are some exceptions that our model does not currently address. And the same issue arises for network topologies that are not hierarchical, such as torus for instance. In such a case, should the split be made on just a particular dimension

<sup>&</sup>lt;sup>4</sup>As implemented in Open MPI with the OMPI\_COMM\_TYPE\_\* values for instance.

of the torus? The info argument could be used to pass this information. But if some form of hierarchy can be extracted from the network topology, we can exploit it with our mechanism.

Currently, the interface proposed features one new value for the <code>split\_type</code> argument of the <code>MPI\_Comm\_split\_type</code> function and three new routines. But one open question is whether we should offer more elements. Indeed, it could be interesting to create several hierarchies of communicators, based on different criteria with different <code>split\_type</code> values. For instance, making a distinction between the network topology and the nodes internal topology could be a relevant idea. The info argument in <code>MPI\_Comm\_split\_type</code> could also be used to split a communicator directly at a desired level, without creating the whole hierarchy.

## 4 Implementation Details

Our proposal is implemented and available as a prototype library called *libhsplit* (for *hierarchi-cal split*). We chose the external library route for fast prototyping reasons but our goal is to eventually integrate this work within an MPI implementation.

Our proposal is technology or software independent and implementable at the sole condition that hardware informations can be retrieved from the underlying target machine. In our case, we chose to leverage two different pieces of software: hwloc [2] and its extension, netloc [4].

## 4.1 An hwloc-based implementation

In this section, we describe the functions of the library that implements the proposal exposed previously. The first version of this library focuses only on the nodes and their internal memory hierarchy and leaves unaddressed the network hierarchy. That is, this implementation considers a flat network topology, meaning that all nodes of a cluster are connected to the same switch. The reason of such a choice stems from the software used to retrieve hardware information. Indeed, we used hwloc [2] to gather as much information as possible. hwloc is a tool that provides the user with an interface allowing to retrieve hardware details in the most portable fashion possible. hwloc is widely available and has already been integrated in several MPI implementations to manage hardware details. It is the case of both Open MPI and MPICH, for instance. As a consequence, this version of our library partially captures the hardware hierarchy. However, as discussed previously in Section 3.4, this is an acceptable outcome/behaviour. Moreover, this implementation complies totally with the communicators proprieties listed in Section 3.2.2.

## 4.1.1 MPI\_Comm\_split\_type implementation

First, we detail the implementation of the routine at the core of our proposal, that is, MPI\_Comm\_split\_type. We propose to introduce a new value for the split\_type parameter of this function. Our implementation relies on the more generic MPI\_Comm\_split operation that takes as input a color parameter that allows to split the input communicator into k non-overlapping subcommunicators<sup>5</sup>. Using this operation in our case is relevant since the subcommunicators we propose to build are non-overlapping by nature. As a consequence, the issue then boils down to determining the right color that shall be used by the regular split operation. Algorithm 1 details how this can be determined with hwloc:

• The first major thing is to determine the hwloc object in the hierarchy that encompasses all the processes members of the communicator that we want to split. hwloc conveniently

<sup>&</sup>lt;sup>5</sup> If no color is specified (MPI\_UNDEFINED), then no valid communicator (MPI\_COMM\_NULL) is created.

Algorithm 1: Split Color Algorithm: cpusets refer to the way hwloc describes object location (set of hardware threads included in the object) or process binding (set of hardware threads where the process may run).

proposes a routine returning the deepest object in the hierarchy in case of levels redundancy (line 2).

- Once this object has been obtained, we are able to search through its hwloc children objects in order to find to which specific one the calling process is bound (line 3). A match is found when the binding of the calling process is included in the considered child (line 4). These child objects are logically numbered in sequence by hwloc, therefore the right color is the matching child's index (line 5). If no candidate is found, the color is left to the MPI\_UNDEFINED value which will yield an invalid (null) communicator in MPI\_Comm\_split.

- A key needs to be determined for the split. We decided to use the rank of the calling process in the input communicator (line 7).

- The split operation is effectively performed, with both the color and key parameters set with their values (line 8).

If the resulting communicator is valid, we then set three (key,value) pairs that can later be queried by a call to MPI\_Comm\_get\_hlevel\_info (see below). These three keys are the following:

- MPI\_COMM\_HLEVEL\_TYPE: the value corresponding to this key is a name for the communicator that can help the programmers to better understand the resource they are using through the communicator. See section 3.3.1 for examples of possible string values. In our implementation, the names are provided directly by hwloc by the hwloc\_obj\_type\_snprintf routine. By doing so, portability is enforced to some degree, or at least across MPI implementations that feature hwloc (which is the case of Open MPI, MPICH and MVAPICH for instance).

- MPI\_COMM\_HLEVEL\_NUM: the value corresponding to this key is the total number of subcommunicators created at a specific level in the hierarchy.

- MPI\_COMM\_HLEVEL\_RANK: the value corresponding to this key the "rank" of a subcommunicator among all created subcommunicators at a specific level of the hierarchy.

The last two (key,value) pairs can be used by programmer in case of data distribution among the various parts of the hardware architecture. These (key,value) pairs are then stored in the resulting new communicator with the MPI\_Comm\_set\_info function. It is important to note that the keys names are not exposed to the programmer at any time. Indeed, since a query routine is provided, there is no need to expose this internal part of the library.

#### 4.1.2 MPI\_Comm\_hsplit\_with\_roots implementation

The next function we describe is the one that returns both a subcommunicator and the communicator whose group contains all the root processes of all created subcommunicators during this step. It is possible to create this roots communicator with the current functions available in MPI. However, from a performance standpoint, an hwloc-based implementation (and thus a new function in the standard) is more efficient as hwloc gives use information that can directly use to this purpose. It also removes the burden of implementing it by the user. That is why we proposed a single function that creates both communicators at the same time. Algorithm 2 describes how this can be performed with hwloc:

Algorithm 2: Split Color Algorithm: variant with roots communicator creation

```

\texttt{1} \ \texttt{color} \leftarrow \texttt{MPI\_UNDEFINED}

2 obj = get_ancestor(comm); // Get the deepest obj which contains all

processes binding

3 foreach idx\leftarrow 0 .. (obj->arity) do // Find the right color

ext{if calling\_process->cpuset} \subseteq 	ext{obj->children[idx]->cpuset then}

\mathtt{color} \leftarrow \mathtt{idx}

5

6

break

7 MPI_Comm_rank(comm,&rank)

8 MPI_Comm_split(comm,color,rank,newcomm)

9 \text{ color} \leftarrow \texttt{MPI\_UNDEFINED}

10 MPI_Comm_rank(newcomm,&newrank)

11 if newrank = 0 then

| color ← (obj->logical_index)

13 MPI_Comm_split(comm,color,rank,rootscomm)

```

- The first part is similar to the algorithm explained in the previous paragraph: the subcommunicator is produced (line 1 to 8).

- In order to produce the root communicator, we need once again to find the right color to use in a second MPI\_Comm\_split operation. Only the roots of the subcommunicators will be part of the resulting communicators. Such roots are chosen as processes with rank 0 in the subcommunicators. This is a sensible choice because if a communicator is valid, i.e. not MPI\_COMM\_NULL, it shall contain at least one process and processes are numbered in sequence, starting from 0 (lines 10 and 11).

- If the calling process is determined to be a root, it will be part of the split and has to provide MPI\_Comm\_split with a color (as previously, the key used shall be its rank in the input communicator and not the subcommunicator). This color is chosen as the hwloc logical index of the ancestor object (line 12). Indeed, choosing a valid color value for processes with 0 rank and an invalid color otherwise will not create the intended hierarchy of roots communicators. We have to make a distinction between root processes sharing the previous level and this information is conveyed by the logical index of the ancestor object.

- The split operation is performed with the right parameters (line 13).

All the (key,value) pairs detailed in the previous section are also set in this function.

#### 4.1.3 MPI\_Comm\_get\_hlevel\_info implementation

The implementation of this function is rather straightforward, as its goal is to gather the information available for a certain hierarchical level (a communicator) and pass it to the application developer in a tractable form. Since all information is stored in an MPI info object, a call to MPI\_Comm\_get\_info is sufficient to retrieve the needed object. Since the various keys used (i.e. MPI\_COMM\_HLEVEL\_NUM, MPI\_COMM\_HLEVEL\_RANK and MPI\_COMM\_HLEVEL\_TYPE) are internal to the library, we can then query for their value and passing it to the user through the arguments of the function.

We decided to not use MPI\_Comm\_set\_name and MPI\_Comm\_get\_name to store/retrieve the value of the MPI\_COMM\_HLEVEL\_TYPE key since it is not possible to store multiple names of a more complete description of the hierarchical level the communicator represents. Also, this communicator could possibly bear a name that we do not want to replace.

#### 4.1.4 MPI\_Comm\_get\_min\_hlevel implementation

In our current implementation, most of the strings returned by this function are generated by hwloc. However, some cases are not covered by hwloc and as a consequence, we introduced our proper strings:

- if the calling process is not part of the communicator queried upon, "Unknown" is returned

- if some processes in the list and the calling process do not belong to the same node, "System

- Cluster" is returned

- if all processes in the list are local (i.e. belong to the same node), the hwloc name corresponding to the level they share is returned

## 4.2 Network Support Extension with netloc

The implementation described in the previous sections only addresses the node internal hierarchy, such as the memory hierarchy. However, even though this is an acceptable solution as users can exploit some (but not all) hierarchy levels, a more comprehensive solution is preferable. Indeed, the various switches in a network often form a hierarchy of their own. Allowing the users to know about it and leverage the hardware characteristics and organization of the underlying network is a compelling idea.

Our model and abstraction is able to give the user some means to optimize their code according to the *structure* of the hardware and not its *nature*. Practically, this means that a hierarchy of switches and a memory hierarchy are not seen nor treated as different things: they constitute a continuum. The issue is then to be able to retrieve the needed information about these various levels in the network, like hwloc is able to gather information about the memory hierarchy inside a node.

Such a tool actually exists: netloc [4]. netloc is a hwloc extension that specifically addresses network hierarchies and topologies. In order to create the communicators corresponding to the switches levels, we use the following experimental netloc routine:

```

int netloc_get_network_coords(int *nlevels,int *dims,int *coords)

```

Where:

• nlevels represents the number of switch levels in the network hierarchy

- dims[i] represents the number of switches at level i in the network hierarchy. dims is therefore an array of size nlevels.

- coords[i] represents the coordinates (or "rank") of the calling process at level i in the network hierarchy. coords is also an array of size nlevels.

The last level in the network hierarchy is not taken into account as it is merely a port number in the last switch. Since all nodes are connected to a switch with their own port number, this information has no use in our context and is redundant with the "Node" level.

From an implementation's point of view, adding the knowledge of the network hierarchy introduces moderate modifications to the existing code, as it was conceptually ready to support such feature. The switch level number is added as a possible string returned by the MPI\_Comm\_get\_min\_hlevel function.

## 5 Practical examples

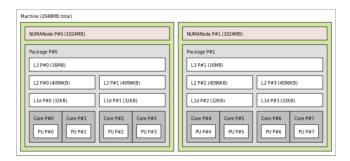

Figure 1: A hierarchical node example.

We now detail practical examples of use of this new split\_type value. Let us suppose that an MPI application is launched on several machines featuring the memory hierarchy depicted by Figure 1: each node is composed of two NumaNodes with a single socket (i.e. package) and 4 cores per socket. Each socket features its dedicated L3 cache and a L2 cache is shared between a pair of cores (hence 4 L2 caches in total). At some point, we assume that the various processes of the application execute the following code:

In this code snippet, NLEVELS is chosen appropriately so that there are enough elements in the newcomm array, but as we discussed previously (see Section 3.4), our proposal does not make any

assumption on the total number of levels in the hardware hierarchy nor on the nature of the hardware resource the communicator is supposed to represent for the processes.

Our proposal does not feature a query function that yields that maximum number of hierarchy levels, as it would incur to an additional time the communicators hierarchy. Practically, this number is not going to be very high, a few tenths at most. As a consequence, having a statically allocated array as in our example is not an issue for memory consumption.

## 5.1 A simple case

In our first case, we suppose that we have an application featuring 32 processes, launched on a 4-node cluster, each node ( $n_k, k \in [0..3]$ ) is as described previously. Let us also suppose that each process is bound to its own dedicated core. For instance, process  $p_x$  (of rank x in MPI\_COMM\_WORLD) is bound to core number i of node number k where k where k is k in k in k in k when the code shown above is executed, the following communicators are created in several steps, where one step corresponds to a call to the MPI\_Comm\_split\_type function:

• step 1: Since processes are located on 4 different nodes, MPI\_COMM\_WORLD encompasses all these nodes. As newly created communicators have to be strictly "included" in their parent communicator, new communicators corresponding to the "Machine" level of each node shall be created. That is:

```

newcomm[0] = \{p_{8k}, p_{8k+1}, \dots, p_{8k+6}, p_{8k+7}\}

(for each node number k \in [0, 3])

```

This is equivalent to a call to MPI\_Comm\_split\_type with the MPI\_COMM\_ TYPE\_SHARED parameter. However, the implementation might also decide to create an intermediate level between MPI\_COMM\_WORLD and this one to represent a level of network switches. In our case, we suppose that all nodes are connected to the same switch and no such intermediate level is created.

For the sake of simplicity, and without loss in generality, we shall now focus only on the communicators created on node number 0 in the remaining steps described below.

• step 2: Since all processes are now located on the same node, newcomm[0] encompasses the whole node. As newly created communicators have to be strictly "included" in their parent communicator, the next communicator should correspond to a level strictly smaller than the "Machine" level. The next meaningful hardware level in the target hierarchy is then the NumaNode/Package/L3 level and since the highest level is chosen in case of redundancies, the "NumaNode" level is chosen. As a consequence, two new communicators are created, one for the first NumaNode and one other for the second NumaNode. More precisely, the two newly created communicators are composed by the following processes:

$$newcomm[1] = \{p_{4i}, p_{4i+1}, p_{4i+2}, p_{4i+3}\}$$

(for each NumaNode number  $i \in [0, 1]$ )

• step 3: In this next step, we shall split the communicators created during step 2, the NumaNode communicators now are the parents communicators in the next call to MPI\_Comm\_split\_type. Since there are two L2 caches/L1 caches per NumaNode, these physical entities are the ones for which new communicators are created. Once again, the highest level is chosen and in

<sup>&</sup>lt;sup>6</sup>A "by node" mapping policy in conjunction with a "by core" binding policy for processes.

this second step, the new communicators correspond to the L2 caches. Practically, a new call to MPI\_Comm\_split\_type with a newcomm[1] communicator as input will produce the following four communicators in node 0:

$$newcomm[2] = \{p_{2i}, p_{2i+1}\}$$

(for each L2 number  $i \in [0, 3]$ )

• step 4: In the next step, a total of eight communicators are created, since two cores/processing units (a.k.a PU) share a single L2 cache. The "Core" level is preferred because it is the highest in the hierarchy. At this step, a total of eight communicators are created, one per process. These communicators are the following:

$$newcomm[3] = \{p_i\}$$

(for each Core number  $i \in [0, 7]$ )

It is to be noted that if  $p_i$  called:

then result would have MPI\_CONGRUENT for value.

• step 5: In this last step, since we have reached the bottom of the hierarchy, no new valid communicators are produced. Therefore, all calls to MPI\_Comm\_split\_type yield:

$$\mathtt{newcomm}[4] = \mathtt{MPI\_COMM\_NULL}$$

( for each Core number  $i \in [0,7]$ )

In the code snippet shown above, if the call to MPI\_Comm\_split\_type is replaced by MPI\_Comm\_hsplit\_with\_roots, another hierarchy of communicators is also produced, that is, the roots communicators. That is, rootscomm[i] is created during the same step as newcomm[i].

• step 1: Since four communicators are created (one for each Node), the roots communicator contains four processes. Since the ranks are retained in the new communicators, this means that the root in each communicator is the process with the lowest rank. Therefore:

$$rootscomm[0] = \{p_{8k}\}, k \in [0..3]$$

As in the previous case, we now examine the next step for a single node only.

• step 2: Since two communicators are created (one for each NumaNode), the single roots communicator contains two processes. Therefore:

$$rootscomm[1] = \{p_0, p_4\}$$

Please note that the root of rootscomm[1] is also a member of rootscomm[0].

• step 3: Each "NumaNode" communicator is split into two "L2" subcommunicators. Hence, two roots communicators are created during this step and they contain two processes each:

$$\begin{aligned} &\texttt{rootscomm}[2] = \{\mathbf{p_0}, p_2\} (\text{for NumaNode number 0}) \\ &\texttt{rootscomm}[2] = \{\mathbf{p_4}, p_6\} (\text{for NumaNode number 1}) \end{aligned}$$

As expected, the roots of both rootscomm[2] communicators are the members of rootscomm[1].

• **step 4:** The same logic of step 3 is applied: each "L2" communicator is split into two "Core" subcommunicators. A total of four roots communicators are then created at this step, which two processes each. That is:

```

\mathtt{rootscomm}[3] = \{\mathbf{p_0}, p_1\} \text{ (for L2 cache number 0)}

\mathtt{rootscomm}[3] = \{\mathbf{p_2}, p_3\} \text{ (for L2 cache number 1)}

\mathtt{rootscomm}[3] = \{\mathbf{p_4}, p_5\} \text{ (for L2 cache number 2)}

\mathtt{rootscomm}[3] = \{\mathbf{p_6}, p_7\} \text{ (for L2 cache number 3)}

```

Once again, the roots of rootscomm[3] are members of either one of the rootscomm[2] communicators.

• **step 5:** Since the bottom of the hierarchy is reached, no roots communicators are produced during this last step. As expected:

```

rootscomm[4] = MPI_COMM_NULL (8 times, one per process)

```

## 5.2 A more complicated case

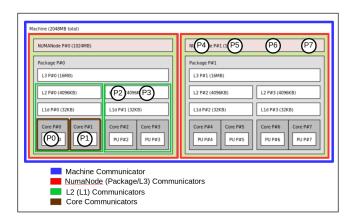

This second example demonstrates the flexibility of our proposal and its ability to cope with more complicated cases than the straightforward example described in the previous section. Even if we do not expect such cases to be commonplace, we emphasize that they do not raise any issue practically. In this example, we launch an application on a single 8-core node where the various processes follow their own binding policy. As a consequence, the processes are not uniformly bound on the machine. Figure 2 depicts such a case involving 8 processes in MPI\_COMM\_WORLD: processes rank 0 and 1 are bound to core 0 and 1 respectively, while processes 2 and 3 are bound on the L2 cache number 1. This means that during the application execution, these processes can execute on either core number 2 or 3, since both cores share the L2 cache number 1. Processes 4, 5, 6 and 7 are bound to NumaNode number 1. In this case they can use any of the cores that belong to this NumaNode, that is, either core 4, 5, 6 or 7. Here again, nothing prevents the core to change during the application execution.

Figure 2: A case of non-uniform binding policy for processes

In this case, and according to the proprieties of the hierarchical communicators, we shall have the following results if the code snippet shown previously is executed by all processes: • step 1: All processes are located within the same node, hence MPI\_COMM\_WORLD encompasses the whole node. This original communicator is the "Machine" communicator (the blue one) on Figure 2. We use this input communicator for the split operation and since the next meaningful level in the hardware hierarchy is the NumaNode/Package/L3 one, two new communicators are created, since there are two NumaNodes below the "Machine" level. As in the previous example, the highest level is chosen, that is, the "NumaNode" level.

```

newcomm[0] = \{p_{4i}, p_{4i+1}, p_{4i+2}, p_{4i+3}\}

(for NumaNode number i \in [0, 1])

```

These communicators are the red ones on Figure 2.

• step 2: In this step, the newcomm[0] communicators are handled differently as the processes belonging to them have different binding policies. In the case of the communicator that covers NumaNode number 0, all processes are bound to at least a L2 cache, this step is similar to the second step of the first example. However, the case of NumaNode number 1 is very different, as the hierarchy cannot be determined since all processes can potentially move inside their NumaNode from one core to the other during the application execution, as explained in Section 3.2.4. As a consequence, no new valid communicator is created during this step for NumaNode number 1. Therefore only two subcommunicators are created:

```

\begin{array}{l} \texttt{newcomm}[\texttt{1}] = \{p_{2i}, p_{2i+1}\} \text{ (for each L2 number } i \in [0,1] \text{ )} \\ \texttt{newcomm}[\texttt{1}] = \texttt{MPI\_COMM\_NULL} \text{ (for each L2 number } i \in [2,3] \text{ )} \end{array}

```

These communicators are the green ones on Figure 2.

• step 3: From this step on, only the valid communicators can be split again, that is, the L2 communicators of NumaNode number 0. Since processes rank 0 and 1 are bound to core, it is possible to create new subcommunicators that correspond to this level. However, since processes rank 2 and 3 are not bound "deeper" than the L2 cache level, no new communicator can be created. Once again, only two new valid communicators are created:

```

\begin{split} \mathbf{newcomm}[2] &= \{p_i\} \text{ (for each Core number } i \in [0,1]) \\ \mathbf{newcomm}[2] &= \mathtt{MPI\_COMM\_NULL} \text{ (for each Core number } i \in [2,3] \text{ )} \end{split}

```

These communicators are the brown ones on Figure 2.

• **step 4:** In this last step, the bottom of the hierarchy is finally reached for processes rank 0 and 1. For all other processes, the bottom has been reached in one of the previous steps. Therefore:

```

newcomm[3] = MPI_COMM_NULL (for each Core number i \in [0, 1])

```

Let us now examine the case where the MPI\_Comm\_hsplit\_with\_roots function was to be called instead of MPI\_Comm\_split\_type. Nothing would change as far as the subcommunicators creation is concerned. However, fewer roots communicators would be created:

• step 1: In the first step, since one communicator corresponding to each NumaNode is created, the single roots communicator would contain two processes:

$$\mathtt{rootscomm}[\mathtt{0}] = \{p_0, p_4\}$$

• step 2: In the second step, no roots communicator is created for NumaNode number 1. The roots communicator for NumaNode 0 contains only two processes, the roots of the L2 cache subcommunicators. That is:

```

\label{eq:potscomm} \begin{split} \texttt{rootscomm}[\texttt{1}] = \{\mathbf{p_0}, p_2\} \; (\text{for NumaNode number 0}) \\ \texttt{rootscomm}[\texttt{1}] = \texttt{MPI\_COMM\_NULL} \; (\text{for NumaNode number 1}) \end{split}

```

Once again, we can verify that the root process of the valid rootscomm[1] communicator is also a member of rootscomm[0].

• step 3: In this step, only the roots communicator of the L2 cache number 0 can be created, as processes rank 2 and 3 are not bound deeper that the L2 level in the machine. Therefore:

```

rootscomm[2] = \{p_0, p_1\} (for L2 cache number 0) rootscomm[2] = MPI\_COMM\_NULL (for L2 cache number 1)

```

The root process of rootscomm[2] is also a member of rootscomm[1].

• **step 4:** The bottom of the hierarchy is reached, two non-valid roots communicators are produced during this step, as this has already been done in previous steps for the rest of the processes in the node.

```

rootscomm[3] = MPI_COMM_NULL

(two times, for processes 0 and 1)

```

This demonstrates that our proposal is flexible enough to accommodate the case of non-uniform binding policies within the same MPI application. This is possible because our approach does not depend on the binding policy applied to the various processes of the application.

# 6 Benefits of the hierarchical model for parallel applications

In this section we propose to model the class of MPI applications that can leverage our hierarchical abstraction to enhance the performance of their communications. Let us suppose that an

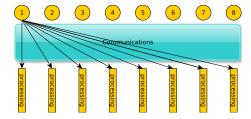

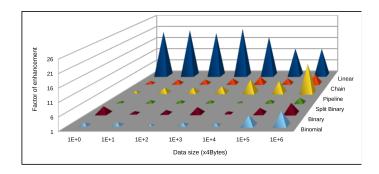

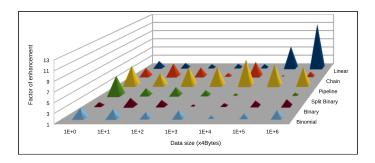

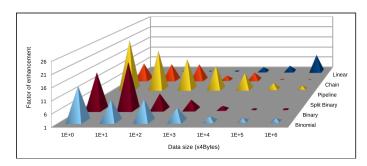

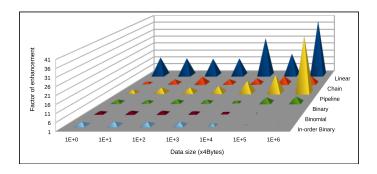

Figure 3: Superstep of MPI application family based on native collective communications

MPI application features p MPI processes. The application execution model we focus on is in the form of a repetitive phasis of super-steps including communication operations C followed by execution operations E as shown by Figure 3. Each process needs to terminate its communication operation to start the processing of data as shown on Algorithm 3.

## Algorithm 3: MPI algorithm covered by our hierarchical model

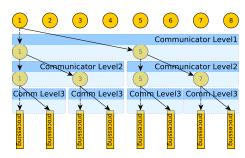

Figure 4: Superstep of MPI application family based on hierarchical collective communications

If the communication operations C include collective operations, then the application can take advantage of the hierarchical model described by Algorithm 4, where L is the number of levels in the hierarchy allowed by the target architecture and generated automatically by our approach. Figure 4 illustrates the application communication model based on a three-level communicator hierarchy.

### Algorithm 4: MPI algorithm based on a hierarchical communication model

Applying a hierarchical model can improve the communication times and thus the total time of the application. As a matter of fact, by exploiting more parallelism in the hierarchy levels, it is possible to enhance the scalability and performance of collective operations. In order to illustrate this claim we propose a short discussion to highlight the important features which can explain this benefit.

The collective communications are modeled with well-known works such as the Hockney [6], the LogP [3] or the PlogP [11] model. These models express the maximum time taken by a collective communication operation as a linear f unction depending on several variables such as:

- p: The number of processes performing the collective communication operation c.

- m: The size of the data exchanged between processes.

- The collective algorithm used.

- $\alpha$ : The hardware latency that may be a function of m and p.

- $\beta$ : The hardware bandwidth that may be a function of m and p.

For example, the processing time of the simple Flat Tree broadcast is expressed with the Hockney [6] model as equal to:

$$(p-1) \times (\alpha + m\beta)$$

As shown by Algorithm 4 L levels of communications are present in the topology-aware hierarchical model according to the structure of the architecture. Thus, the time of collective operations will be represented as a sum of L functions depending on the previous cited features but where each level is characterised by a set of specific parameters:  $p_i$ ,  $\alpha_i$ ,  $\beta_i$  and  $m_i$ . As a consequence, the Flat Tree broadcast example shall be expressed as:

$$\sum_{i=0}^{L-1} (p_i - 1) \times (\alpha_i + m\beta_i)$$

The hardware topology-aware hierarchical model could reduce the processing time of collective operations by exploiting the following points:

- Fewer processes per level: in most applications, it is enough to use a pyramidal structure in the hierarchical model of computation. In fact, as illustrated by Figure 4, the structure based only on the roots of hierarchical communicators in upper levels is enough to perform the communication. Such a structure implies to use fewer processes  $p_i$  by level, which reduces the processing time of the collective.

- Parallelism by level: this point regards the exploitation of parallelism at each level of the hierarchy. Indeed, and except for the top level of the hierarchy, the communications inside the communicators of the same level are carried out in parallel.

- Data locality and process affinity: This point highlights the advantage of using hardware-aware communicators. Indeed, taking into account the hardware affinity of processes placement in the machine, the communication between them is enhanced thanks to the cache optimizations.

- Improved latency and bandwidth per level: this point concerns the physical latency and bandwidth which could be improved when the number of processes is small. In fact, because of the contention phenomenon, the higher the number of processes involved in the communication at the same time through an interconnect, the higher the latency and the lower the bandwidth delivered to each process.

From all the above points, collective communication operations could be improved depending on the execution conditions. For instance, if we take the Flat Tree broadcast of a single message (m=1) and operated in the simple context of 8 processes and the three-level hierarchy as described by Figure 4 then the result is:

The simple case:

$$Time = (8-1)(\alpha + \beta)$$

The hierarchical case:

$$Time = (2-1)(\alpha_0 + \beta_0) + (2-1)(\alpha_1 + \beta_1) + (2-1)(\alpha_0 + \beta_1)$$

If we compare both expressions, it is clear that the hierarchical approach enhances the simple collective with the factor of at least (7/3) times when latencies and bandwidths are equal in both the simple and the hierarchical cases. However, in the real situation, the simple execution could generate more contention on the interconnects of each level than the hierarchical execution. Thus, the factor of enhancement of collective time could be greater than (7/3).

## 7 Experimental Results

In this section we present the experimentations we carried out and their results to demonstrate the benefits of our proposal. We modified two benchmarks by introducing our hierarchical model of communicators and we compared their executions on three architectures. In all cases we used the roots communicators hierarchy generated by calling the primitive described in subsection 3.2.3. In addition, we used all cores of a targeted architecture and bound an MPI process on each of them.

### 7.1 Platforms and architectures

For our study, we used tree architectures: a network of 10 nodes (NTW10E5) and two SMP machines (SMPE12E5, SMP20E5) from the Plafrim platform [17]. The characteristics of these architectures are given in Table 1.

Table 1: Characteristics of the used architectures. NUMA nodes are grouped by pairs based on distance in large SGI platforms. These pairs correspond to the physical blades.

| SMP12E5                      | SMP20E7                                                                                          | NTW10E5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NTW24E5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RHEL7                        | SLES11                                                                                           | CentOS 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Red Hat 4.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.10.0                       | 2.6.32.46                                                                                        | 3.10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1                            | 1                                                                                                | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12 (6 pairs)                 | 20 (10 pairs)                                                                                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12                           | 20                                                                                               | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8                            | 8                                                                                                | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| E5-4620v2                    | E7-8837                                                                                          | E5-2680v3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | E5-2680v3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

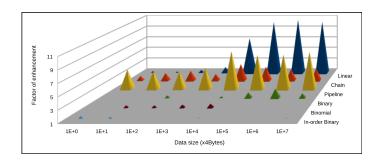

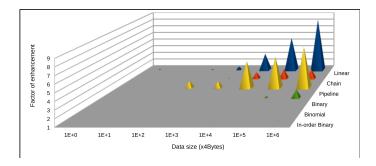

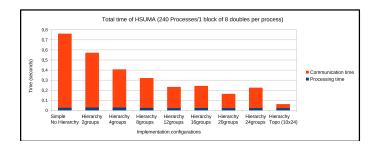

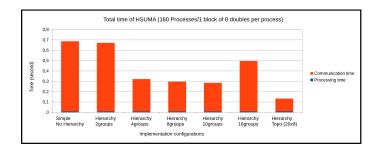

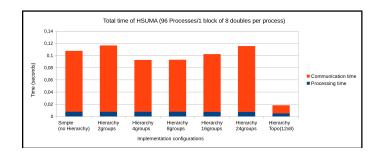

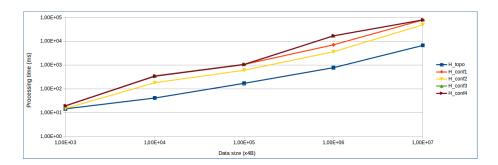

| $2600 \mathrm{M}\mathrm{hz}$ | $2660 \mathrm{Mhz}$                                                                              | $2600 \mathrm{M}\mathrm{hz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $2600\mathrm{M}\mathrm{hz}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |