# TCAD Simulation of Amorphous Indium-Gallium-Zinc Oxide Thin-Film Transistors

Jorge Martins, Pedro Barquinha, João Goes

# ▶ To cite this version:

Jorge Martins, Pedro Barquinha, João Goes. TCAD Simulation of Amorphous Indium-Gallium-Zinc Oxide Thin-Film Transistors. 7th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Apr 2016, Costa de Caparica, Portugal. pp.551-557, 10.1007/978-3-319-31165-4 52. hal-01438284

# HAL Id: hal-01438284 https://inria.hal.science/hal-01438284

Submitted on 17 Jan 2017

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# TCAD Simulation of Amorphous Indium-Gallium-Zinc Oxide Thin-Film Transistors

Jorge Martins<sup>1</sup>, Pedro Barquinha<sup>1</sup>, João Goes<sup>2</sup>

<sup>1</sup>i3N/CENIMAT, Department of Materials Science, Faculty of Science and Technology, Universidade NOVA de Lisboa and CEMOP/UNINOVA, Campus de Caparica, 2829-516 Caparica, Portugal

<sup>2</sup> CTS-UNINOVA, Dep. Eng. Electrotécnica, Faculdade de Ciências e Tecnologia, Universidade Nova de Lisboa, 2825-149 Caparica, Portugal jorge.souto.martins@gmail.com

**Abstract.** Indium-gallium-zinc oxide (IGZO) thin-film transistors (TFTs) are simulated using TCAD software. Nonlinearities observed in fabricated devices are obtained through simulation and corresponding physical characteristics are further investigated. For small channel length (below 1 μm) TFTs' simulations show short channel effects, namely drain-induced barrier lowering (DIBL), and effectively source-channel barrier is shown to decrease with drain bias. Simulations with increasing shallow donor-like states result in transfer characteristics presenting hump-like behavior as typically observed after gate bias stress. Additionally, dual-gate architecture is simulated, exhibiting threshold voltage modulation by the second gate biasing.

Keywords: IGZO, TCAD simulation, DOS, TFT, CPS.

#### 1 Introduction

Oxide TFTs are nowadays starting to play an important role in display industry, with leading companies as LG using them in the backplane of recent products, such as curved organic light emitting device (OLED) TV sets. Still, significant advances in the current state-of-the-art of oxide TFT technology are required before high performance fully transparent, flexible, low-cost and low-power dissipation electronics reach the maturity level required for commercialization. The implementation of Technology Computer-Aided Design (TCAD) [1][2] tools for simulation of devices at a physical level can lead to understanding on how to further improve fabrication processes, material properties and device architectures. The ultimate goal is to enhance the performance of amorphous oxide TFTs, mimicking the routes followed for single-crystalline CMOS, a-Si and poly-Si technologies. Embedding physically-extracted parameters from the fabricated devices into the models for simulation, accurate models can be built and prediction on how changes in materials and processes affect physical response of the oxide TFTs can be achieved. This can allow viable process and device development and, simultaneously, understanding, the otherwise difficult or even impossible to extract physical

characteristics behind device operation. Some specific goals to be addressed are referred next.

As performance of amorphous oxide semiconductors (AOS) is controlled by the density of states (DOS) in a given material, and TCAD simulation is based in the DOS [3], it can provide understanding of the specific nature of states causing performance differences among different AOS. This can be used for instance to achieve a suitable and sustainable indium-free replacement for IGZO. Modeled IGZO TFTs based on DOS extracted from different techniques have shown to agree very well with measured characteristics, without employing any fitting parameter [4] [5]. Instabilities in oxide TFTs can be further investigated with TCAD, by implementing charge-trapping and defect creation in the simulations, allowing to understand the specific physical causes of degradation in TFTs, typically associated with Gate/Drain Bias Stress, illumination and temperature. Correlations between the defect-creation and the device performance degradation have been reported [6], with localization of defect creation being also investigated by means of simulations [7]. Some effects that limit device performance are related to device architecture, as parasitic capacitances that limit the maximum operation frequency, and short channel effects (SCE), which limit the scalability of the technology. As architectures can be arbitrarily defined in TCAD simulation optimization and understanding of physical phenomena in different geometries appears as a great advantage. Moreover, as recently more and more TFT architectures are proposed (e.g. dual-gate, floating-capping-metal, bulk-accumulation [8] and dual-active layer TFTs), TCAD can accelerate the optimization of those configurations, reducing fabrication runs and elucidating the physics behind the electrical behavior of each architecture [9].

In this work the short channel effect Drain Induced Barrier Lowering (DIBL) is shown with TCAD simulation in  $\mu$ m-scale IGZO TFTs. To the best of the authors' knowledge it's the first time that the barrier level for different drain bias is displayed for  $\mu$ m-scale oxide TFTs.

# 2 Integration in Cyber Physical Systems

Amorphous oxide electronics allow for production in a wide range of substrates, notably, inexpensive flexible and/or transparent substrates, as they can be processed at low temperatures (while still maintaining good performance) and have large area uniformity due to their amorphous nature. This way, they can be integrated into a wider range of systems, rather than their silicon technology counterparts. This technology thus shows to have great applicability in Cyber Physical Systems (CPS). In the CPS 5Cs architecture, amorphous oxides can be integrated in the Connection and the Conversion layers. In the Connection level they present the already discussed advantages of being applicable in wide range of substrates, as flexible and transparent ones. Several applications have already been reported as gas sensors [10], touch-panels [11] and even biological sensors [12]. Integrated with the connection level, the technology can also be in the conversion level as they have performance that allow for the processing of the information received at the Connection level. In fact, one of the current trends of oxide TFT technology is precisely focused on full integration and

in increasingly more complex circuits, including signal processing, amplification and, ultimately, analog-to-digital conversion [13].

#### **TCAD Simulation**

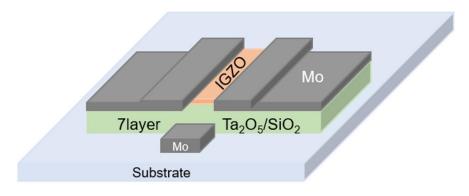

In this section some preliminary simulations are presented, addressing specific scenarios in which IGZO TFT devices, as produced in our group, show the need for improvement. Sputtered staggered bottom-gate TFTs on glass have been produced. A 60 nm thick Molybdenum (Mo) gate electrode was sputtered. The dielectric layer is a sputtered 100 nm thick 7 layer multicomponent oxide (alternating layers of SiO<sub>2</sub> and Ta<sub>2</sub>O<sub>5</sub>). The active layer is a 40 nm thick amorphous IGZO (with 2:1:1 composition in In:Ga:Zn atomic ratio), also sputtered. Finally, 60 nm thick Mo source and drain electrodes have been sputtered. All layers were patterned by photolithography and lift-off with exception of the dielectric layer, in which, photolithography and dryetching have been used. A schematic of the fabricated devices can be seen in Fig. 1. After all layer fabrication devices were annealed at 180° C for 10 minutes in air in a rapid thermal annealing system. This fabrication process is compatible with commercial polymeric films.

Fig. 1. Schematic of the sputtered IGZO TFTs.

For simulation purposes the TCAD Silvaco's 2D ATLASTM was used. A similar configuration than that of fabricated devices was employed. An electron mobility of 16 cm<sup>2</sup> (V s)<sup>-1</sup> and electron concentration of 10<sup>16</sup> cm<sup>-3</sup> in the a-IGZO was assumed. Both fabricated and simulated TFTs have a channel length of 20 um unless otherwise is specified. Channel width of the characterized TFTs is 20 µm and for simulated devices the obtained drain current in 2D simulation is factored in order to correspond to a 20 µm width channel TFT.

#### 3.1 Short Channel Effects

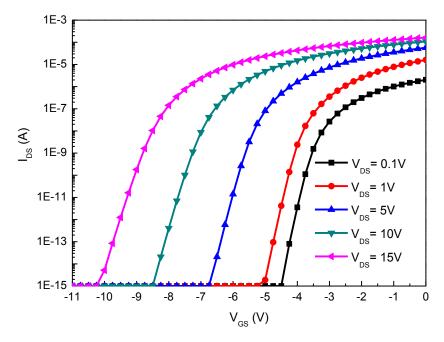

Sputtered IGZO TFTs with channel length (L) below 5  $\mu$ m have exhibited SCEs, which are well known in silicon technology, where devices are of nm-scale. As low L (5  $\mu$ m and below) IGZO TFTs have been reported with [14] and without [15] SCEs, TCAD simulation was used to investigate this physical limitation further, as the the mechanisms for enabling or not the SCE are not clear yet. Preliminary simulations for similar TFTs showed that the short channel effects occur for L = 0.5  $\mu$ m. As shown in Fig. 2, turn-on voltage (Von) shifts negatively with increasing drain bias in the simulated transfer characteristics. This effect is explained as Drain Induced Barrier Lowering (DIBL), as for low L drain bias can reduce the Source-Semiconductor schottky junction barrier.

Fig. 2.  $V_{On}$  shift with increasing drain bias for simulated L = 0.5  $\mu m_{\bullet}$

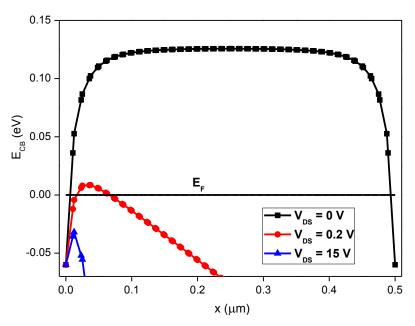

By extracting the conduction band energy level across the channel the decreasing of the barrier between source and semiconductor with increasing drain bias is clear, as shown in Fig. 3.

**Fig. 3.** Conduction band energy of IGZO in respect to the fermi level ( $E_F$ ) for a L=0.5  $\mu$ m IGZO TFT, showing source-semiconductor barrier lowering (at x=0 $\mu$ m) for increasing drain bias.

# 3.2 Hump in Transfer Characteristics.

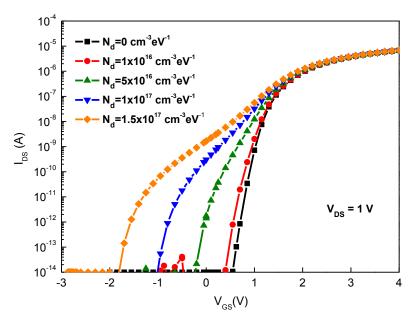

Performance degradation by irradiation, temperature and/or bias stress is one the main challenges for the application of oxide electronics. Fabricated devices showed hump like behavior in transfer characteristics after gate bias stress. This hump has been reported on several scenarios, and many different explanations have been reported so far. Some authors report it as a result of an effect of shallow donor-like states creation in the semiconductor [6]. Fig. 4 shows a simulation with increasing peak value of this shallow donor state, assuming 0.1eV of peak variance and a state energy 0.2 eV below conduction band, since energy states at this level have been reported [16]. The concentration increase in these states leads to the creation of an increasingly more visible hump, suggesting that it might be the (or at least, one of the) creation mechanisms for the hump.

**Fig. 4.** Increasing of hump-like behavior in transfer characteristics of IGZO TFTs with increasing concentration of shallow donor-like states.

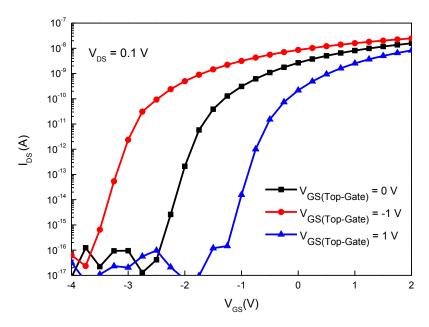

#### 3.3 Dual-Gate TFT

Typically, fabricated IGZO TFT in our research group at CENIMAT/I3N at FCT NOVA show a depletion mode operation, which complicates its application in circuits. Some architectures for threshold voltage modulation have been already reported, as applying a second-gate on the back-interface of the semiconductor. Fig. 5 shows simulated transfer characteristics for dual-gated IGZO TFTs, with different fixed bias on the second gate. The added top gate and top gate oxide for dual-gate simulation are identical to the bottom gate and bottom gate oxide. As expected the  $V_{\rm on}$  is modulated, which can be used to achieve enhancement mode devices.

Fig. 5. Modulation of Von in dual-gate IGZO TFT by second gate bias.

### **Conclusions and Future Work**

TCAD simulations have demonstrated to be a powerful tool to improve understanding on amorphous oxide TFTs and reduce fabricated batches and costs. Short channel effects have been shown in simulations of IGZO TFTs, and these are in agreement to what was verified in fabricated devices by sputtering. Transfer characteristics shifted with drain bias, explained as DIBL, and the barrier has been effectively seen to reduce with drain bias observing the simulated conduction band energy in the IGZO. Further investigation on the SCEs, such as understanding the role of the schottky barrier, might elucidate on how to suppress these effects. As for the hump behavior, simulation showed that it may be somehow related to shallow donor-like state creation. Further investigation on how specific DOS affect the device characteristics will lead to understanding the mechanisms of degradation in the oxide TFTs. Finally, simulation of a double-gate TFT was employed, and the Von modulation by the second gate bias was observed. This modulation can be used to achieve enhancement mode TFTs as preferred for application in circuit.

### Acknowledgements

This work is funded by FEDER funds through the COMPETE 2020 Programme and National Funds through FCT - Portuguese Foundation for Science and Technology under the Project Nos. UID/CTM/50025/2013 and EXCL/CTM-NAN/0201/2012. The work has also received funding from the European Communities 7th Framework Programme under grant agreement ICT-2013-10-611070 (i-FLEXIS project) and from H2020 program under ICT-03-2014-644631 (ROLL-OUT project).

#### References

- 1. Software, D.S.: ATLAS User 's Manual. 567-1000 (2013).

- 2. C-, V., Started, G.: Sentaurus Device User Guide. Synopsis (2009).

- 3. Hsieh, H.-H., Kamiya, T., Nomura, K., Hosono, H., Wu, C.-C.: Modeling of amorphous InGaZnO4 thin film transistors and their subgap density of states. Appl. Phys. Lett. 92, 133503 (2008).

- Jeon, K., Kim, C., Song, I., Park, J., Kim, S., Kim, S., Park, Y., Park, J.H., Lee, S., Kim, D.M., Kim, D.H.: Modeling of amorphous InGaZnO thin-film transistors based on the density of states extracted from the optical response of capacitance-voltage characteristics. Appl. Phys. Lett. 93, 4–7 (2008).

- 5. Junfei Shi, Chengyuan Dong, Y.S.: Influence of Deep States in Active Layers on the Performance of Amorphous In-Ga-Zn-O Thin Film Transistors Junfei Shi, Chengyuan Dong and Yikai Su. Proc. China Display/Asia Disp. 2011. 356–359 (2011).

- Im, H., Song, H., Jeong, J., Hong, Y., Hong, Y.: Effects of defect creation on bidirectional behavior with hump characteristics of InGaZnO TFTs under bias and thermal stress. Jpn. J. Appl. Phys. 54, 153–156 (2015).

- 7. Lee, J., Choi, S., Kim, S.K., Choi, S., Kim, D.H., Park, J., Kim, D.M.: Modeling and Characterization of the Abnormal Transistors After High Positive Bias Stress. IEEE Electron Device Lett. 36, 1047–1049 (2015).

- 8. Mativenga, M., An, S., Jang, J.: Bulk accumulation a-IGZO TFT for high current and turnon voltage uniformity. IEEE Electron Device Lett. 34, 1533–1535 (2013).

- Lu, T., Chen, W., Zan, H., Ker, M.: Investigating electron depletion effect in amorphous indium – gallium – zinc-oxide thin-film transistor with a floating capping metal by technology computer-aided design simulation and leakage reduction. Jpn. J. Appl. Phys. 53, 064302 (2014).

- 10.Chen, K.-L., Jiang, G.-J., Chang, K.-W., Chen, J.-H., Wu, C.-H.: Gas sensing properties of indium-gallium-zinc-oxide gas sensors in different light intensity. Anal. Chem. Res. 4, 8– 12 (2015).

- 11.Fu, R., Liao, C., Leng, C., Zhang, S.: An IGZO TFT based in-cell capacitance touch sensor. ICSICT 2012 - 2012 IEEE 11th Int. Conf. Solid-State Integr. Circuit Technol. Proc. 4, 5–7 (2012).

- 12.Shen, Y.-C., Yang, C.-H., Chen, S.-W., Wu, S.-H., Yang, T.-L., Huang, J.-J.: IGZO thin film transistor biosensors functionalized with ZnO nanorods and antibodies. Biosens. Bioelectron. 54, 306–10 (2014).

- 13.Correia, A.P.P., Barquinha, P., Goes, J.C. da P.: A Second-Order ΣΔ ADC Using Sputtered IGZO TFTs. Springer International Publishing (2015).

- 14.Chen, R., Zhou, W., Zhang, M., Wong, M., Kwok, H.S.: Self-aligned top-gate InGaZnO thin film transistors using SiO2/Al2O3 stack gate dielectric. Thin Solid Films. 548, 572–575 (2013).

- 15.Park, J.-S.: Characteristics of short-channel amorphous In-Ga-Zn-O thin film transistors and their circuit performance as a load inverter. J. Electroceramics. 28, 74–79 (2012).

- 16.Oba, F., Nishitani, S.R., Isotani, S., Adachi, H., Tanaka, I.: Energetics of native defects in ZnO. J. Appl. Phys. 90, 3665 (2001).