# Polychronous automata and their use for formal validation of AADL models

Thierry Gautier, Clément Guy, Alexandre Honorat, Paul Le Guernic, Jean-Pierre Talpin, Loïc Besnard

#### ▶ To cite this version:

Thierry Gautier, Clément Guy, Alexandre Honorat, Paul Le Guernic, Jean-Pierre Talpin, et al.. Polychronous automata and their use for formal validation of AADL models. Frontiers of Computer Science, 2019, 13 (4), pp.677-697. 10.1007/s11704-017-6134-5. hal-01411257

### HAL Id: hal-01411257 https://inria.hal.science/hal-01411257

Submitted on 7 Dec 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Polychronous Automata and their Use for Formal Validation of AADL Models

Thierry GAUTIER (\(\sum \))\(^1\), Clément GUY \(^1\), Alexandre HONORAT \(^1\), Paul LE GUERNIC \(^1\), Jean-Pierre TALPIN \(^1\)

Loïc BESNARD \(^2\)

1 INRIA, Rennes-Bretagne-Atlantique Research Centre, France 2 CNRS, IRISA, Rennes, France

© Higher Education Press and Springer-Verlag Berlin Heidelberg 2012

Abstract This paper investigates how state diagrams can be best represented in the polychronous model of computation (MoC) and proposes to use this model for code validation of behavior specifications in AADL. In this relational MoC, the basic objects are signals, which are related through dataflow equations. Signals are associated with logical clocks, which provide the capability to describe systems in which components obey to multiple clock rates. We propose a model of finite-state automata, called polychronous automata, which is based on clock relations. A specificity of this model is that an automaton is submitted to clock constraints. This allows one to specify a wide range of control-related configurations, either reactive, or restrictive with respect to their control environment. A semantic model is defined for these polychronous automata, that relies on a Boolean algebra of clocks. Based on a previously defined modeling of AADL software architectures using the polychronous MoC, this model of polychronous automata is used as a formal model for the AADL Behavior Annex. This is illustrated with a case study which specifies an adaptive cruise control system.

#### 1 Introduction

The design of embedded systems, and more specifically critical systems, requires the satisfaction of strong, various and heterogeneous constraints such as safety, determinism of embedded threaded distributed programs, or implementation, scheduling in a specific or non specific OS, etc. One way to help designers is to provide them with friendly usable tools supported by strong mathematical semantics. These formal models and methods allow to ensure correctness of components used or defined at each The polychronous model of level of the design. computation [1] is such a formal model. Historically related to the synchronous programming paradigm [2] (Esterel [3], Lustre [4]), the polychronous model of computation, implemented in the dataflow language Signal [5, 6] and its environment Polychrony<sup>1)</sup>, stands apart by the capability to model multi-clocked systems. The synchronous paradigm consists of abstracting the non-functional implementation details of a system and lets one benefit from a focused reasoning on the logics behind the instants at which the system functionalities should be secured. The fundamental notion of polychrony consists in the capability to describe systems in which components obey to multiple clock rates. In particular, the Signal language gives the opportunity to seamlessly model embedded systems at multiple levels of abstraction while reasoning within a simple and formally defined mathematical model. A design approach that may be advocated is to allow for a seamless inter-operation of heterogeneous programming viewpoints within the same host model of computation which is the polychronous model. A typical case study from Airbus, for instance, was based on a co-modeling of the doors management system of the A350 [7]. In this case study, functionalities were

Received month dd, yyyy; accepted month dd, yyyy

1) http://polychrony.inria.fr

modeled with synchronous Simulink<sup>2)</sup> and a system-level model of the hardware equipment was specified in AADL (Architecture Analysis & Design Language) [8]. Polychrony toolbox was then used to interpret computations and communications specified in both models in order to synthesize schedulers for sequential and distributed simulation. The experiment was successful, since it has demonstrated that the polychronous model, through its supportive language Signal, may be used as an effective common semantic model for representing or interfacing heterogeneous models. However, Signal is based on a dataflow oriented notation, thus there is sometimes some distance between an actual specification, which may use, for instance, state oriented description, and its semantic encoding as systems of equations. This may cause some practical difficulties, in particular when traceability is a requirement, as is the case in most systems.

In this paper, first, we investigate the way state diagrams can be best represented in the polychronous model of computation, maintaining the multi-clock characteristic property of the representation. We propose a model of automata, called polychronous automata, which is based on clock (or event) relations, and allows one to specify a wide range of control-related configurations, more or less permissive (or, dually, more or less restrictive). A semantic model is defined for these polychronous automata, that relies on the Boolean algebra of clocks, and permits to manipulate these automata, without having necessarily to translate them into dataflow equations. In previous works [9, 10], in the aim of virtual prototyping embedded architectures, we defined a compositional semantic translation of AADL specifications into the polychronous model. We now refine this modeling by considering our semantic model of polychronous automata as a formal model for the AADL Behavior Annex.

Our work is motivated by practical reasons such as effective combination of heterogeneous programming notations (including dataflow and automata), and formal validation and virtual prototyping of timed software architectures. Our purpose is not to propose just another extension of an existing programming language. Instead, we focus on the definition of a specific model of automata, specially adapted to the polychronous model of computation, adopted as common semantic model. Such automata have to relate events by expressing and specifying *clock relations* (or clock *constraints*) between these events. For the definition of polychronous automata, the Signal

language is used as syntactic support to express clock equations. Simple examples such as alternating events are used in the first sections of this paper as they are sufficient to illustrate the basics of the model.

In the next section, we first consider some related works, both concerning the introduction of models of automata in synchronous languages, and the use of some formal models to represent and validate AADL models. In Section 3, we recall the main operators of the Signal language and their semantics. Then we define in Section 4 the Boolean control algebra which is used to manipulate clock formulas. In Section 5, we describe the refinement of polychronous programs as automata. In Section 6, we highlight different forms of polychronous automata described as equations on signals. Relying on these requirements in terms of expressivity, we define our model of automata in Section 7. Then, the principles of the semantic translation of AADL in the polychronous model are presented in Section 8. concrete AADL case study, including specifications as automata, is detailed in Section 9 to illustrate formal validation in this modeling framework. Conclusion and future work are drawn in Section 10.

#### 2 Related work

Usual automata have been introduced several years ago in dataflow synchronous languages and are used every day in production tools like SCADE [11]. More generally, there have been many attempts to combine heterogeneous programming models. A major problem addressed in Ptolemy is the use of heterogeneous mixtures of models of computation [12]. So-called Modal Models in particular are hierarchical models where the top level model consists of a finite-state machine, the states of which are refined into other models, possibly from different domains [13]. In our approach, heterogeneous designs are expressed in terms of a common semantics, which is that of the polychronous model of computation. In the software system Matlab/Simulink, which is largely accepted in the industry, the Stateflow notation [14] is used to describe modes in event-driven and continuous systems.

Mode-automata [15] were originally proposed to gather advantages of declarative and imperative approaches to synchronous programming and extend the functional dataflow paradigm of Lustre with the capability to model transition systems. Mode-automata have been combined with stream functions in Lucid Synchrone [16]. Related

<sup>2)</sup> http://www.mathworks.com/products/simulink

forms of hierarchical state machines include Statecharts [17] and their variants, including UML state machines [18], and SyncCharts [19], associated in particular with Esterel and, more recently, SC-Charts [20], based on an improved definition of (sequential) constructivity [21]. DDFCharts [22], which compose finite-state machines and synchronous dataflow graphs, have multiple clocks; transitions can be driven by different clocks and the instants at which clocks synchronize are seen as a rendez-vous communication.

Our approach may be distinguished from the others by its capability to model multi-clocked systems and to express clock relations through the automata. A first attempt was made a few years ago to define polychronous mode automata [23], but compared to our current proposal, it did not allow to manipulate automata as specific objects that can be used, for instance, to specify dynamic properties of events. In its spirit, our approach, which is based on constraint specification relating occurrence of events, is relatively close to that taken for Lutin [24], but with a different purpose. In Lutin, statements describe sequences of non deterministic atomic reactions expressing constraints on input/output values. It is used mainly for test sequence specification and generation. In our proposal, constraints relate values and *clocks* of signals.

Concerning the second contribution of this article, i.e., the use of a formal model (in our case, polychronous automata) to represent and validate AADL behavior specifications, there has been many related works that have contributed to the formal specification, analysis and verification of AADL models and its annexes. We limit ourselves to mentioning here the works which seem to be closest to our approach. In particular, RAMSES [25] presents the implementation of the AADL Behavior Annex. The Behavior Annex supports the specification of automata and sequences of actions to model the behavior of AADL programs and threads. implementation OSATE proceeds by model refinement and can be plugged in with Eclipse-compliant backend tools for analysis or verification. For instance, the RAMSES tool uses OSATE to generate C code for OSs complying the ARINC-653 standard.

Synchronous modeling is central in [26], which presents a formal real-time rewriting logic semantics for a behavioral subset of the AADL. This semantics can be directly executed in Real-Time Maude and provides a synchronous AADL simulator (as well as LTL model-checking). It is implemented by the tool AADL2MAUDE using OSATE.

Similarly, Yang et al. [27] define a formal semantics for an implicitly synchronous subset of the AADL, which includes periodic threads and data port communications. Its operational semantics is formalized as a timed transition system. This framework is used to prove semantics preservation through model transformations from AADL models to the target verification formalism of timed abstract state machine (TASM).

With respect to related works, we also annex the core AADL and its Behavior Annex with formal semantic frameworks to express executable behaviors and temporal properties, but we endeavour in an effort of structuring and using them together within the framework of a more expressive multi-clocked synchronous model. Polychrony would allow us to gain abstraction from the direct specification of executable, synchronous, specification in the AADL, yet offer services to automate the synthesis of such, locally synchronous, executable specification, together with global asynchrony, when or where ever needed.

#### 3 The Signal language

We first introduce the Signal language and its semantics, before to formalize its Boolean control algebra, that is the basis for clock calculus. Signal is a declarative language expressed within the polychronous model of computation. The reader is referred to the bibliography of the Signal language for a detailed description (for instance [28] for an overview, [5,29] for detailed syntax and semantics).

A Signal *process* defines a set of (partially) synchronized *signals* as the composition of equations. A signal x is a finite  $((\exists n \in \mathbb{N})(x = (x_t)_{t \in \mathbb{N}, t \leq n}))$  or infinite  $(x = (x_t)_{t \in \mathbb{N}})$  sequence of typed values in the data domain  $\mathbb{D}_x$ ; the indices in the sequence represent logical discrete time *instants*. At each instant t, a *signal* is either *present* and holds a value v in  $\mathbb{D}_x$ , absent and virtually holds an extra value denoted  $\bot$ , or *completed* and never holds any actual or virtual value for all instants s such that  $t \leq s$ . The set of instants at which a *signal* x is present is represented by its *clock*  $\hat{x}$ . Two signals are *synchronous* iff they have the same clock. Clock constraints result from implicit constraints over signals and explicit constraints over clocks.

The semantics of the full language is deduced from the semantics of a core language, and from the Signal definition of the extended features. A Signal process is either an equation  $x := f(x_1, ..., x_n)$ , where f is a function, or the

composition P|Q of two processes P and Q, or the binding P/x of the signal variable x to the process P. In this section, we give a sketch of its functional part using dataflow models.

Semantic domains. For a set of values of some type  $\mathbb{D}$ , we define its extension  $\mathbb{D}_{\perp} = \mathbb{D} \cup \{\bot\}$ , where  $\bot \notin \mathbb{D}$  denotes the absence of a signal value. The semantics of Signal is defined as least domain fixed point. For a data domain  $\mathbb{D}$ , we consider a poset  $(\mathbb{D}_{\perp} \cup \{\bullet, \#\}, \leqslant)$  such that  $(\mathbb{D}_{\perp}, \leqslant)$  is flat, i.e.,  $x \leqslant y \Rightarrow x = y$ , for all  $x, y \in \mathbb{D}_{\perp}$  ( $\bullet$  and # denote respectively the presence of a signal and the absence of information). We denote by  $\mathbb{D}^{\infty}$  the set of finite and infinite sequences of "values" in  $\mathbb{D}_{\perp}$ . The empty sequence is denoted by  $\epsilon$ . All n-ary functions  $f: (\mathbb{D}^{\infty})^n \to \mathbb{D}^{\infty}$  are defined using the convention of noting s a (possibly empty) signal in  $\mathbb{D}^{\infty}$ , v a value in  $\mathbb{D}$ , x a value in  $\mathbb{D}_{\perp}$ . As usual, |s| is the length of s,  $s_1.s_2$  is the concatenation of  $s_1$  and  $s_2$ .

Given a non empty finite set of signal variables A, a function  $b:A\to\mathbb{D}^\infty$  that associates a sequence b(a) with each variable of  $a\in A$  is named a *behavior* on A. The length |b| of a behavior b on A is the length of the smallest sequence b(a). An *event* on A is a behavior  $b:A\to\mathbb{D}_\perp$ . For a behavior b on a set of signal variables A, and an integer  $i\leqslant |b|$ , b(i) denotes the event e on A such that e(a)=(b(a))(i) for all  $a\in A$ . An event e on A is said to be empty iff  $e(a)=\bot$  for all  $a\in A$ . The concatenation of signals is extended to tuples of signals. Two behaviors  $b_1,b_2$  are *stretch-equivalent* iff they only differ on non-final empty events (see [1] for more details).

Signal functions. A Signal function is a n-ary (with n > 0) function f that is total, strict and continuous over domains [30] (w.r.t. prefix order) and that satisfies:

```

- stretching: f(\bot.s_1, ..., \bot.s_n) = \bot.f(s_1, ..., s_n)

- termination: ((\exists i \in 1, n)(s_i = \epsilon)) \Rightarrow f(s_1, ..., s_n) = \epsilon

```

Stepwise extension. Given n > 0 and a n-ary total function  $f: \mathbb{D}_1 \times \ldots \times \mathbb{D}_n \to \mathbb{D}_{n+1}$ , the stepwise extension of f (e.g., =, and, +, etc.) denoted F is the synchronous function that satisfies:

$$-F(v_1.s_1,...,v_n.s_n) = f(v_1,...,v_n).F(s_1,...,s_n)$$

*Delay.* Function *delay*:  $\mathbb{D} \times \mathbb{D}^{\infty} \to \mathbb{D}^{\infty}$  satisfies:

$-delay(v_1, v_2.s) = v_1.delay(v_2, s)$

The infix syntax of  $delay(v_1, s)$  is: s \$ init  $v_1$ .

*Merge*. Function *default*:  $\mathbb{D}^{\infty} \times \mathbb{D}^{\infty} \to \mathbb{D}^{\infty}$  satisfies:

- $default(v.s_1, x.s_2) = v.default(s_1, s_2)$

- $default(\perp .s_1, x.s_2) = x.default(s_1, s_2)$

The infix syntax of  $default(s_1, s_2)$  is:  $s_1$  default  $s_2$ .

*Sampling*. Let  $\mathbb{B} = \{ff, tt\}$  denote the set of Boolean values. Function *when*:  $\mathbb{D}^{\infty} \times \mathbb{B}^{\infty} \to \mathbb{D}^{\infty}$  satisfies:

- for  $b \in \{\bot, ff\}$ , when $(x.s_1, b.s_2) = \bot$ .when $(s_1, s_2)$

- $-when(x.s_1, tt.s_2) = x.when(s_1, s_2)$

The infix syntax of when  $(s_1, s_2)$  is:  $s_1$  when  $s_2$ .

*Process.* An *equation* is a pair (x, E) denoted x := E. An equation x := E associates with the variable x the sequence resulting from the evaluation of the Signal function f denoted by E (defined as a composition of functions). If  $A = \{x_1, ..., x_n\}$  ( $x \notin A$ ) is the set of the free variables in E, the equation x := E denotes a *process* on A, i.e., a set of behaviors on  $A \cup \{x\}$ ; a process is closed by stretch-equivalence (thanks to the stretching rule).

The parallel composition of equations defines a process by a network of strict continuous functions connected by signal names. Composition of processes is associative, commutative and idempotent. When it satisfies the Kahn conditions (no cycle, single assignment...), it then is a strict continuous function or Kahn Process Network (KPN) [31], defined as least upper bound satisfying the equations. It further satisfies the termination and stretching properties (it is closed for the stretching relation). It may or may not be synchronous. In the semantics of Signal [1], a process is the set of infinite behaviors accepted by the above "KPN semantics".

A process with feedback or local variables may be not time-deterministic. The semantics of a non deterministic process can be defined using Plotkin's power-domain construction [32]. The input-free equation x := x init 0 is a typical example of not timely deterministic process: x holds a sequence of constant value 0 separated by an undetermined number of silent transitions, characterized by an occurrence of  $\bot$ .

An example of non deterministic process is the equation x := E, that defines x to be equal to E when E is present and undefined when E is  $\bot$  (partial definition). This equation is a shortcut for x := E default x. A signal x can be constructively defined by several equations  $x := E1, \ldots, x$  ::= En in a process, provided that for every pair of equations x := Ei, x := Ej, when Ei and Ej are both present, they hold the same value. If  $E1, \ldots, En$  do not recursively refer to x and if they denote functions, then ( $x := E1 \mid \ldots \mid x := En$ ) is a deterministic process.

Partial definitions are very useful in automata where the function that computes the value of a signal often depends on current state. The states being exclusive, the consistency property is satisfied. Partial definitions are used also to

define *state variables* the elements of which are present as frequently as necessary. When such a state variable is not explicitly defined, it keeps its previous value.

*Derived operators.* The following notations (which are derived operators) are used to manipulate clocks, represented as signals of type event, always *true* if and only if present.

- null clock ^0 (never present)

- signal clock ^x, defined by x = x (present, and true, when x is present)

- *selection* ~b (a.k.a. [b] or [:b]), defined by ^b when b (present, and *true*, when b is present and is *true*)

- intersection x1 ^\* x2, defined by ^x1 when ^x2

- union x1 ^+ x2, defined by ^x1 default ^x2

- difference x1 ^- x2, defined by [(not ^x2) default ^x1]

- synchronization x1 ^= x2, defined as (c := (^x1 = ^x2))/c

Note that, in the syntax, the hat notation appears just before the symbol or variable it applies to: for instance, "^\*" is a syntactic representation of "\*" (see below).

A synchronized memory y := x cell c init x0 is defined by the composition of y := x default (y \$ init x0) and  $y ^= x ^+ [c]$ . It defines y with the most recent value of x when x is present or c is present and true. Finally, the Signal term 11 :: P associates the label 11 with the process P; a label 11 is a signal of type event. Its clock is the tick of the labeled process, P (i.e., the upper bound of all the clocks in P).

#### 4 Boolean control algebra

We define the syntax and set the axioms of the Boolean control algebra, taking into account *state variables* used to represent states of the automata.

**Definition 1** Considering V a (possibly empty) countable set of signal variables, S a non empty finite set of state variables with  $S \cap V = \emptyset$ , a *Boolean control algebra*  $\Phi(V, S)$  is a tuple  $(F_{VS}, \hat{*}, \hat{+}, \hat{-}, \neg, 0, \mathbf{1}_{V})$ , where:

- \(\hat{\*}\), \(\hat{+}\) designate meet (infimum) and join (supremum);

- $\mathbf{0}$ ,  $\mathbf{1}_{V}$  are the minimum and maximum.

The set of control Boolean formulas  $F_{V,S}$  is the smallest set that satisfies:

- constants  $\mathbf{0}, \mathbf{1}_{V} \in F_{V,S}$ ;

- atoms  $\forall x \in V \cup S$ ,  $\hat{x}$ ,  $\widetilde{x} \in F_{V,S}$ ;

- unary expressions  $\forall f \in F_{V,S}, \neg f \in F_{V,S}$ ;

binary expressions ∀f, g ∈ F<sub>V,S</sub>, +fg, \*fg, -fg ∈ F<sub>V,S</sub>.

Parentheses and infix notations can be used in the formulas.

The formula  $\widehat{x}$  designates the *clock* of a variable x. The formulas satisfy Boolean axioms:  $(F_{V,S}, \hat{*}, \hat{+}, \neg, \mathbf{0}, \mathbf{1}_v)$  is a Boolean algebra. The following supplementary axioms are also considered.

- difference  $f g = f * \neg g$ ;

- partition  $\forall x \in V \cup S$ ,  $\widehat{x} = \widetilde{x} + \neg \widetilde{x}$  and  $\widetilde{x} * \neg \widetilde{x} = \mathbf{0}$ ;

- exclusion  $\forall s1, s2 \in S$ ,  $\widetilde{s1} * \widetilde{s2} = \mathbf{0}$  or s1 = s2;

- $1_0 = 0$ .

The clock of an automaton with a non-empty V is defined by  $\sum_{x \in V} (\widetilde{x} + \neg \widetilde{x}) = \mathbf{1}_{v}$ , and  $\forall s \in S$ ,  $\widehat{s} = \mathbf{1}_{v}$ . Formulas in the Boolean control algebra have normal forms: Shannon disjunctive forms (given an arbitrary total order on variables).

Note that, independently of state variables which are distinguished here, this Boolean control algebra is that of the standard polychronous model of computation. The formal tools which are based on this control algebra, such as the *clock calculus* (which builds a *clock hierarchy*), still apply exactly in the same way when automata are considered. In both contexts, timing analysis mainly refers to analyzing clock relations based on clock hierarchy.

Clock hierarchy. The clock hierarchy of a process is a component of its Data Control Graph (DCG). The DCG is made of a multigraph G and a clock system  $\Sigma$ . We refer to [28] for a more complete description. A clock equation is a class of equivalent clock formulas. The clock system  $\Sigma$  is a forest (set of trees) of clock equations: this is why it is called clock hierarchy. The clock hierarchy is defined by a relation  $\hat{\setminus}$  (dominates) on the quotient set of signals by  $\hat{\ }$  = (x and y are in the same class iff they are synchronous). Informally, a class C dominates a class D if the clock of D is computed as a function of Boolean signals belonging to C and/or to classes recursively dominated by C. A node n of a tree, which is a clock equation, contains also the list of signals signal(n) the clock of which is equal to this class. A tree represents an endochronous process: it has a fastest rated clock and the status (presence/absence) of all signals is a pure flow function (this status depends neither on communication delays, nor on computing latencies).

The equational nature of the Signal language is a fundamental characteristic that makes it possible to consider the compilation of programs as an endomorphism over Signal programs. We have mentioned a few properties allowing to rewrite programs with rules such as commutativity and associativity of parallel composition.

More generally, until the very final steps of code generation (when code generation is an objective), the compilation process may be seen as a sequence of morphisms allowing to rewrite programs as transformed Signal programs. The final steps (C code generation for instance) are simple morphisms over the transformed Signal programs. These transformation steps, to sequential, clustered, or distributed code generation, are described in [28].

#### 5 Refinement of processes as automata

So far, contrary to what is done for other synchronous languages, including dataflow ones like Lustre (see for instance [33]), no explicit representation of automata was directly produced in the compilation of Signal programs, either for code generation purpose, or as input to formal verification tools. In this section, we propose a method for deriving an automaton from a polychronous program, which relies heavily on the concept of clock.

A given Signal program may be seen as an automaton which contains one single state and one single transition, labeled by a clock. This clock is the upper bound of all the clocks of the program (the *tick* of the program).

The construction of a refined automaton from a Signal program will be based on delayed signals, viewed as state variables (in particular Boolean ones). A state of the automaton is a Signal program with some valuation of its state variables. Transitions are labeled by clocks, which represent the events that fire these transitions. The principle of the construction consists in dividing a given state according to the possible values of a state variable (i.e., true and false for Boolean state variables, which are considered here) in order to get two states, and thus two new Signal programs. Each one of these two states is obtained using a rewriting of the starting program. Moreover, the absence of value for the state variable (which can be considered as another possible value) is taken into account in the clocks labeling the transitions. The construction of the automaton is a hierarchic process.

Figure 1 illustrates the first step of the construction. Initially, the automaton A has one single state, which is the Signal program P, with one transition, labeled by the tick k of P. The construction is started with the valuation of a first state variable, s, in the program P, respectively with true and false, which gives two new programs,  $P_1$  and  $P_2$ . The new programs are obtained by rewriting the previous one, taking into account the considered valuation. This rewriting results

**Figure 1** Refinement of state s in P by the automaton  $A_1 = (P_1, P_2)$

generally in simplifications of the programs. The resulting automaton,  $A_1$ , now contains two states,  $P_1$  and  $P_2$ . The calculus of the transitions consists in computing the clocks of the events that cause a change of state. The transition from  $P_1$  to  $P_2$  occurs when the state variable s, which was true, becomes false; thus the corresponding clock is  $\neg \widetilde{s}$ . Conversely, the transition from  $P_2$  to  $P_1$  occurs at the clock  $\widetilde{s}$ . The transition from  $P_1$  to itself is labeled by the clock k, minus the instants at which there is a transition from  $P_1$  to  $P_2$  (and the same reasoning for  $P_2$ ). Note that the transitions are not instantaneous. When a clock raising a change of state is present at a given instant, the effective change of state of the automaton takes place at the following instant (with respect to the tick).

The construction of the automaton is an iterative process, by successive valuation of its state variables,  $s_1$ ,  $s_2$ , etc. For instance, the second step would introduce new states,  $P_{11}$  and  $P_{12}$  from  $P_1$ , by discriminating it according to the value of a second variable  $s_2$ . One could, equivalently, introduce two other states from  $P_2$ . Now, at any refinement step n > 1, one could then potentially define  $2^n$  states by iterating the refinement of all sub-processes  $P_i^{n-1}$ , of clocks  $k_i^{n-1}$  and indices  $0 < i \le 2^{n-1}$  obtained from step n - 1, by partitioning them according to an nth state variable  $s_n$  and by using the same mechanism, Figure 2.

**Figure 2** Refinement of state  $s_n$  in  $P_i^{n-1}$  by the automaton  $(P_{i1}^n, P_{i2}^n)$

This would seem to be an expensive construction, at least in the worst case, in the size of the explicit automaton being an exponential of its number of state variables. Fortunately, however, all Signal programs have a clock hierarchy, defined from the dominance relation introduced in Section 4, which is used to represent the control flow of the program in a much more efficient way (and actually optimal, as

hierarchies can be normalised and admit a canonical representation). Concretely, most of the  $2^n$  are in practice inaccessible, because of dominance (of a state value by a clock).

Example. Let's for instance consider a Signal program with two state variables  $s_1$  and  $s_2$  such that  $s_2$  is not defined when  $s_1$  is false, i.e.,  $s_2$  ^= when  $s_1$ . In other words,  $s_1$  has a higher frequency than  $s_2$ , and in the built clock hierarchy, the clock of  $s_1$  dominates  $s_2$ . If we construct its automaton as in figure 2, evaluating  $s_1$  first,  $s_2$  second, we would obtain four sub-processes  $P_{11,12,21,22}^2$  from  $P_1^1$  and  $P_2^1$ . However, partitioning  $P_2^1$  into  $P_{21,22}^2$  is useless, since  $s_2$  is not present when  $s_1$  is false.

It may further be observed that, when constructing the automaton, the order in which state variables are valuated has an influence on the number of states of the automaton. Our choice is to therefore base this order on the clock hierarchy of the Signal program, using a pre-order depth-first traversal. In this way, more frequent state variables are evaluated before less frequent ones. Note also that when some state variable is valuated, the corresponding program is rewritten, using in particular constant propagation. This results generally in many simplifications, since a number of clocks may become null, thus eliminating corresponding variables.

#### 6 Automaton description in Signal equations

Of particular interest from the previous example is that, in the polychronous framework, the behavior of an automaton may be either reactive, with respect to its environment or context, or restrictive: constrained by clock relations. In the case of a reactive automaton, events from the environment are free to occur at their own rate. The automaton registers the occurrences of these events and makes its state evolve according to these occurrences. In the case of a restrictive automaton, the automaton enforces constraints on the events that can occur. Events that are not explicitly allowed in some state are forbidden: this has an effect on the environment which is, in some way controlled by the automaton.

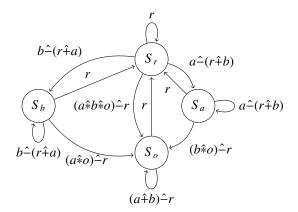

This can be illustrated on an automaton alternating two events, a and b. Figure 3, events a and b are *constrained* to alternate by the clock relation  $a \cdot b = 0$ , which imposes that they cannot happen simultaneously (the intersection of clocks a and b is never present). It should further be assumed also that b cannot occur in  $S_1$  and a cannot occur in  $S_2$ . It can be

noticed that the occurrences of a and b are always controlled (or constrained), and control is state dependent.

Figure 3 A restrictive behavior

Such an automaton can also be expressed by constraining a and b to occur in either of the automaton states s.

```

s := not (s \$ init false) | a ^= [s] | b ^= [not s]

```

A *reactive* behavior, as in Lustre or Esterel, is different. Events a and b are free to occur at any time. An Esterel or a Lustre program does not "control" the delivery of its input signals. A reactive automaton will observe and record the alternating occurrences of a and b, Figure 4, it will not enforce them.

Figure 4 A reactive behavior

In Signal, the observer will be implemented using a couple of equations that monitor alternation using a state variable change and stuttering using another wait.

A resettable Esterel program like the famous ABRO is an object which falls in between constrained and reactive behaviors: it emits an output o immediately after receiving both inputs a and b. It is reset when r occurs. So, signal o is controlled, while others aren't.

```

module ABRO:

input a, b, r;

output o;

loop

[ await a || await b ];

emit o

each r

end module

```

The automaton for the ABRO is represented Figure 5, where transitions are labeled by Signal clock expressions.

An equational definition of the ABRO may be specified as follows in Signal, using a state variable for representing the expectation of a and b:

Figure 5 Automaton for ABRO

```

sa := ((false when r) default a) cell b init false

| sb := ((false when r) default b) cell a init false

| wait := r default (false when o) default waiting

| waiting := wait $ init true

| o := [waiting] when (sa and sb)

```

In the ABRO program, the inputs a, b, r are never controlled, and the output o is obviously controlled. However, in Signal, it is worth noting that controlled variables are not limited to output signals.

#### 7 Explicit structure of polychronous automata

Although it is always possible to represent automata by systems of equations, equations are clearly not always the most natural way to represent them. Moreover, in a model-driven engineering context, it is better suited to explicitly represent user-specified and automatically automata to maintain high-level semantic generated the traceability of model properties as well as We have hence chosen light-weight transformations. syntactic extensions to the Signal language in order to introduce explicit representations of automata.

We add a new syntactic category of *process*, called automaton. In such an automaton process, labeled processes represent states, and generic processes such as Transition are used to represent the automaton features. Usual equations can be used in these automaton processes to specify constraints or to define computations. Then comes the question of whether these automata should be only a syntactic structure (in such a way that they would be systematically translated as ordinary equations on signals when compiled), or whether they should be reflected in the polychronous formal model itself. This latter choice has the

advantage of allowing a formal manipulation of automata (which may be, or not, translated as equations). For instance, it may be the case that a given behavior is best abstracted as an interface automaton than as a system of clock equations which would require to make explicit some hidden Boolean variables. It is therefore desirable to define a model of "polychronous automata" allowing a possible smooth integration within the polychronous model.

A basic statement for the definition of our automata is that state change takes time. It is also assumed in [15], [16], or in SCADE 6. In this way, there is a single state at each logical instant and there is no immediate transition. Such automata should be used to schedule steps, not actions in a step. This drives towards simplicity and is also suitable for high-level mode modeling in an application. polychronous framework, transitions will be labeled by clock (or event) expressions named triggers and a state is implicitly exited on the upper bound of its triggers. An automaton is *clocked*: it is controllable by an external clock, its *control clock*. There are several possible interpretations of a given automaton: in a permissive view, all non forbidden events are allowed in states; while in a restrictive one, all non allowed events are forbidden in states. By default, we adopt the permissive hypothesis.

#### 7.1 Notations for polychronous automata

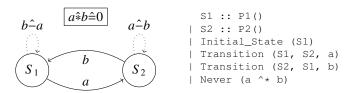

To make things concrete, let us write a syntactic representation of the automaton in Fig. 6. This simple automaton has two external events, a and b, and its control clock is, implicitly, the upper bound, a ^+ b of the clocks of its inputs. The two states, S1 and S2, are designated by labels, associated here with empty processes. The statement Never (a ^\* b) represents the *constraint* of the automaton. This constraint, which must always be respected, can be expressed by a clock formula that is constrained to be null: here, a ^\* b ^= ^0, expressed as Never (a ^\* b). Such constraints can always be expressed as a conjunction of Never formulas (which can also be specified as one single Never statement with several parameters) or of explicit synchronizations like Synchro (x, y) (with Synchro (x, y) defined as Never (x - y, y - x). In this small automaton with two states and two explicit transitions, the initial state is S1. We will see below that there are also implicit transitions.

Let us state some vocabulary and notations. For a transition T = Transition (S1, S2, h), S1 is the source of T, S2 is the target of T, h is the trigger of T, denoted trig-

ger(T), and a trigger in S1; h is a clock expression, that may represent, for instance, a conjunction of events (e.g., a  $^*$  b represents the conjunction of events a and b). The transition T is *enabled* at k iff (k  $^*$  h) is not null and the current state is S1.

Figure 6 Polychronous automaton (with implicit stuttering loops)

A *step* is defined as being an implicit not exiting reflexive (e.g. stuttering) transition. A step S1--h->>S1 is *enabled* at k iff (k \* h) is not null, current state is S1 and there is no enabled transition. All steps that are not explicitly forbidden are allowed. In the example of Fig. 6, S1 -- b^-a ->> S1 and S2 -- a^-b ->> S2 are steps (they appear as dotted transitions). Steps allow for "stuttering" when there is no enabled transition. For a state S, exiting on (one of the) enabled transitions is mandatory. A formal model of constrained automata, consistent with the polychronous framework, is proposed in the next section.

#### 7.2 Formal definition

For an automaton A of signal variables  $V_A$  and states  $S_A$ , we denote by  $F_{A,S}$  the set of *normal form* formulas in the Boolean control algebra  $\Phi(V_A, S_A)$  (cf. Section 4).

**Definition 2** A polychronous automaton A is an epsilon-free automaton defined up to isomorphism (over states) as a tuple  $A = (S_A, s_0, R_A, V_A, T_A, C_A)$  where:

- $S_A$  is the non empty finite set of states;

- $s_0$  is the initial state;

- $R_A \subset S_A \times S_A$  is the transition relation;

- $V_A$  is the, possibly empty, finite set of signal variables;

- $T_A: (R_A) \to F_{A,S}$  is the function that assigns a formula to a transition;

- C<sub>A</sub> is the *constraint* of A: it is a formula in F<sub>A,S</sub> that is (constrained to be) null (thus a formula f in F<sub>A,S</sub> is null in A iff f \* C<sub>A</sub> = f).

*Remarks*. A transition in  $T_A$  carries a formula in the Boolean control algebra that represents its trigger. Polychronous automata are subject to clock constraints  $C_A$  which are expressed by a formula in the Boolean control algebra. If  $C_A$  is  $\mathbf{0}$ , then the automaton is *constraint-free*; if  $C_A$  is  $\mathbf{1}_{V_A}$  (i.e., the

supremum of the algebra is constrained to be null), all formulas are null. The notation  $1_A$  is used to denote the supremum  $1_{V_A}$ .

An automaton with an empty set of transitions is  $\mathbb{O}_V = (\{s\}, s, \emptyset, V, \emptyset, \mathbf{1}_V)$ , which blocks all occurrences of all variables of V. The automaton with an empty set of variables is  $\mathbb{I} = \mathbb{I}_{\emptyset} = (\{s\}, s, \emptyset, \emptyset, \emptyset, \mathbf{0})$ ; it is equal to  $\mathbb{O}_{\emptyset} = (\{s\}, s, \emptyset, \emptyset, \emptyset, \mathbf{1}_{\emptyset})$ .

*Example.* The automaton in Fig. 6 is defined by  $A = (S_A, s_0, R_A, V_A, T_A, C_A)$  with

- $S_A: \{S_1, S_2\}$

- $s_0: S_1$

- $R_A$ : { $(S_1, S_2), (S_2, S_1)$ }

- $V_A : \{a, b\}$

- $T_A: (S_1, S_2) \mapsto a, (S_2, S_1) \mapsto b$

- $C_A: a \hat{*} b \hat{+} \neg \widetilde{a} \hat{+} \neg \widetilde{b}$

$(a, b \text{ are events thus } \neg \widetilde{a}, \neg \widetilde{b} \text{ should be null}).$

A labeled transition is denoted by " $h: s_1R_As_2$ " meaning that  $((s_1, s_2) \in R_A \text{ and } T_A((s_1, s_2)) = h)$ .

#### 7.3 Properties

Now notions introduced previously can be formalized:

- The *control clock* of an automaton *A* is  $1_A (= \sum_{x \in V_A} \widehat{(x)})$ , the supremum of the clocks of its variables.

- In  $h: s_1R_As_2$ , h is the trigger of  $(s_1, s_2)$  and a trigger in  $s_1$ .

- The *trigger* of a state s,  $trigger_A(s)$ , is the upper bound of the triggers of (s, \*), where (s, \*) stands for all the transitions outgoing from s.

Then it is possible to define the *stuttering clock* of a state as the clock difference between the control clock of the automaton and the trigger of the state (plus the null clock of the state,  $C_A(s) = \tilde{s} * C_A$ ): the *stuttering clock* of a state s is  $\tau(s) = 1_A - (C_A(s) + trigger_A(s))$ . Hence the definition of implicit transitions: when the stuttering clock  $\tau(s)$  of a state s is not null, there is a silent implicit transition  $\tau(s) : sR_As$  named step. Usual properties of automata can be easily extended to polychronous automata:

- A state t is n-reachable in A iff s<sub>0</sub> and t are not null and either

- n = 0 and  $t = s_0$ ,

- -n > 0 and t is (n-1)-reachable in A,

- n > 0 and  $(\exists s \ (n-1)$ -reachable in A)  $(\exists h)(h \hat{*} \tilde{s} \text{ not null})(h : sR_A t)$ .

- A state t is reachable in A iff it is  $|S_A|$ -reachable in A.

- A state s is *deterministic* if the triggers of its transitions are mutually exclusive: formally, s is determin-

istic iff  $(\forall ((s, s_1), (s, s_2)) \in R_A \times R_A)((s_1 = s_2) \vee (T_A((s, s_1)) \hat{*} T_A((s, s_2)) = \mathbf{0})).$

- An automaton is *deterministic* iff all its reachable states are deterministic.

- A state *s* is *total* (or *reactive*) iff  $\tau(s) + (\Sigma_{(s,t) \in R_A}(trigger_A((s,t)))) = 1_A$ .

- An automaton is total (or reactive) iff all its states are total (we observe that if C<sub>A</sub> is not 0 then A is not reactive).

#### 7.4 Polychronous automata algebra

Just like the synchronous composition, the composition (or synchronous product) of polychronous automata corresponds to the conjunction of the behaviors specified by each of them.

**Definition 3** Let  $A = (S_A, s_0, R_A, V_A, T_A, C_A)$  and  $B = (S_B, t_0, R_B, V_B, T_B, C_B)$  two polychronous automata, their composition is defined by  $AB = A|B = (S_{AB}, (s_0, t_0), R_{AB}, V_{AB}, T_{AB}, C_{AB})$ , where:

- $\bullet \ \ S_{AB} = S_A \times S_B,$

- $R_{AB} = \{((s_1, t_1), (s_2, t_2)) | ((s_1, s_2), (t_1, t_2)) \in R_A \times R_B \},$

- $\bullet \ \ V_{AB}=V_A\cup V_B,$

- $(\forall st = ((s_1, t_1), (s_2, t_2)) \in R_{AB}) (T_{AB}(st) = T_{AB}((s_1, t_1)) \hat{*} T_{AB}((s_2, t_2))),$

- $\bullet \ \ C_{AB}=C_A + C_B.$

Note that the constraint of the composed automaton (its null formula  $C_{AB}$ ) is defined by the clock union of the constraints of the operand automata.

**Theorem 1** The composition of polychronous constrained automata has the following properties:

- if A is deterministic, A|A = A, it is idempotent;

- it is commutative;

- it has a neutral element  $\mathbb{I} = (\{s\}, s, \emptyset, \emptyset, \emptyset, \emptyset)$ ;

- it is associative.

Idempotence for deterministic automata can be proved using induction on *n*-reachability of states. Associativity can be proved by induction on *n*-prefix automata (the states of a *n*-prefix automaton of an automaton *A* are the *n*-reachable states of *A*). Associativity corresponds to context independence and commutativity to order independence.

#### 7.5 Discussion

The added value provided by the formal model of the polychronous automata is to allow for a smooth integration of automata into the polychronous model of computation of the Signal dataflow language. They have not necessarily to be translated by systems of equations on signals, although such a translation is, of course, possible. Note that using such a translation, semantics of polychronous automata reduce to semantics of standard polychronous programs. Comparable translations have been studied in previous works, such as [16] for example (it is not our purpose here to describe another translation that would not be so different). We have defined a parallel composition (synchronous composition) of polychronous automata. A classical extension of finite automata is also that of *hierarchical automata*, in which states may be non atomic. Here, this can be handled quite simply in the context of the Signal language. It is not detailed in this article since it does not present new challenges with respect to previous works.

Just like labels are syntactically associated with states, labels can also be associated with transitions, and these labels can be used as clocks. The label of a transition is an event signal (a clock), which is *true* (present) when this transition is fired. Actions associated with an automaton can be expressed as polychronous equations (in our case, in Signal), that are composed with the constraints of the automaton. They may use specific events associated with the automaton, such as labels of transitions, but also other typical events such as entering or exiting a given state, etc. For example, let  $\pm 1$  and  $\pm 2$  be labels associated with two transitions in a given automaton, then the equation  $\circ := \pm 1$   $^+ \pm 2$  expresses the action of emitting an event  $\circ$  as soon as one of these transitions is fired.

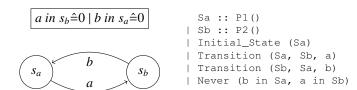

A further remark can be made on permissive versus restrictive interpretation (recall permissive is the default one). The transformation of a given automaton from a permissive interpretation to a restrictive one is obtained as follows by *disabling its steps*. Given a (permissive) automaton A, the high level operation "strong A" consists in adding the following constraint for every state s in A:  $(1_A - trigger_A(s)) * \tilde{s} = 0$ . For an event h and a clock h, let us write (in a more readable way) "h in h" the clock h \* [S]. Consider as example the h automaton represented in Fig. 6. Defining "automaton alternate = strong h" adds to h the constraints h0 and h1 in h2 h1 on h2 h3 in h4 h5 h6 h7 in h9 h9. Applying constraint reduction, we get the automaton represented in Fig. 7.

Figure 7 "alternate" automaton

#### 8 Polychronous AADL modeling

In previous sections, we have introduced a model of polychronous automata in the polychronous model of computation. This polychronous MoC has been used previously as semantic model for systems described in the core AADL standard. The core AADL is extended with annexes, such as the Behavior Annex, which allows to specify more precisely architectural behaviors. The translation from AADL specifications into the polychronous model should take into account these behavior specifications, which are based on description of automata. In this section, we first describe the principles of a compositional semantic translation of AADL specifications into the polychronous model.

#### 8.1 A short introduction to AADL

AADL is a SAE (Society of Automotive Engineers) standard, dedicated to modeling embedded real-time system architectures. It describes the structure of systems as an assembly of software components allocated on execution platform components together with timing constraints.

*Architecture.* Three families of components are provided in AADL:

- software application components, which include process, thread, thread group, subprogram, and data components;

- execution platform components, which include processor, virtual processor, memory, device, bus, and virtual bus components;

- composite components, which describe systems containing execution platform, application software, or other composite components.

Each component has a type, which represents the functional interface of the component and externally observable attributes. Each type may be associated with zero, one or more implementation(s) that describe the contents of the component, as well as the connections between components. The

components communicate via data ports, event ports, and event data ports.

11

Properties. AADL properties provide information about model elements of an AADL specification. For example, a property Dispatch\_Protocol is used to describe the dispatch type of a thread. Property associations in component declarations assign a particular property value (e.g., Periodic) to a particular property (e.g., Dispatch\_Protocol) for a particular component. Timing properties associated with threads, such as Input\_Time or Output\_Time of ports, assure an input-compute-output model of thread execution. Binding properties assign hardware platform to the execution of application components.

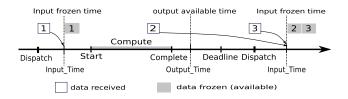

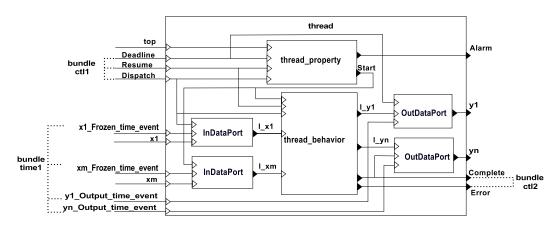

AADL timing execution model. Threads are dispatched either periodically, or by the arrival of data or events on ports, or by the arrival of subprogram calls from other threads, depending on the thread type. Three event ports are predeclared: dispatch, complete and error (Figure 8). A thread is activated

Figure 8 Execution time model for an AADL thread

to perform the computation at *start* time, and has to be finished before *deadline*. A *complete* event is sent at the end of the execution. The received inputs are frozen at a specified point (*Input\_Time*), by default the *dispatch* time, which means that the content of the port does not change during the execution of a dispatch, even though the sender may send new values. For example, the values 2 and 3 (Figure 8) arriving after the first *Input\_Time* will not be processed until the next *Input\_Time*. As a result, the performed computation is not affected by a new input arrival until an explicit request for input. Similarly, the output is made available to other components at a specified point of *Output\_Time*, by default at *complete* (resp., *deadline*) time if the associated port connection is immediate (resp., delayed) communication.

*Behavior*. The Behavior Annex provides an extension to AADL core standard so that complementary behavior specifications can be attached to AADL components. The behavior is described with a state transition system equipped with guards and actions.

#### 8.2 AADL modeling

#### 8.2.1 AADL time model in Polychrony

The key idea for modeling the computing latency and communication delay in Signal is to keep the ideal view of instantaneous computations and communications, while delegating computing latency and communication delays to specific "memory" processes, that introduce delay and well-suited synchronizations to timed signals.

A "memory" process  $o = f_m(i, b)$  is used to repeat the input signal i on the instants of a Boolean signal b. The result o contains values of i when i is present and b is true, and the last value of i when i is absent and b is true:

$$\begin{aligned} o &= f_m(i,b) \equiv \\ \forall t > 0: \quad o_t &= \begin{cases} i_t & \text{if } i_t \neq \bot, \text{ and } b_t = true \\ i_{pred(t)} & \text{if } i_t = \bot, \text{ and } b_t = true, \\ pred(t) &= max\{k < t \mid o_k \neq \bot\} \\ \bot & \text{otherwise} \end{cases}$$

Input freezing. Let f(x) represent the result of the behavior f of a given in port on its input signal x (e.g., f can be a FIFO to represent queued event or event data port). A port y = f(x) gives the available output y from the currently received input x:

$$y = f(x) \equiv \forall t > 0 : (x_t \neq \bot \Leftrightarrow f(x_t) \neq \bot) \land (y_t = f(x_t)))$$

The freezing of x at t, denoted here  $x \triangleright t$ , is a function that takes an input x, a frozen time event t, and produces a new signal z at time t:

$$z = x \triangleright t \equiv z = f_m(f(x), t)$$

Thread activation. We use  $th(z_1, z_2, ...)$  to represent the original computation of a thread th with frozen inputs  $z_1, z_2, ...$  An activation condition *start* is introduced so that the thread th is activated to perform computation at *start*. This is denoted as  $th'(z_1, z_2, ..., start)$ , where the inputs  $z_1, z_2, ...$  are memorized at *start*:

$$th'(z_1, z_2, \dots, start) \equiv th(z_1', z_2', \dots)$$

where  $\forall i, z_i' = f_m(z_i, start)$

Output sending. Like for *in* ports, let g(y) represent the behavior of an *out* port. The sending function, denoted here y > t, is such that the generated output of g(y) is hold and sent out at time t:

$$w = y \triangleright t \equiv w = f_m(g(y), t)$$

#### 8.2.2 Compositional transformation

The translation from AADL to Signal is recursive. A package, which represents the root of an AADL specification, is transformed into a Signal module, the root of a Signal program, allowing to describe an application in a modular way. The rest of the transformation proceeds modularly by an inductive translation of the AADL concepts of a given model or source text. Each AADL component implementation is translated into a Signal process composed of the following elements:

- an interface consisting of input/output signals translated from the features (ports) provided by the component type,

- additional control signals, that may also be added depending on the component category (*Dispatch* and *Deadline* for a thread),

- a body, itself composed of subcomponents, subprogram call sequences, connections, component properties and a transition system specifying the functional behavior.

Threads. Let us sketch the principles of the translation of threads, which are the main executable and schedulable components. The six types of threads (periodic, aperiodic, sporadic, timed, hybrid, background) are discriminated by the dispatch: a dispatch request is periodic, or is triggered by an event (or event data) arriving, etc. The different threads are implemented in the same way, but the "dispatch" signal is generated differently.

An AADL thread component is implemented as a Signal process (Figure 9): it is composed of processes that represent its behavior, property, ports and subcomponents. *Dispatch, Complete* and *Error* are predeclared ports in AADL. They are represented as input/output signals (Dispatch, Complete, Error). According to the AADL semantics, the signals Resume and Deadline are added as inputs, which are generated by the scheduler. Start is represented as the first Resume after a Dispatch signal. It is computed in the xx\_Thread\_property subprocess. The event signals (x1\_Frozen\_time\_event, y1\_Output\_time\_event...) are represented as input signals, which are produced by the scheduler.

Figure 9 Thread modeling

The translation (as polychronous automata) of the transition system that provides the functional behavior of the thread will be illustrated on the case study described in Section 9.

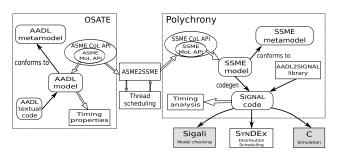

#### 8.3 Complete toolchain

A global view of the toolchain for modeling, timing analysis and verification of the AADL models in the polychronous MoC is given in Figure 10.

Figure 10 A global view of the AADL to Signal toolchain

The AADL model, which conforms to the AADL meta-

model, is captured as AADL textual code in the OSATE toolkit [34]. The timing properties provide detailed timing specifications related to the AADL model. A model transformation toolchain, ASME2SSME, performs analyses on the ASME models (AADL Syntax Model under Eclipse) and generate Signal models in SSME (Signal Syntax Model under Eclipse). The SSME models can be transformed to Signal textual code within Polychrony.

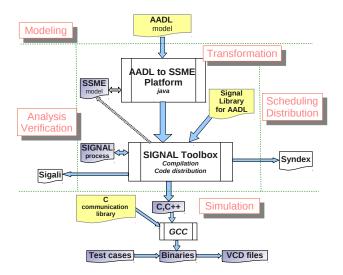

An AADL2SIGNAL library provides common Signal processes reducing significantly the transformation cost. The timing properties represented as Signal clocks are calculated and analyzed in the compilation of Signal programs. Then, executable code can be generated for simulation. Associated tools, such as Sigali [35] and SynDEx [36], can be used for further verification and validation. The global architecture, in the context of Polychrony, is represented in Figure 11.

Figure 11 Global architecture

#### 9 Case study: an Adaptive Cruise Control System

In this section, we present the ADDL modeling of an Adaptive Cruise Control (ACC) system, a highly safety-critical system embedded in recent cars, and we show how polychronous automata allow to verify properties over such an heterogeneous system.

#### 9.1 Adaptive Cruise Control systems

Adaptive Cruise Control systems are embedded systems in cars. They get information from different sensors and can act on the speed of the vehicle, notably in the case of a risk of collision. As such, ACC systems are safety-critical systems, needing for careful design and verification.

An Adaptive Cruise Control System is an optional cruise control system for road vehicles that automatically adjusts the vehicle speed to maintain a safe distance from vehicles ahead. [...] Control is imposed based on sensor information from onboard sensors [37].

ACC systems pursue two main goals: automatically follow a preset speed (as a classical Cruise Control system), improving comfort of the driver, reducing fatigue and preventing subconsciously violating speed limits; and adapt the vehicle speed to maintain safe distance from vehicle ahead and prevent collisions.

For this, an ACC system gets information from different sensors: speedometer, lidar/radar to detect vehicles or obstacles ahead, and wheel sensor to adjust the position of the lidar/radar. It also gets information from the driver through buttons allowing to set the preferred speed and to activate/deactivate the system. Depending on the situation (presence of an obstacle or not, activation of the cruise control or not), it computes the acceleration/deceleration for the vehicle to reach the needed speed: the preferred speed of the driver if there is no obstacle and the cruise control is on, or the speed of the vehicle ahead if one is detected. Finally, it acts on the vehicle speed through its brakes and throttle.

ACC systems are thus highly safety-critical systems which have to satisfy multiple requirements linked to multiple perspectives:

• from the timing and scheduling perspective, all threads must meet their deadlines and the overall task of reacting

- to the presence or absence of an obstacle must meet a maximum reaction time;

- from the logical perspective, the system must be free of deadlock and race condition;

- from the security perspective, critical software components (processes or systems) must be protected from less critical components, thus executed on dedicated processors;

- from the consumption perspective, the system must draw minimal power from the car battery, thus processors must run on the minimal possible frequency;

- from the cost perspective, the overall cost of the system should be minimal, which means minimizing hardware component size and complexity.

All these requirements interact in many ways, and thus cannot only be checked on a subset of the system. Minimizing hardware components size and processors frequency to reduce construction costs and consumption of the vehicle will affect execution time and scheduling of the different tasks (e.g., less powerful processor will take more time to execute a task and smaller or slower buses will slow data communication). In the same way, changing a processor by another to reduce costs, may lead to impossible bindings between processes and processors (e.g., some embedded processors may be unable to execute complex operations).

To analyze collectively all these requirements, and ensure that choices made in order to satisfy one requirement does not break another (i.e., that the set of requirements is consistent), the full system must be analyzed at once.

AADL model of the ACC system can be transformed into a Signal program, where behavior is described through polychronous automata and properties are used as constraints over the system. It is then possible to use the Polychrony framework to analyze and schedule the system. The Polychrony framework targets the two first perspectives presented above: time and scheduling, and logical perspectives. Requirements depending on other perspectives should be addressed using complementary analyzes.

#### 9.2 AADL modeling of the Adaptive Cruise Control system

In the following, we present the modeling of a simplified ACC system using AADL. AADL provides a combination of visual and textual modeling: we use the visual representation for the overview of the system and details about connections, communications, and behavior automata, and we use the textual representation for details about requirements and

properties such as types, numbered or enumerated properties and about behavior actions.

#### 9.2.1 Architecture of the Adaptive Cruise Control system

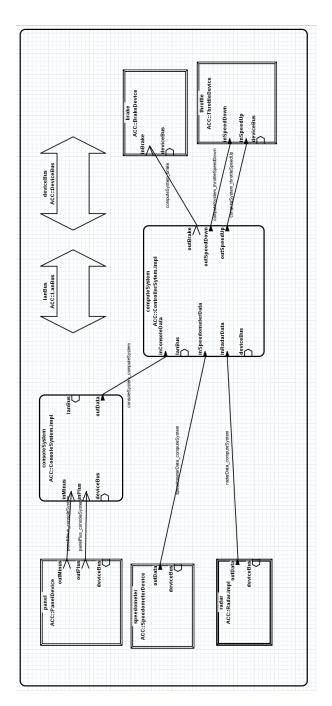

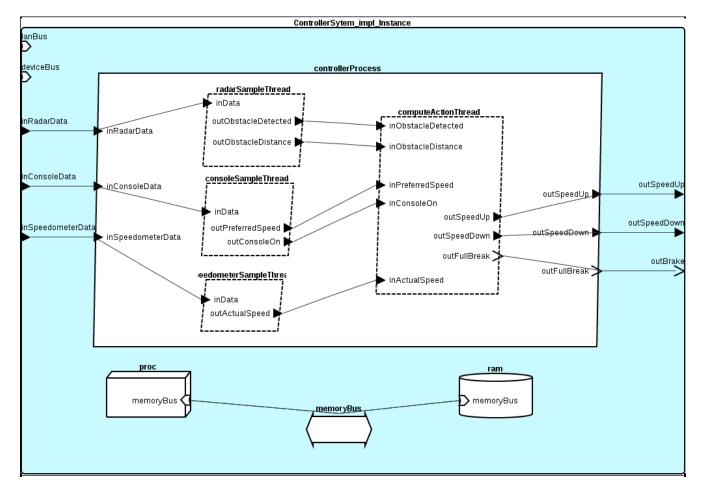

Figure 12 presents an overview of the system, consisting in:

- devices, such as sensors (speedometer, radar, wheel sensor), console with buttons and display, throttle and brakes:

- buses allowing subsystems to communicate with each other and with devices;

- controller and console subsystems.

Each of the two subsystems consists itself of hardware components, such as processors, memories and buses; and software components: processes containing threads. Figure 13 presents the controller subsystem and its components: one processor, one memory, one bus connecting the processor and the memory and one controller process. The controller process itself contains four threads, one for each sensor, and the *ComputeActionThread*, which is responsible for sending *speed up*, *slow down* or *complete stop* signals to the throttle and brakes of the vehicle.

#### 9.2.2 Behavior of the Adaptive Cruise Control system

In AADL, system behavior is specified through the so-called behavior annexes attached to components. Behavior annexes specify the behavior of AADL components (threads and subprograms) through state transition systems with guards and actions, which can be expressed as polychronous automata.

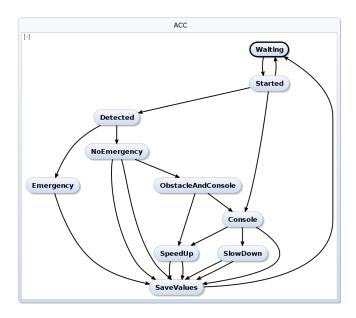

Figure 14 shows the state transition system describing the behavior of the *ComputeActionThread* thread, which is responsible for processing the correct behavior the system should adopt (slow down, speed up or keep the speed constant) depending on the situation.

For readability sake, guards and actions have been omitted. In the case of this state transition system, guards are tests on input signals (are they present or not, and value comparison if they are present), and actions are of two kinds: either the sending of a signal through one of the output ports of the thread; or the computation of an intermediate value, such as the vehicle speed relative to the obstacle one, or the acceleration/deceleration needed to reach a given speed. For an example of such guards and actions, see Listing 1 which presents the complete transition from the *Started* state to the *Detected* one.

The state transition system starts in the *Waiting* state, waiting for its thread to be dispatched, and to pass in *Started* state.

Figure 12 Overview of the Adaptive Cruise Control system modeled with AADI.

Double-lined rectangles represent devices, double-arrows buses and rectangles with rounded corners systems and subsystems.

Figure 13 Controller subsystem of the Adaptive Cruise Control system modeled with AADL. Rectangles represent processors, double-arrows buses, cylinders memories and rhombuses processes and threads.

Figure 14 State transition system for the ComputeActionThread thread.

**Listing 1** Transition between two states of the state transition system described by the behavior annex of the *ComputeActionThread* thread. Guard of the transition is indicated between brackets, and action between braces.

The *Waiting* state is a *complete* one, that is, a state in which a thread pauses its execution when entering in, waiting for a new dispatch.

After entering the *Started* state, depending on the inputs, the state transition system can pass in *Detected* (the system detected an obstacle) or *Console* state (the system did not detect an obstacle and the cruise control is on), or go back to the *Waiting* state (the system did not detect an obstacle and the cruise control is off).

In the *Detected* state, the system must decide the emergency of the situation: if the obstacle is in an unsafe range, the system goes into the *Emergency* state and its next transition will send a signal to brakes in order to stop the vehicle; if the obstacle is outside this range, the system enters the *NoEmergency* state and then determines whether it should slow down to adapt its speed to the obstacle speed, speed up or keep the speed constant (each transition sending the corresponding signal to the throttle after the computation of the needed acceleration/deceleration). The same happens in the *Console* state depending on the current speed of the vehicle and the speed preset by the driver. After saving useful values (e.g., current speed, current obstacle speed and distance

in the *SaveValues* state, the state transition system returns in the *Waiting* state, waiting for the next dispatch of its thread.

#### 9.2.3 Properties of the Adaptive Cruise Control system

Requirements, such as threads deadline, sensors period, memories and buses size, processors frequency and scheduling policies, are modeled using AADL properties.

Timing and scheduling requirements on a thread can be expressed through AADL properties such as: dispatch protocol (Dispatch\_Protocol), period in case of a periodic dispatch (Period), execution deadline (Deadline) and worst-case execution time (Compute\_Execution\_Time). For example, Listing 2 presents these properties attached to the *ComputeAction-Thread* thread.

```

thread implementation ComputeActionThread.impl

properties

Dispatch_Protocol => Periodic;

Period => 50 ms;

Deadline => 40 ms;

Compute_Execution_Time => 20 ms;

end ComputeActionThread;

```

**Listing 2** Timing and scheduling properties of the *ComputeActionThread* thread implementation (double right arrows associate values to properties).

Logical requirements, such as the absence of deadlocks and race condition, are not explicitly expressed through properties, but automatically checked by the Polychrony framework.

### 9.3 Refinement and verification of system requirements using the polychronous model of computation

The AADL model of the ACC system can be transformed into a Signal program, where behavior is described through polychronous automata and properties are used as constraints over the system. It is then possible to use the Polychrony framework to analyze and schedule the system.

#### 9.3.1 Transformation of the Behavior Annex to Signal

An overview of the compositional transformation from AADL to Signal is presented in Section 8. We will now focus on the translation of a state transition system described through an AADL behavior annex to a polychronous automaton described in Signal. The rules describing formally the semantics of the Behavior Annex and its translation in transition systems represented as polychronous automata are de-

tailed in [38]. Here, we rather provide the intuition of this translation as Signal automata through our case study.

Such an automaton is described using the Signal syntactic extensions presented in Section 7. Listing 3 shows the declaration and interface (input and output signals) of the Signal automaton process corresponding to the state transition system of the *ComputeActionThread* thread presented above.

States are simply declared as Signal labels. Listing 4 presents declaration of a few states from the Signal automaton obtained from the transition system of the *ComputeActionThread* thread of the Adaptive Cruise Control system.

Transitions are declared as a label attached to special Signal process Automaton\_Transition which takes as parameters the labels of the source and destination states, and the condition expression corresponding to the AADL guard of the transition. Moreover, transition processes declare Signal equations to compute when firing the transition. Listing 5 presents the Signal declaration corresponding to the AADL transition presented in Listing 1.

```

automaton ComputeActionThread_behavior =

(? event Dispatch, Resume, Deadline;

boolean inObstacleDetected;

integer inObstacleDistance;

integer inPreferredSpeed;

real inActualSpeed;

boolean inConsoleOn;

! event outFullBreak;

real outSpeedUp;

real outSpeedDown;

event Complete;

event Error;

)

```

**Listing 3** Signal declaration and interface of the automaton corresponding to the transition system of the *ComputeActionThread* thread.

```

label S_Waiting, S_Started, S_Detected [...]

```

**Listing 4** Extract of the Signal declaration of the states of the automaton corresponding to the transition system of the *ComputeActionThread* thread.

```

(| t1 :: Automaton_Transition(S_Started, S_Detected,

[:inObstacleDetected])

| on t1 :: (| obstacle_distance ::= inObstacleDistance |)

|)

```

**Listing 5** Signal translation of the AADL transition presented in Listing 1.

Once the AADL model of a system transformed into a Signal program, one can analyze the program using the Polychrony framework in order to check if timing, scheduling and logical requirements over the whole system are met.

#### 9.3.2 Verification of timing and scheduling requirements

Polychrony provides a schedulability analysis for periodic programs obtained from AADL models. In particular, it can detect non-schedulable systems thanks to the timing properties (mainly the period and the WCET—Worst Case Execution Time). Moreover, with some extra information (port rates), periods can be left undefined: they will be computed by calling a standalone plugin named ADFG (this plugin is based on the work of Bouakaz [39,40]).

The schedulability test is triggered during the translation of an AADL processor device into Signal, provided that all threads of the unique process bound to this processor are periodic and have at least a defined Compute\_Execution\_Time. The test is composed of the two following steps:

- 1. Polychrony checks that all threads have a defined period and tries to compute it if it is not the case (in our case study, all periods are defined so this step is skipped). The periods can be computed if all threads define connections between them (such that they form a connected graph) and have Input\_Rate and Output\_Rate properties on their connections' ports. The computation is done by ADFG which ensures that the deduced periods imply a schedulable system.

- 2. A simple utilization factor test is done on the system (which is useful especially if the periods are user-provided). If the utilization factor is less than one, each thread period is converted into an affine clock relation between the fastest clock and each thread control signal (Dispatch, Resume, Deadline, Initialize) with corresponding phases. Otherwise, the AADL to Signal transformation continues on the other AADL elements.

Note that this way of defining the periodic thread control signals implies that the generated Signal code does not take into account possible thread preemptions: this is oriented towards functional simulation.

The current implementation has some limitations: e. g., all temporal properties (periods, etc.) must be expressed in the same time unit, and the scheduled threads must be in the same unique process of a processor. Future work is dedicated to release these limitations and to use an exact scheduling test in the step 2, instead of the utilization factor (which is only a necessary condition), for EDF (Earliest Deadline First) and DM (Deadline Monotonic) scheduling algorithms. Besides, the step 1 is based on ADFG which can compute the best periods, deadlines, and communication buffer sizes given a cyclo-

static dataflow graph, in order to maximize the throughput. This is more than what is currently used, so a possible improvement would be to reuse all the ADFG results to refine more AADL properties related to the scheduling.

#### 9.3.3 Verification of logical requirements

Polychrony also allows to detect deadlocks in an AADL model of a given system. After the transformation of the AADL model to a Signal program (following the compositional transformation presented in Section 8), the Polychrony framework calculates the *Graph of Conditional Dependencies* of the Signal program and computes the product clock of each cycle in this graph (a cycle representing a potential deadlock) [41]. The *Graph of Conditional Dependencies* is a labeled directed graph where:

- vertices are the signals and clock variables;

- edges indicate data dependencies among signals and clock variables;

- labels represent the conditions at which the dependencies are valid.

In this graph, cycles represent possible deadlocks: cyclical data dependencies between signals and/or clock variables. However, since dependencies are conditioned, Polychrony only needs to consider instants where all the dependencies are valid. To do so, it computes the product of the labels of each edge in the cycle. If this product is null, there is no instant where all the dependencies are valid at the same time, and thus there is no possible deadlock.

If the product clock of every cycle in the *Graph of Conditional Dependencies* of the Signal program is null, then the program (and the AADL model from which it has been obtained) is *deadlock-free*.

On the case study, a race condition due to an error in the state transition system of the *ComputeActionThread* was detected thanks to the clock calculus of Polychrony.

In addition, model checking based formal verification can be performed in the Polychrony framework using the associated Sigali tool [35]. Properties such as invariance, reachability and attractivity can be checked by Sigali. Algorithms for computing state predicates are also available in the tool.

#### 10 Conclusion

We have presented a model of finite-state automata, called polychronous automata, that integrates smoothly with

dataflow equations in the polychronous model of computation. They define transition systems to express explicit reactions together with properties, in the form of Boolean formulas over logical time, to constrain their behavior.

The implementation of such automata amounts to composing explicit transition systems with a controller synthesized from the specified constraints.

Polychronous automata have been integrated in the opensource version of the Polychrony framework through lightweight syntactic extensions of the Signal language. They may be used to specify behaviors (and constraints) and to *abstract* behaviors, as the result of a formal calculus.

This formal model of automata supports the recommendations adopted by the SAE committee on the AADL to implement a timed and synchronous behavioural annex for the standard [42]. The model of polychronous automata has been provided as semantic model for our proposal of an extension of the AADL Behavior Annex.

An experimental implementation of the semantic features of this "timing annex" enriches the already existing transformation from AADL models to Signal programs to consider behavior of AADL models. This transformation will be integrated in the POP environment for Eclipse<sup>3)</sup>. The implementation has been tested with the Adaptive Cruise Control case study, developed with Toyota ITC. Adaptive Cruise Control systems are highly safety-critical car embedded systems which need to satisfy multiple interdependent requirements. Polychronous automata allow us to define a complete semantic model for AADL specifications of such systems. We provide tools over this semantic model for verifying and analyzing properties (such as deadlock freeness and schedulability) over a whole system.

#### References