# **CAIRN – GRANIT Teams**

University of Rennes 1 – IRISA ENSSAT – 6 rue de kerampont – 22300 Lannion France

# FPGA-based implementation of a flexible FFT dedicated to LTE standard

Tran Mai Thanh, Emmanuel Casseau, Matthieu Gautier University of Rennes 1, IRISA Laboratory, Cairn & Granit teams, Lannion, France

| <u>Abstract</u>                                                                               |                | Building a flexible FFT for LTE standard                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The Field Programmable Gate Array                                                             |                |                                                                                                                                                                                                           |

| (FPGA) technology is expected to High-level C/C++ Development                                 |                | Algorithm 2 Algorithmic reconfiguration for the power-of-two point FFT                                                                                                                                    |

| play a key role in the development Waveform Modeling BLOCK_1() BLOCK_2() BLOCK_N()            |                | $\succ \text{ FFT with six different lengths for } \frac{\text{FFTPOW2(inputs, outputs, control)}}{\text{function } BLOCK_FFTPOW2(inputs, outputs, control)}  \triangleright 0 \le \text{ control} \le 4$ |

| of Software Defined Radio (SDR)                                                               |                | $\mathbf{OFDM}$ FFT_size_max = 2048                                                                                                                                                                       |

| platforms. To this aim, leveraging BLOCK_A() BLOCK_B()                                        |                | • 128, 256, 512, 1024, 1536,<br>FFT_size = FFT_size_max >> control $\triangleright$ FFT_size = $\frac{\text{FFT}_size\_max}{2^{\text{control}}}$                                                          |

| the nascent High-Level Synthesis                                                              |                | 2048 FFT_stages= FFT_stages_max - control<br>Bit_reverse() ▷ re-range the order of bits before calculating                                                                                                |

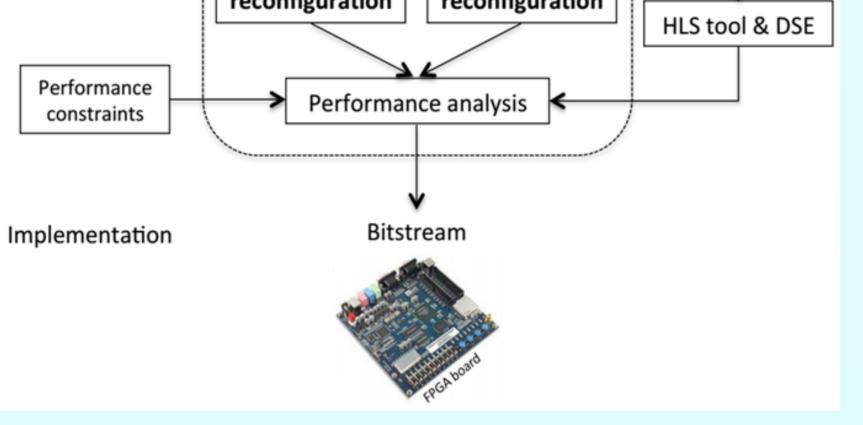

| (HLS) tools, a design flow from                                                               | Algorithmic    | $\blacktriangleright Power-of-two point FFT for i = 0 to FFT_stages do$                                                                                                                                   |

| high-level specifications to Register-                                                        | econfiguration | • Algorithmic reconfiguration $Calculate_index() > choose the stage, prepare for possible twiddles for j = 0 to FFT_size/2 do$                                                                            |

| Transfer Level (RTL) description     Embedded System       Design     Software       Hardware |                | Computing_twiddles() > determine coefficients for radix 2                                                                                                                                                 |

| reconfiguration reconfiguration -                                                             | ¥              | • Radix-2 Decimation-in-innerity for $k = 0$ to FFT_size/2 do                                                                                                                                             |

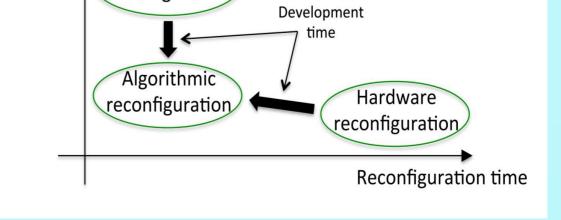

can be thought to generate processing blocks that can be reconfigured at run-time. Based on such a flow, this demo describes the architectural exploration of a Fast Fourier Transform (FFT) for Long Term Evolution (LTE) standard. Synthesis results show the tradeoff between reconfiguration time and area that can be achieved with such an approach.

Generation of multi-mode processing block

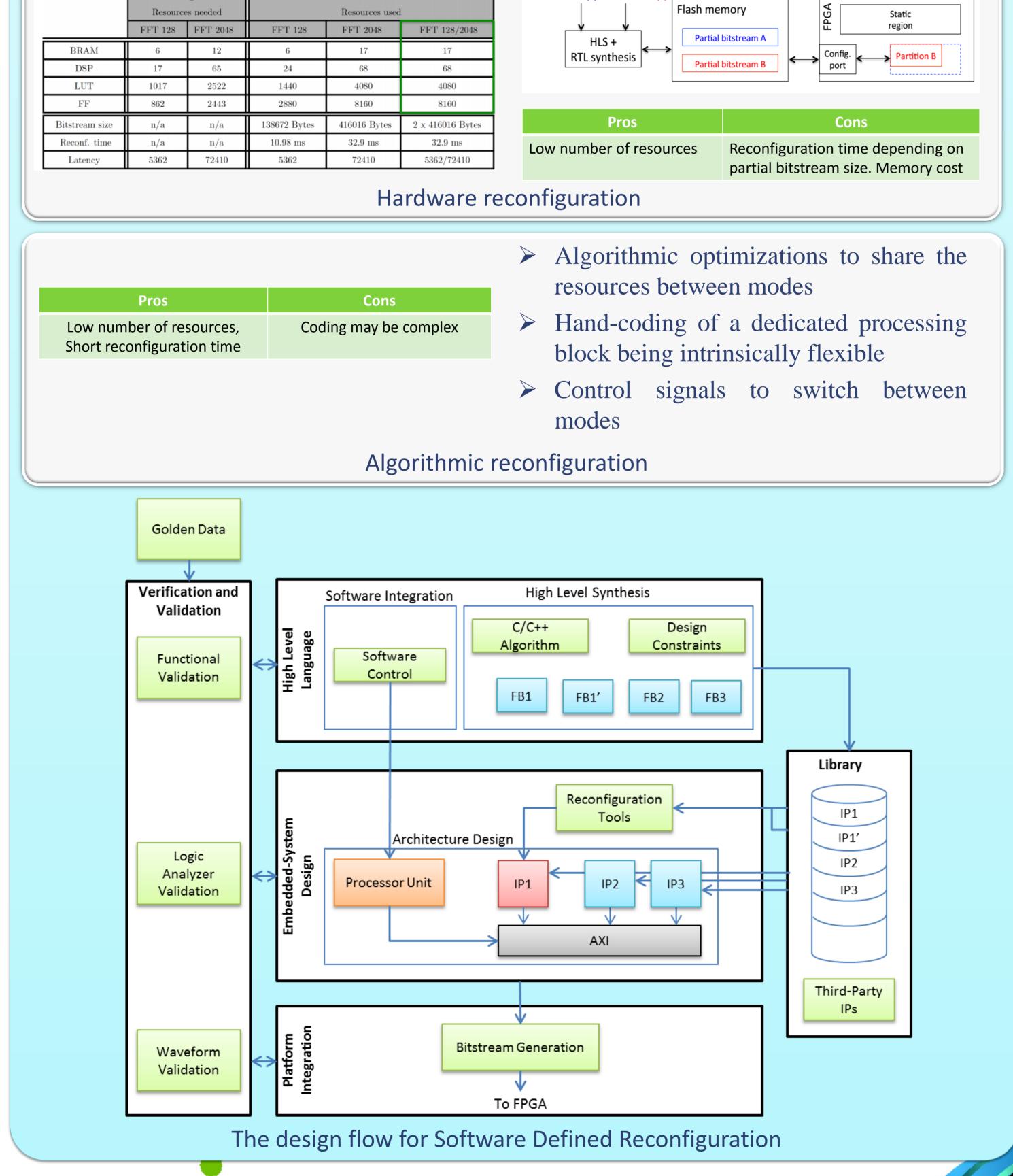

## **Design flow for Software Defined Reconfiguration**

| Algorithm 1 Automatic generation of a multi-mode processing block         | Processing block                                             | Block_FFT128() | BLOCK_FFT2048()                             | Two_Mode_Block() |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------|----------------|---------------------------------------------|------------------|--|

| function MULTI_MODE_BLOCK (inputs, outputs, control)<br>switch control do | BRAM                                                         | 6              | 12                                          | 12               |  |

| case A                                                                    | DSP                                                          | 17             | 65                                          | 82               |  |

| BLOCK_A(inputs, outputs)                                                  | LUT                                                          | 1017           | 2522                                        | 3459             |  |

| case B<br>BLOCK_B(inputs, outputs)                                        | ${ m FF}$                                                    | 862            | 2443                                        | 3241             |  |

| end function                                                              | Latency                                                      | 5362           | 72410                                       | 5491/72411       |  |

| Block A ? Block B                                                         | Software reconfiguration with two FFT modes(128/2048)        |                |                                             |                  |  |

| Flash memory   Multi_Mode Bitstream     Config.   port                    | Pros                                                         |                | Cons                                        |                  |  |

|                                                                           | Simplicity, Rapid prototyping,<br>Short reconfiguration time |                | High resources<br>(Sharing hard to achieve) |                  |  |

|                                                                           | configuration                                                |                |                                             |                  |  |

| Software rec                                                              | 0                                                            |                |                                             |                  |  |

used

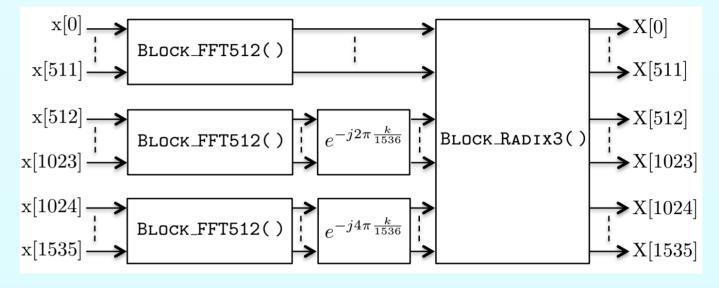

- Flexible FFT for LTE

- Hardware reconfiguration

between Power-of-two point and

1536-point FFTs

[Cooley65] J. Cooley and J. Tukey, "An Algorithm for the machine calculation of complex Fourier series", American Mathematical Society, 1965.

[Norton87] A. Norton, et al, "Parallelization and Performance Analysis of the Cooley-Tukey FFT Algorithm for Shared-Memory Architectures", IEEE Transactions on Computers, 1987.

[Mathew06] J. Mathew, et al, "Exploration of power optimal implementation technique of 128-pt FFT/IFFT for wpan using pseudo-parallel data path structure", in IEEE ICCS 2006.

Radix\_2(inputs, outputs) end function

FFT power-of-two point

FFT 1536-point

|                | Processing block                     |                 | Software reconfiguration                     | Hardware reconfiguration                     |  |

|----------------|--------------------------------------|-----------------|----------------------------------------------|----------------------------------------------|--|

|                | BLOCK_FFTPOW2()                      | BLOCK_FFT1536() | Multi_Mode_Block_LTE()                       | FFT for LTE                                  |  |

| BRAM           | 12                                   | 14              | 26                                           | 17                                           |  |

| DSP            | 65                                   | 40              | 103                                          | 68                                           |  |

| LUT            | 2553                                 | 3054            | 5256                                         | 4080                                         |  |

| $\mathbf{FF}$  | 2497                                 | 2010            | 4299                                         | 8160                                         |  |

| Bitstream size | n/a                                  | n/a             | n/a                                          | $2 \ge 416016$ Bytes                         |  |

| Reconf. time   | n/a                                  | n/a             | 10  ns                                       | $32.9 \mathrm{\ ms}$                         |  |

| Latency        | 3555 / 7604 / 16172<br>34284 / 72412 | 52198           | 3555 / 7604 / 16172<br>34284 / 72412 / 52198 | 3555 / 7604 / 16172<br>34284 / 72412 / 52198 |  |

#### Results of a flexible FFT

**M I R I S A**

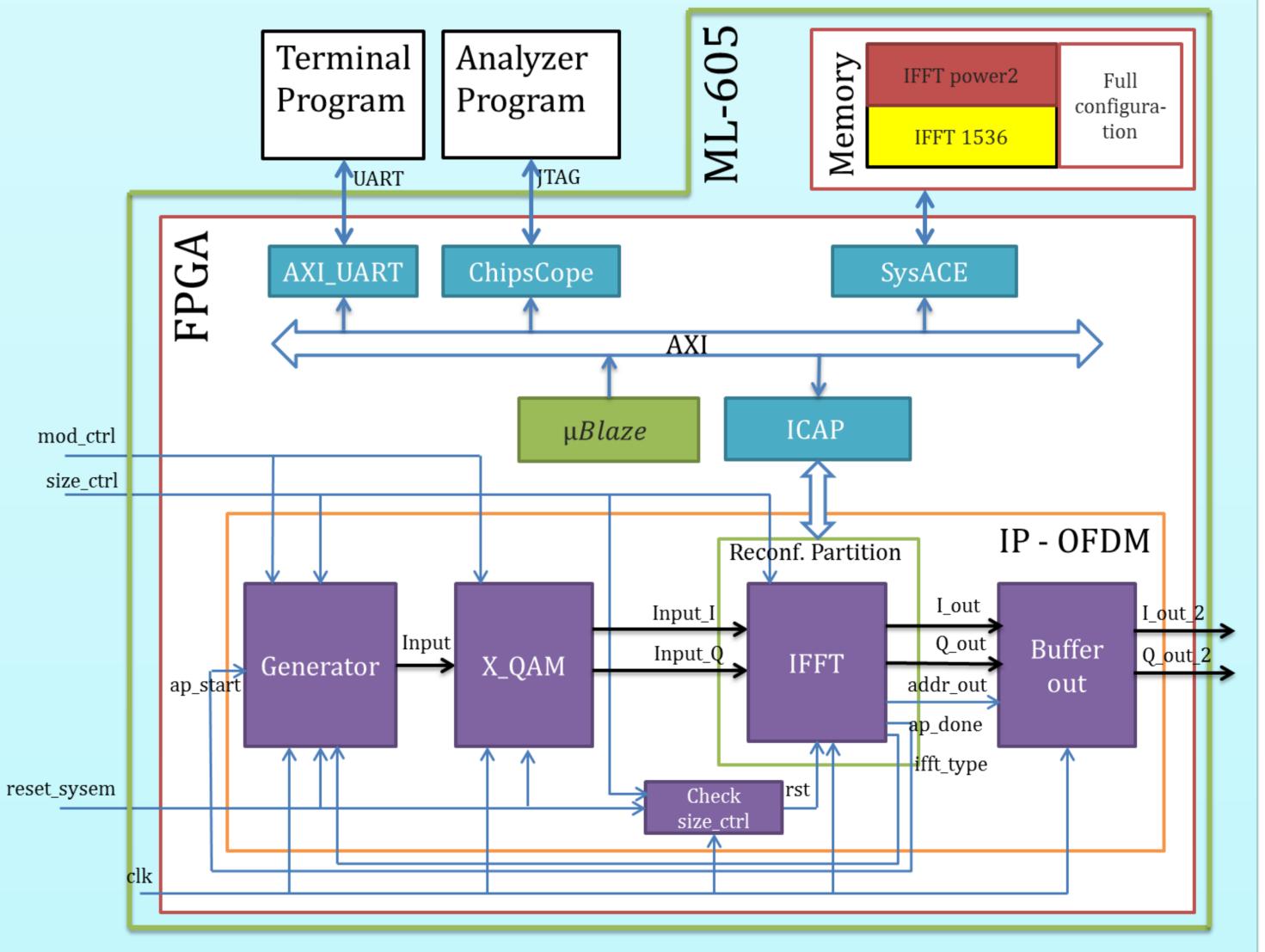

### The design on ML605 board

Resources Software reconfiguration

Tradeoff between resources and reconfiguration time & the board

ContactMai-Thanh TRAN: mai-thanh.tran@irisa.frMatthieu GAUTIER: matthieu.gautier@irisa.frEmmanuel CASSEAU: emmanuel.casseau@irisa.fr

informatics mathematics

Centre de Recherche INRIA – Rennes Bretagne Atlantique