# Synchronous Deterministic Parallel Programming for Multicores with ForeC

Eugene Yip, Partha S. Roop, Alain Girault, Morteza Biglari-Abhari

### ▶ To cite this version:

Eugene Yip, Partha S. Roop, Alain Girault, Morteza Biglari-Abhari. Synchronous Deterministic Parallel Programming for Multicores with ForeC: Programming Language, Semantics, and Code Generation. [Research Report] RR-8943, Inria - Research Centre Grenoble – Rhône-Alpes. 2016. hal-01351552

# HAL Id: hal-01351552 https://inria.hal.science/hal-01351552

Submitted on 3 Aug 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Synchronous Deterministic Parallel Programming for Multicores with ForeC: Programming Language, Semantics, and Code Generation

Eugene Yip, Partha S. Roop, Alain Girault, Morteza Biglari-Abhari

RESEARCH REPORT

N° 8943

August 2016

Project-Team Spades

# Synchronous Deterministic Parallel Programming for Multicores with ForeC: Programming Language, Semantics, and Code Generation

Eugene Yip\*, Partha S. Roop†, Alain Girault‡, Morteza Biglari-Abhari§

Project-Team Spades

Research Report n° 8943 — August 2016 — 89 pages

RESEARCH CENTRE GRENOBLE – RHÔNE-ALPES

Inovallée 655 avenue de l'Europe Montbonnot 38334 Saint Ismier Cedex

$<sup>\</sup>hbox{$^*$ eyip002@aucklanduni.ac.nz, Department of ECE, The University of Auckland, New Zealand.}$

$<sup>^\</sup>dagger$ p.roop@auckland.ac.nz, Department of ECE, The University of Auckland, New Zealand.

<sup>&</sup>lt;sup>‡</sup> alain.girault@inria.fr, Inria, France. Université Grenoble Alpes, Lab. LIG, Grenoble, France. CNRS, Lab. LIG, F-38000 Grenoble, France.

<sup>§</sup> m.abhari@auckland.ac.nz, Department of ECE, The University of Auckland, New Zealand.

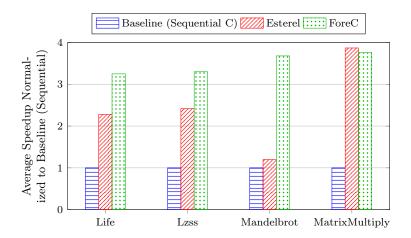

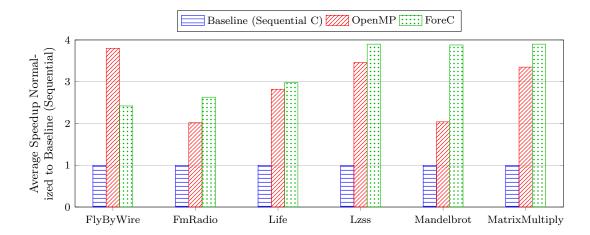

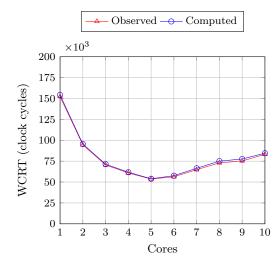

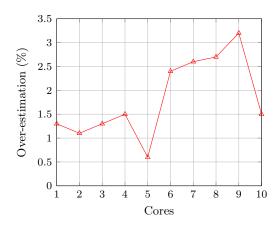

Abstract: Cyber-physical systems (CPSs) are embedded systems that are tightly integrated with their physical environment. The correctness of a CPS depends on the output of its computations and on the timeliness of completing the computations. The increasing use of high-performing and low-power multi-core processors in embedded systems is pushing embedded programmers to be parallel programming experts. Parallel programming is challenging because of the skills, experiences, and knowledge needed to avoid common parallel programming traps and pitfalls. This paper proposes the ForeC language for the deterministic, parallel, and reactive programming of embedded multi-cores. The synchronous semantics of ForeC is designed to greatly simplify the understanding and debugging of parallel programs. ForeC allows programmers to express many forms of parallel patterns while ensuring that ForeC programs can be compiled efficiently for parallel execution and be amenable to static timing analysis. ForeC's main innovation is its shared variable semantics that provides thread isolation and deterministic thread communication. All ForeC programs are correct by construction and deadlock-free because mutual exclusion constructs are not needed. Through benchmarking, we demonstrate that ForeC can achieve better parallel performance than Esterel, a widely used synchronous language for concurrent safety-critical systems, and OpenMP, a popular desktop solution for parallel programming. We demonstrate that the worst-case execution time of ForeC programs can be estimated to a high degree of precision.

**Key-words:** programming language, semantics, parallelism, synchronous, determinism, reactive, multi-core, worst-case execution time, code generation.

# Programmation parallèle, synchrone et déterministe de multi-coeurs avec ForeC: langage de programmation, sémantique et génération de code

Résumé: Les systèmes cyber-physiques sont des systèmes embarqués qui sont très fortement couplés à leur environnement. La correction d'un tel système dépend à la fois des sorties calculées et des dates auxquelles ces sorties sont produites. L'usage croissant de processeurs haute performance multi-cœurs dans les systèmes embarqués pousse les programmeurs à devenir des experts en programmation parallèle. La programmation parallèle représente un défi en raison des compétences, de l'expérience, et des savoirs qui sont requis afin d'éviter les pièges classiques. Dans cet article, nous proposons le langage de programmation ForeC pour la programmation déterministe, parallèle et réactive des processeurs embarqués multi-cœurs. La sémantique synchrone de ForeC a été conçue pour simplifier grandement la compréhension et la mise au point des programmes parallèles. ForeC permet aux programmeurs d'exprimer de nombreuses formes de schémas parallèles tout en garantissant que les programmes ForeC peuvent être compilés efficacement pour une exécution parallèle, et que leur temps d'exécution peut être calculé statiquement. La principale innovation de ForeC réside dans la sémantique des variables partagées, qui garantit l'isolation des fils d'exécution et une communication déterministe entre les fils d'exécution. Tous les programmes ForeC sont correct par construction et sans inter-blocage car les constructions d'exclusion mutuelle ne sont pas nécessaires. Grâce à des benchmarks, nous démontrons que ForeC peut obtenir de meilleures performances parallèles qu'Esterel, un langage synchrone largement utilisé pour les systèmes concurrents à sûreté critique, ainsi qu'OpenMP, une solution utilisée classiquement pour la programmation parallèle. Nous démontrons que le temps d'exécution au pire cas des programmes ForeC peut être estimé avec un très haut degré de précision.

Mots-clés : langage de programmation, sémantique, parallélisme, synchronisme, déterminisme, réactif, multi-cœur, génération de code.

## Contents

| 1        | $\mathbf{Intr}$   | oduction 6                                                |

|----------|-------------------|-----------------------------------------------------------|

|          | 1.1               | Parallel Programming of Embedded Systems                  |

|          | 1.2               | Synchronous Languages                                     |

|          | 1.3               | Programming Safety-Critical Embedded Systems              |

|          | 1.4               | Contributions                                             |

|          | 1.5               | Paper Organization                                        |

| <b>2</b> | Rela              | ated Work                                                 |

|          | 2.1               | Discussion                                                |

| 3        | Mul               | tti-Core Architecture 13                                  |

| Ü        | 3.1               | Predictable Embedded Multi-Core Architecture              |

|          | (TD)              | P. C.I.                                                   |

| 4        |                   | ForeC Language 15 Overview and Syntax                     |

|          | 4.1               | · ·                                                       |

|          |                   | 4.1.1 Local and Global Ticks                              |

|          |                   | 4.1.2 Fork/Join Parallelism                               |

|          |                   | 4.1.3 Shared Variables                                    |

|          |                   | 4.1.4 Copying of Shared Variables                         |

|          |                   | 4.1.5 Resynchronization of Shared Variables               |

|          |                   | 4.1.6 Hierarchical Preemption                             |

|          |                   | 4.1.7 Bounded Loops                                       |

|          | 4.2               | Semantics of ForeC                                        |

|          |                   | 4.2.1 Assumptions                                         |

|          |                   | 4.2.2 Notation                                            |

|          |                   | 4.2.3 Semantic Functions                                  |

|          |                   | 4.2.4 Statically Known Information                        |

|          |                   | 4.2.5 EVAL                                                |

|          |                   | 4.2.6 Copy                                                |

|          |                   | 4.2.7 Combine                                             |

|          |                   | 4.2.8 The Structural Operational Semantics                |

|          |                   | 4.2.9 The nop Statement                                   |

|          |                   | 4.2.10 The copy Statement                                 |

|          |                   | 4.2.11 The pause Statement                                |

|          |                   | 4.2.12 The status Statement                               |

|          |                   | 4.2.13 The abort Statement                                |

|          |                   | 4.2.14 The Assignment Operator (=)                        |

|          |                   | 4.2.15 The if-else Statement                              |

|          |                   | 4.2.16 The while Statement                                |

|          |                   | 4.2.17 The Sequence Operator (;)                          |

|          |                   | 4.2.18 The par Statement                                  |

|          |                   | 4.2.19 Tick Completion                                    |

|          |                   | 4.2.20 Illustrations                                      |

|          |                   | 4.2.21 Example One                                        |

|          |                   |                                                           |

|          | 4.9               | 4.2.22 Example Two                                        |

|          | 4.3               | Definitions and Proofs                                    |

|          | $\frac{4.4}{4.5}$ | Comparison with Esterel, PRET-C, and Concurrent Revisions |

|          | 4.5               | - DISCUSSION 50                                           |

| 5            | Con  | npiling ForeC for Parallel Execution                   | 51         |

|--------------|------|--------------------------------------------------------|------------|

|              | 5.1  | Overview                                               | 51         |

|              | 5.2  | Static Thread Scheduling                               | 51         |

|              | 5.3  | Structure of the Generated Program                     | 55         |

|              | 5.4  | The par Statement                                      | 55         |

|              | 5.5  | The pause Statement                                    | 59         |

|              | 5.6  | Shared Variables                                       | 59         |

|              | 5.7  | The abort Statement                                    | 59         |

|              | 5.8  | Global Tick Synchronization                            | 60         |

|              | 5.9  | Generating Programs for Execution on Operating Systems | 61         |

|              | 5.10 | Discussion                                             | 61         |

| 6            | Fore | eC Benchmarking                                        | 63         |

|              | 6.1  | Benchmark Programs                                     | 63         |

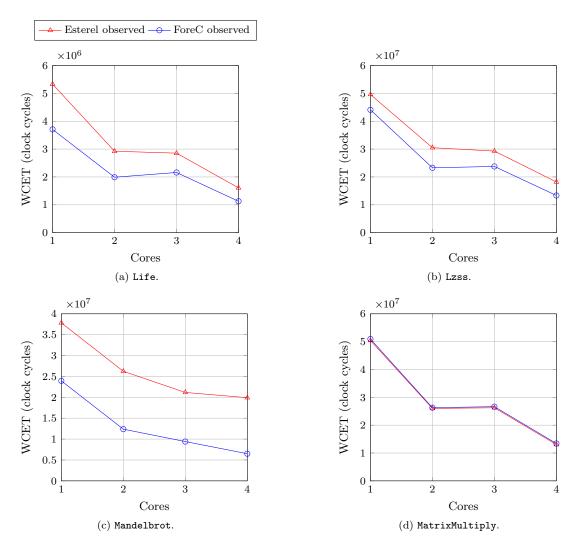

|              | 6.2  | Performance Evaluation                                 | 63         |

|              |      | 6.2.1 Comparison with Esterel                          | 64         |

|              |      | 6.2.2 Comparison with OpenMP                           | 66         |

|              | 6.3  | Time Predictability                                    | 67         |

|              | 6.4  | Discussion                                             | 68         |

| 7            | Con  | aclusions and Future Directions                        | <b>7</b> 0 |

| $\mathbf{A}$ | Sha  | red Variables                                          | 71         |

|              | A.1  | Passing Shared Variables by Value and by Reference     | 71         |

|              | A.2  | Combining More Than Two Copies                         | 72         |

|              | A.3  | Combine Policies Illustrated                           | 73         |

|              |      | Examples of Combine Functions                          | 75         |

### 1 Introduction

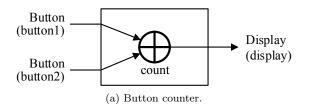

People interact daily with many embedded systems, which are digital systems embedded into a product to add specific functionality, such as those shown in Figure 1. An embedded system is safety-critical if its failure to operate correctly may lead to catastrophic consequences [1]. Safety-critical embedded systems [72] must be dependable and functionally safe [26, 102, 41] and certified against safety standards, such as DO-178B [115], IEC 61508 [61], and ISO 26262 [63]. Certification is a costly and time consuming exercise and is exacerbated by the use of multi-core processors to create more efficient designs. Safety-critical embedded systems typically monitor and control physical processes in the environment that in turn affects the computations of the embedded systems. Because the computations and physical processes are tightly coupled, these embedded systems need to be real-time and reactive, computing new outputs as soon as new inputs are detected. For example, an unmanned aerial vehicle must react continuously to its surrounding environment to avoid obstacles while it flies to its intended destination. The correctness of an embedded system depends on the output of its computations and on the timeliness of completing the computations [79, 145].

A key to building successful embedded systems using multi-core processors is the understanding of the timing behaviors of the computations [8] and physical processes. Unfortunately, the timing behavior of computations modeled in the C programming language [62], a popular language for programming embedded systems, is complex because it depends on the underlying architecture. The timing of C programs is typically validated by static worst-case execution time (WCET) analysis [145]. The understanding of the timing behavior of C programs on multi-core processors can be greatly enhanced by the following methods: (1) introducing timing constructs that allow programmers to control time as a first-class resource, e.g., enforcing that the execution time between two programming points must be less than the inter-arrival time of inputs; and (2) defining a deterministic parallel execution semantics for multi-threaded C programs that communicate over shared memory. This paper tackles these two points by bringing together the formal semantics of synchronous languages [13] and the benefits of C's control and data structures. The resulting language, called ForeC, is suitable for the deterministic parallel programming of multi-cores. The following sections review the parallel programming of embedded multi-cores and the programming restrictions for easing the certification process.

Figure 1: Examples of embedded systems and those with safety-critical concerns.

### 1.1 Parallel Programming of Embedded Systems

Programs can be executed directly by the hardware (bare-metal) or by a real-time operating system (RTOS) [147]. The bare-metal approach allows all of the system's resources to be used to execute the program, but code must be included to manage the hardware. By contrast, an RTOS manages the hardware and provides a consistent environment for developing and executing programs, thus, enabling code portability across a range of systems. Hence, the RTOS must be taken into account when analyzing programs. C [62] is a popular language for programming embedded systems with support for multi-threading and parallelism provided by third-party libraries, compilers, and runtime support [38]. Notable examples include Pthreads [132], OpenMP [100], and MPI [90]. These multi-threading solutions are inherently non-deterministic [78] because they allow non-deterministic constructs, such as race conditions over shared variables in the case of Pthreads and OpenMP. The lack of formal semantics for the programming model can also lead to ambiguous behaviors.

Parallel programming is challenging because it requires programmers to have specific skills, experience, and knowledge to avoid the common parallel programming traps and pitfalls [88]. For example, parallel accesses to the same shared variable will interfere and corrupt the value of the shared variable. It is the programmer's responsibility to identify the regions of code that can interfere, called *critical sections*, and ensure that they are executed sequentially at mutually exclusive times. Hence, programmers need to be aware of the data dependencies in their specific program and to choose the appropriate solution to manage the dependencies. Studies have shown that, without careful tuning [80], parallel programs executed on multi-cores can perform worse than their sequential counterparts. The next section describes the use of *synchronous languages* as an alternative to creating concurrent programs that are deterministic.

### 1.2 Synchronous Languages

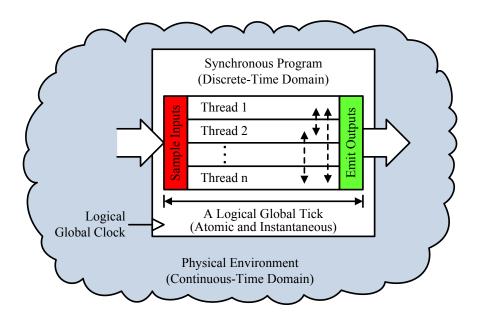

Synchronous languages [13] are based on sound mathematical semantics, which facilitates system verification by formal methods [13] and the generation of correct-by-construction implementations [44, 94]. Figure 2 depicts a synchronous program, defined as a set of concurrent threads, within its physical environment. Synchronous programs react continuously to inputs from the environment by producing corresponding outputs. Each reaction is triggered by a hypothetical (logical) global clock. At each global tick, the threads in the program sample the environment, perform their computations, and emit their results to the environment. When a thread completes its computation, we say that the thread has completed its *local tick*. When all threads in the program have completed their local tick, we say that the program has completed its global tick. Central to synchronous languages is the synchrony hypothesis [13], which states that the execution of each reaction is considered to be atomic and instantaneous. The sampling of inputs avoids the need to use interrupts which are sources of unpredictable delays that degrade the system's timing predictability. Concurrent threads communicate instantaneously with each other (dashed arrows in Figure 2) due to the synchrony hypothesis. Once the embedded system is implemented, the synchrony hypothesis has to be validated. That is, the worst-case execution time [144] of any global tick must not exceed the minimal inter-arrival time of the inputs.

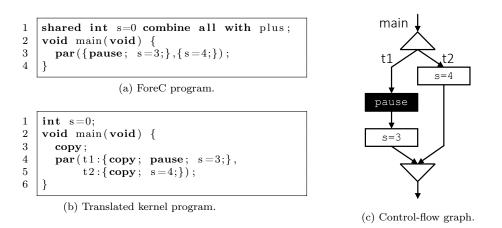

We use the Esterel synchronous language [18] to illustrate some features of the synchronous paradigm in Figure 3a. It contains two threads (starting from lines 4 and 7 respectively), scoped between the square brackets and separated by the parallel operator  $\parallel$  (line 6). The parallel operator is commutative and associative and specifies that both threads are executed concurrently. The execution of a thread can be divided over multiple global ticks with the pause statement (e.g., lines 5, 8, and 11). The pause statement pauses the execution of its enclosing thread, demarcating the end of the thread's local tick. All executing threads must pause or terminate

Figure 2: Synchronous model of computation.

```

int A = 0, B = 0;

2

thread main(void) {

module main:

3

PAR(t0, t1);

2 3

signal A, B

4

5

thread t0() {

4

6

A \, = \, 1 \, ;

emit A;

5

EOT;

pause

7

6

8

thread t1() {

if (A == 1) { B = 1; }

7

present A then emit B end;

9

8

10

EOT;

9

abort

11

10

emit B;

12

abort {

11

pause;

13

B = \dot{1};

EOT;

12

emit A; emit B

14

13

when immediate A

15

A = 1; B = 1;

14

16

\} when (A == 1);

15

end module

17

(b) PRET-C

(a) Esterel

```

Figure 3: Examples of synchronous programs.

to complete the global tick. Thus, the pause acts as a synchronization barrier. At the next global tick, the threads resume from their respective pauses. In Esterel, threads communicate by emitting signals and threads can test for their presence or absence. For example, line 2 declares two signals, A and B, that are emitted by the emit statement when execution reaches lines 4, 7, 10, and 12. An emitted signal lasts until the global tick ends, becoming absent in the following global tick unless it is emitted again. Note that an emitted signal is logically present from the start of the global tick to ensure that all the threads see the same signal statuses, even if the emit statement occurs later in the global tick. In the first global tick, the first thread emits the signal A. At the same time, the second thread tests positively for the presence of A and emits B. Using the abort statement, a body of code can be preempted by the presence of a signal. Preemption provides a convenient way to model the transitions and states of a state machine. In the second global tick of the example program, the second thread enters an abort (line 9) that preempts its body (lines 10–12) if A is present. Because A is not present, the body is not preempted and B is emitted. Meanwhile, the first thread terminates because it has reached the end of its body.

Synchronous programs are considerably difficult to parallelize [48, 66, 153] due to the need to resolve instantaneous thread communication and associated causality issues. At runtime, all potential signal emitters must be executed before all testers of a signal. If this is not possible, then a causality issue arises. Thus, concurrency is typically *compiled away* to produce only sequential code [44]. The common approach for parallelizing synchronous programs is to automatically parallelize an intermediate representation of the program [48, 66, 153, 10]. The techniques differ in the heuristics used to partition the program to achieve sufficient parallelism.

Esterel only supports basic data computations and delegates complex data computations to a host language, for instance C. Consequently, C-based synchronous languages have been developed to provide data handling at the language level. These languages extend C with a range of synchronous constructs to support concurrency, preemption, and thread communication. C-based synchronous languages appeal to C programmers because the learning barrier for synchronous languages is reduced. PRET-C [4] is one such example and Figure 3b is the PRET-C version of the Esterel example (Figure 3a). The two threads (to and t1, defined on lines 5 and 9) are arguments to the parallel operator PAR (line 3). The EOT statement demarcates the end of a thread's local tick (e.g., lines 7, 11, and 14). Unlike Esterel, threads in the PAR's argument are executed in a left-to-right (static) order. The thread's local tick must be executed entirely before the next thread can be executed. In the example program, to always executes its local tick before t1. In PRET-C, threads communicate using globally declared C-variables, not signals. Because threads are always executed in a static order, the local ticks always execute in a mutually exclusive manner. Hence, threads can safely access shared variables without needing to use mutual exclusion constructs; all PRET-C programs are thread-safe by construction. In the first global tick of Figure 3b, t0 executes first and assigns 1 to the shared variable A (line 6). Then, t1 executes and checks the condition A==1, which is true, and assigns 1 to B. PRET-C does not suffer from causality issues because global variables are always present and variables are always accessed sequentially (within a thread and across threads). PRET-C supports preemption with the abort statement but its behavior differs from Esterel's abort. Preemption occurs when the associated C-condition evaluates to true. The condition is always checked before the abort body is executed. In the second global tick of the example program, t0 terminates because it has reached the end of its body. Then, t1 executes and the condition A==1 (line 16) is checked before the abort body (lines 13–15) is executed. The condition is true, so the body is preempted. Execution jumps to line 15 and t1 terminates.

Other C-based synchronous languages exist, such as Synchronous C [138] and Esterel C Language [77], and are reviewed in Section 2. However, these languages are not designed to take

advantage of parallel execution. This paper focuses on developing a C-based, synchronous language for writing parallel programs that perform well on multi-core processors and are amenable to static timing analysis.

### 1.3 Programming Safety-Critical Embedded Systems

Safety-critical embedded systems need to be certified against stringent safety standards, such as DO-178B [115] or IEC 61508 [61], before they can be deployed and used in the field. Although the C language is popular for programming safety-critical embedded systems, its semantics [62] includes unspecified and undefined behaviors [73]. Strict coding guidelines [91, 57, 64] are typically used by safety-critical programmers to help write well defined programs that are deterministic, understandable, maintainable, and easier to debug [47, 56]. The coding guidelines can be grouped into three main areas:

Code clarity: These guidelines suggest a style for writing programs free of ambiguous statements and to structure code for readability. For example, the use of braces to clarify the nesting of if-else statements or the forbidding of goto statements. Code clarity helps static analyzers parse the program and attain greater analysis precision.

Defensive programming: These guidelines help minimize the use of unspecified and undefined behaviors, which contribute to non-determinism. For example, the C semantics does not specify the evaluation order of multiple expressions, e.g., in function arguments. Thus, function arguments with side-effects may evaluate to different values depending on the evaluation order used by the implementation. To ensure deterministic evaluation [97], expressions must not contain any assignment operators, e.g., "=", "+=", or "++". Furthermore, the sequencing operator "," must not be used in expressions.

Runtime reliability: These guidelines help prevent runtime errors from occurring, even when the program is written correctly. For example, a runtime error occurs when a program requests for more memory than is available in the implemented system. To prevent it, memory is always allocated statically at the start of the program. Static verification tools, such as Parasoft [104], Polyspace [109], and Parallel Lint [68], can be used to identify possible runtime defects.

### 1.4 Contributions

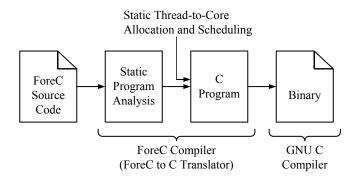

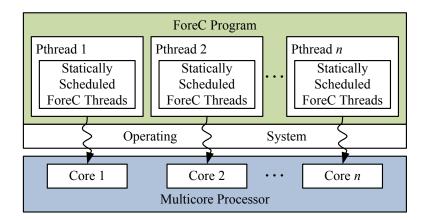

We propose the ForeC parallel programming language for simplifying the deterministic parallel programming of embedded multi-core systems. Execution platforms have evolved from single-cores to multi-cores. Hence, all the synchronous languages designed for the single-core era must be reinvented to address the multi-core challenges. To this end, ForeC is a C-based synchronous language designed specifically for the programming of multi-cores. ForeC brings together the formal deterministic semantics of synchronous languages and the benefits of C's control and data structures. A key innovation is ForeC's shared variable semantics that provides thread isolation and deterministic thread communication. Moreover, many forms of parallel patterns can be expressed in ForeC. We show that ForeC programs are reactive and deterministic by construction. ForeC can be compiled for direct execution on embedded multi-cores or for execution by an OS on desktop multi-cores. Through benchmarking, we demonstrate that ForeC can achieve better parallel performance than Esterel and OpenMP, while also being amenable to static timing analysis.

### 1.5 Paper Organization

This paper is organized as follows. Section 2 provides a detailed literature review of parallel and synchronous programming languages. Section 3 describes the multi-core architecture considered by this paper. Section 4 introduces the ForeC language, defines the formal semantics, and provides proofs for determinism and reactivity. Section 5 describes our compilation approach for generating code that delivers good parallel performance and that is amenable to static timing analysis. Section 6 presents benchmarking results for ForeC's performance on multi-cores and the time predictability of its execution. Section 7 concludes the paper.

### 2 Related Work

Designing embedded systems that are time-predictable remains an open challenge [8]. Moreover, the growth of embedded multi-cores is pushing more programmers to be parallel programming experts. Table 1 highlights different approaches for enforcing mutual exclusion on shared variables, usually by interleaving the parallel accesses to enforce a sequence of accesses to the critical sections. As argued by Lee [78], the adoption of parallelism in sequential languages, like C [62], discards important properties, such as determinism, predictability, and understandability. Thus, programmers spend large amounts of time taming the non-determinism in their parallel programs [85]. Instruction reordering is regularly employed by compilers and processor cores to maximize execution parallelism, but this can cause wrong values for shared variables to be observed. C provides the programmer with memory fences to enforce a partial ordering on variable accesses between threads: all side-effects of a releasing thread are committed before the acquiring thread leaves the fence. To help tame non-determinism, runtime environments that enforce deterministic thread scheduling and memory accesses can be used. Such runtime environments have been developed for Linux processes (DPG [15]), Pthreads (Grace [16], Kendo [99], CoreDet [14], and Dthreads [84]), OpenMP (DOMP [7]), and MPI (DetMP [154]). For DPG, Kendo, Core-Det, and Dthreads, all thread interactions are mapped deterministically onto a logical timeline (which progresses independently of physical time). Program execution is divided into alternating parallel and serial phases, similar to the Bulk Synchronous Parallel (BSP) [136] programming model. In the parallel phase, threads execute in parallel until they all reach one of the following synchronization points: a lock, memory access, or statically defined number of executed instructions. Then, in the serial phase, threads take turns to resolve their memory accesses or lock acquisitions. Threads in CoreDet and Dthreads also maintain their own version of the shared memory state, which is resynchronized in every serial phase. This concept is used and formally defined in concurrent revisions [27]. DOMP and Grace differ in that the resynchronization only occurs when threads reach a synchronization construct. However, understanding the program's behavior at compile time remains difficult because the determinism is only enforced at runtime. Thus, if the program is modified, e.g., to fix a bug, then a vastly different runtime behavior is possible. An alternative is to directly extend and modify the C language with deterministic parallelism, such as SharC [116], CAT [45], SHIM [131],  $\Sigma C$  [51], and ForkLight [70]. These solutions allow the asynchronous forking and synchronized joining of threads, but lack a convenient mechanism for preempting groups of threads. However, their timing predictability has not been demonstrated, which is required for programming safety-critical embedded systems.

The classic synchronous languages are Esterel [18], Lustre [53], Signal [52], and the recent extension based on functional programming such as Lucid Synchrone [35], and are well suited to the modeling of control-dominated systems [30] and safety-critical systems [13]. To increase their uptake with embedded programmers, C-based synchronous languages have been developed, such as Reactive Shared Variables [23], Esterel C Language (ECL) [77], PRET-C [4] and Synchronous C

**Programming Constructs:** These are constructs written in the host language to provide mechanisms for the programmer to achieve mutual exclusion. Examples include: locks, monitors, memory fences, transactional memory, message passing, and parallel data structures. Using these constructs correctly can be tedious and error prone for large programs and may lead to other errors [78, 88, 85], e.g., deadlocks, starvation, or priority inversion.

Language Semantics: The language semantics can have a memory model that defines how threads interact through memory, what value a read can return, and when the value of a write becomes visible to other threads. Although the memory model can prevent race conditions, it may only be suitable for a few types of applications. Examples include: synchronous languages [13], PRET-C [4], Synchronous C [138], SharC [5], Deterministic Parallel Java [21], SHIM [137],  $\Sigma C$  [51], concurrent revisions [27], and Reactive Shared Variables [23].

Static Analysis: A compiler or static analyzer can identify and alert the programmer regarding the race conditions in their program (e.g., Parallel Lint [68]) and may try to resolve them by serializing the parallel accesses for the programmer (e.g., Sequentially Constructive Concurrency [139]). However, programmer guidance is needed for race conditions that cannot be resolved.

Runtime Support: Programs are executed on a runtime layer that dynamically enforces deterministic execution and memory accesses. Examples include: dOS [15], Grace [16], Kendo [99], CoreDet [14], Dthreads [84], DOMP [7], and DetMP [154]. However, understanding the program's behavior at compile time remains difficult because the determinism is only enforced at runtime.

Hardware Support: Parallel accesses can be automatically detected and resolved by the hardware, preventing race conditions from happening. Examples include: Ultracomputer's combine hardware [124] and certain shared bus arbitration (e.g., round-robin, TDMA, and priority). However, the timing of the parallel accesses affects how they are interleaved.

Table 1: Existing solutions for avoiding race conditions.

(SC) [138, 139]. The inherent sequential execution semantics of SC, Reactive Shared Variables, and PRET-C renders them unsuitable for multi-core execution. Moreover, concurrency in synchronous languages is a logical concept to help the programmer handle concurrent inputs, rather than a specification for parallel execution. Thus, compilers typically generate only sequential code [44, 112], although some generate concurrent tasks [31, 93, 101, 94] for execution on single-cores. Yuan et al. [153, 151] offer a static and dynamic scheduling approach for Esterel on multi-cores. For the static approach, threads are statically load-balanced across the cores and signal statuses are resolved at runtime. For the dynamic approach, threads that need to be scheduled for execution are inserted into a custom hardware queue accessible to all cores. The dynamic approach has been shown to provide better average-case performance compared to the static approach [151]. This is because the static approach uses worst-case execution times to load-balance the threads, even though the actual execution times may be shorter.

The common approach for parallelizing synchronous programs is to parallelize an intermediate representation of the sequentialized code [48, 66, 153, 9, 29, 150, 103]. Multi-threaded OpenMP programs can be generated from the Synchronous Guarded Actions intermediate format [10]. The techniques differ in the heuristics used to partition and distribute the program to achieve sufficient parallelism. The Synchronized Distributed Executive (SynDEx) [111] approach considers the cost of communication when distributing code to each processing element. When distributing a synchronous program, some desynchronization [12, 49, 24] is needed among the concurrent threads. That is, the concurrent threads execute at their own pace, but sufficient inter-thread

communication is used to preserve the original synchronous semantics. The use of *futures* has been proposed as a method for desynchronizing long computations in Lustre [34]. A *future* is a proxy for a result that is initially unknown but becomes known at a later time and can be computed in parallel with other computations.

Once a synchronous program is implemented, it is necessary to validate the synchrony hypothesis. That is, the worst-case execution time [145, 144] (WCET) of any global tick must not exceed the minimal inter-arrival time of the inputs. This is known as worst-case reaction time (WCRT) analysis [22, 89] and various techniques have been developed for single-cores [89, 67, 140, 117, 32, 3, 22, 75] and multi-cores [66, 149].

### 2.1 Discussion

This section has presented a snapshot of the current efforts in the programming of time-predictable CPSs. Many of the attempts at providing deterministic parallelism have used concepts found in synchronous languages. C-based synchronous languages have much to offer to embedded programmers in terms of deterministic concurrency and formally verifiable implementations, but lack support for parallel execution. This paper tackles the lack of a C-based synchronous parallel programming language that offers both time-predictability and good parallel execution performance.

### 3 Multi-Core Architecture

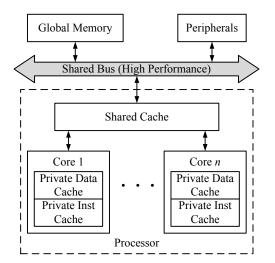

Embedded systems continue to explode in complexity and functionality [74]. To meet the size, weight, and power (SWaP) concerns, the advent of affordable embedded multi-core processors [19, 126 offer designers the opportunity to achieve better performance than single-core processors. Figure 4 illustrates the architecture of a general-purpose multi-core. In pursuit of increasing average-case performance, the cores typically include speculative features [105] such as out-oforder execution, branch prediction, data forwarding, superscalar execution, and on-chip caches. However, such optimizations can cause timing anomalies [86] where a local worst-case execution time does not lead to the program's worst-case execution time. Thus, speculation leads to the degradation of time-predictability and is undesirable for embedded systems. The PREcision Timed (PRET) machine [43, 42] and PRedictability Of Multi-Processor Timing (PROMPT) [36, 69] design philosophies aim to tackle this issue by advocating the design of predictable hardware architectures, while not sacrificing performance. In particular, the architecture should provide timing isolation between the cores, i.e., the actions of the cores must not influence each other's timing behavior. The architecture should be timing compositional, i.e., with repeatable timing behavior and free of timing anomalies. The following are examples of unpredictable hardware features with possible predictable alternatives [146, 98, 11]:

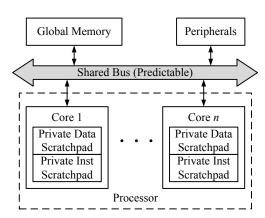

Replace caches with fast software managed memories, called scratchpads [143]. The selection of data and instructions to be allocated to a scratchpad is determined entirely at compile time [134, 129, 71, 113, 96]. In the static allocation scheme, the contents of the scratchpad cannot be changed at runtime. In the dynamic allocation scheme, the contents of the scratchpad can be changed at runtime by using compile time decisions. Importantly, the replacement policy of scratchpads is controllable, whereas with caches the replacement policy is controlled by the hardware, sometimes with unpredictable behaviors (e.g., with the PLRU policy). The memory address spaces of scratchpads and global memory are mutually exclusive.

Figure 4: General multi-core architecture.

Figure 5: Example of a predictable multicore embedded architecture.

Replace out-of-order execution with better code generation from the compiler [106, 123, 40, 39, 135]. A processor's ability to reorder a group of instructions is limited by the size of its instruction buffer. The compiler does not have this limitation because it has access to the entire program and can make better judgments when reordering instructions. However, it may not have the runtime execution information which may affect the performance.

Deactivate high-performance bus features, such as burst transfers or pipelining, and use fair time-sharing arbitration policies, such as round-robin or time division multiple access (TDMA) [125]. The round-robin policy cycles through a static list of cores, granting them access to the bus. If the granted core does not need the bus, then the grant is given to the next core on the list. The TDMA policy cycles through a static list of cores, granting them access for a fixed amount of time (a time slot), whether the core needs it or not. If the granted core does not need the bus, then some policies [125, 6, 76, 108, 54] will grant the slot to the other cores in a round-robin manner, thus improving the throughput. Fairness of the arbitration is important to ensure that all accesses complete within a bounded length of time.

Embedded systems designed using the PRET [42] or PROMPT [69] philosophies are simpler to understand, model, and analyze. Many predictable single-core processors have been proposed, such as the MACS [33], MCGREP [142], Patmos [122], PTARM [83], and FlexPRET [155] processors. MERASA [135] is a predictable multi-core processor that supports hard and non-real-time threads. Hard real-time threads access scratchpads for predictability, while non-real-time threads access caches for performance. An analyzable memory controller is used to arbitrate shared bus accesses from the cores. For Java programs, there is the JOP [121] processor and its multi-core variant [114] that uses scratchpads and a shared TDMA bus.

The execution of synchronous programs can be accelerated by reactive processors [118, 81], which have hardware support for signal resolution, concurrency, preemptions, and global tick synchronization. A key feature is their ability to execute programs in a time predictable manner. Single-core multi-threaded reactive processors include KEP [81] and STARPro [152]. Reactive multi-processors include EMPEROR [37] and HiDRA [120]. However, these reactive processors

and associated compilers do not support the execution of host functions written in a host language, such as C. As a compromise between efficiency and host language support, a general purpose processor can be patched with a reactive functional unit to accelerate the execution of synchronous constructs. The ARPRET [2] processor is a patched Xilinx MicroBlaze [148] processor tailored for executing PRET-C. Java-based reactive single-core processors include RJOP [92] and TP-JOP [82]. GALS-HMP [119] is a Java-based reactive multi-processor.

### 3.1 Predictable Embedded Multi-Core Architecture

The architecture of the predictable multi-core used in this paper is representative of existing designs. It is a homogeneous multi-core processor [36, 121] that we have designed using identical Xilinx MicroBlaze [148] cores, illustrated in Figure 5. Each MicroBlaze core has a three-stage, in-order, timing anomaly-free pipeline connected to private data and instruction scratchpads. The scratchpads are statically allocated and loaded at compile time. A shared bus with TDMA arbitration connects the cores to shared resources, such as global memory and peripherals. Due to the resource constraints of existing FPGA devices, we developed a multi-core MicroBlaze simulator for benchmarking purposes. We extended an existing MicroBlaze simulator [141] significantly to support cycle-accurate simulation, an arbitrary number of cores, and a shared bus with TDMA arbitration.

### 4 The ForeC Language

Execution platforms have evolved from single-cores to multi-cores. Hence, all the synchronous languages designed earlier (e.g., Esterel [18], Lustre [53], Signal [52], Esterel C Language [77], Reactive Shared Variables [23], and PRET-C [4]) must be remodeled to address the challenges raised by multi-cores. Over 30 years of synchronous programming languages have demonstrated that they are very well suited to the design of safety-critical real-time systems [25, 127]. Moreover, the ideal modeling of time brought by the synchrony hypothesis makes them good candidates for PRET programming. This motivates our proposed ForeC language that is dedicated to the programming of multi-cores. ForeC inherits the benefits of synchrony, such as determinism and reactivity, along with the benefits and power of the C language, such as control and data structures. This is unlike conventional synchronous languages, which treat C as an external host language. A key goal of ForeC is in providing deterministic shared variable semantics that is agnostic to scheduling. This goal is essential for the reasoning and debugging of parallel programs. This section presents ForeC with a UAV running example. The formal semantics of ForeC is then detailed and important proofs concerning program reactivity and determinism [87, 130] are provided.

### 4.1 Overview and Syntax

Fore C is a synchronous language that extends a safety-critical subset of C [20, 65] (see Section 1.3) with a minimal set of synchronous constructs. We briefly describe the statements, type specifiers, and type qualifiers allowed in the C subset:

C statements (c\_st): Expressions in a statement can only be constants, variables, pointers, and arrays that are composed with the logical, bitwise, relational, and arithmetic operators of C. Although the use of pointers and arrays is allowed, they can make static dataflow analysis difficult [28] because of pointer aliasing. Thus, we assume that pointers are never reassigned to point to other variables. All C control statements, except goto, can be used.

```

Statements: st ::= c\_st \mid \texttt{pause} \mid \texttt{par}(st, st) \mid \texttt{weak}? \texttt{ abort } st \texttt{ when immediate}? (exp) \mid st; st

Type Qualifiers: tq ::= c tq \mid \texttt{input} \mid \texttt{output} \mid \texttt{shared}

```

Figure 6: Syntactic extensions to C.

input: Type qualifier to declare an input, the value of which is updated by the environment at the start of every global tick.

output: Type qualifier to declare an output, the value of which is emitted to the environment at the end of every global tick.

shared: Type qualifier to declare a shared variable, which can be accessed by multiple threads. pause: Pauses the executing thread until the next global tick.

par(st, st): Forks two statements st as parallel threads. The par terminates when both threads terminate (join back).

weak? abort st when immediate? (exp): Preempts its body st when the expression exp evaluates to a non-zero value. The optional weak and immediate keywords modify its temporal behavior.

Table 2: ForeC constructs and their semantics.

These are the selection statements (if-else and switch) and loop statements (while, do-while, and for).

- C type specifiers: All the C primitives can be used, e.g., char, int, and double. Custom data types can be defined using struct, union, and enum.

- C type qualifiers (c tq): All the C const, volatile, and restrict qualifiers can be used.

- C storage class specifiers: The C typedef, extern, static, auto, and register specifiers can be used.

Figure 6 gives the extended syntax of ForeC and Table 2 summarizes the informal semantics. A statement (st) in ForeC can be a traditional C statement  $(c_st)$ , or a barrier (pause), fork/join (par), or preemption (abort) statement. Using the sequence operator (;), a statement in ForeC can be an arbitrary composition of other statements. Like C, extra properties can be specified for variables using type qualifiers. A type qualifier (tq) in ForeC is a traditional C type qualifier  $(c_tq)$ , an environment interface (input and output), or a shared variable amongst threads (shared). The input, output, and shared type qualifiers precede the C type qualifiers in variable declarations.

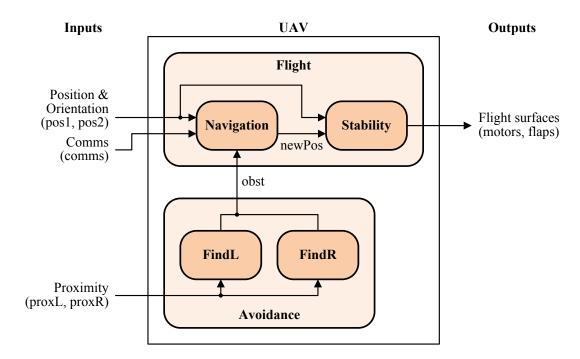

As a running example to illustrate the ForeC language, we describe the design of an unmanned aerial vehicle (UAV) inspired by the Paparazzi project [95]. A UAV is a remotely controlled aerial vehicle commonly used in surveillance operations. Figure 7 presents the functionality of the UAV as a block diagram of tasks. The UAV consists of two parallel tasks called Flight and Avoidance. The Flight task consists of two parallel tasks called Navigation and Stability. The Navigation task localizes the UAV with on-board sensors, updates the flight path, and sends the desired position to the Stability task. The Stability task controls the flight surfaces to ensure stable flight to the desired position. The Avoidance task consists of two parallel tasks called FindL and FindR. These tasks use on-board sensors to detect obstacles around the UAV and sends collision avoidance data to the Navigation task.

Figure 7: Tasks of the UAV.

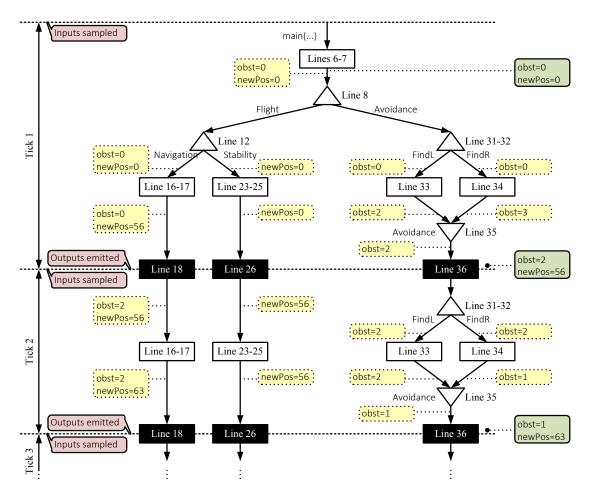

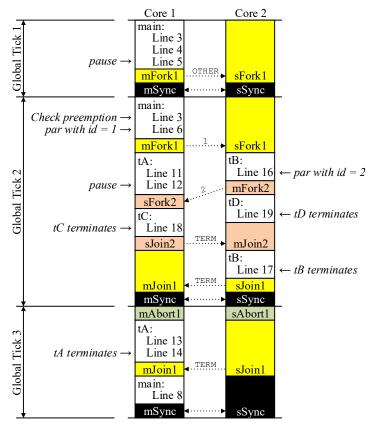

Figure 8 is a ForeC implementation of the UAV example given in Figure 7. Figure 9 is a possible execution trace of Figure 8 to help illustrate the execution of ForeC programs. Sections 1.2 described the execution behavior of synchronous programs. To recap, the threads of a synchronous program execute in lock-step to the ticking of a global clock. In each global tick, the threads sample the environment, perform their computations, and emit their results to the environment. When a thread completes its computation, we say that it has completed its local tick. When all the threads complete their local ticks, we say that the program has completed its global tick. In Figure 9, the first three global ticks are demarcated along the left-hand side.

In Figure 8, the UAV program starts with the inclusion of a C header file (line 1) for the functions used in the program and the global variable declarations (lines 2–3) to interface with the environment. Line 2 declares inputs to capture sensor readings. Inputs are read-only and their values are updated by the environment at the start of every global tick. Line 3 declares outputs for the actuation commands for the flight motors and surfaces. Outputs emit their values to the environment at the end of every global tick. Inputs and outputs can only be declared in the program's global scope. The left-hand side of Figure 9 shows the sampling of inputs and emission of outputs at the start and end of each global tick, respectively.

Like traditional C programs, the function main (line 5) is the program's main entry point and serves as the initial thread of execution. Lines 6–7 declare variables that can be shared amongst threads (see Section 4.1.3). In Figure 9, the states of the shared variables are given inside solid round boxes at specific points in the execution trace. Line 6 declares a shared variable obst to store the distance and angle of the closest obstacle as an encoded integer. Line 7 declares a shared variable newPos to store the UAV's desired position.

On line 8, the par statement forks the Flight (line 11) and Avoidance (line 30) functions into two parallel *child* threads. We refer to the threads by their function names, e.g., the Flight and Avoidance threads. The forking of threads is represented in Figure 7 as triangles. On line 12,

```

1

#include <uav.h>

input int pos1, pos2, proxL, proxR;

output int motors=0, flaps=0;

Inputs.

// Outputs.

3

void main(void) {

5

shared int obst=0 combine new with min;

6

shared int newPos=0 combine new with plus;

8

par(Flight(&newPos,&obst), Avoidance(&obst));

9

10

void Flight(shared int *newPos, shared int *obst) {

11

12

par(Navigation(newPos, obst), Stability(newPos));

13

14

15

void Navigation(shared int *newPos, shared int *obst) {

16

while (1) {

17

*newPos=plan(pos1, obst);

18

pause;

19

20

}

21

22

void Stability(shared int *newPos) {

23

while (1) {

24

motors=thrust(pos2, newPos);

25

flaps=angle(pos2, newPos);

26

pause;

27

28

29

30

void Avoidance(shared int *obst) {

31

\mathbf{while} \ (1) \ \{

32

par(

\{*obst=find(proxL);\},

Thread\ FindL .

33

34

{*obst=find(proxR);}

// Thread FindR.

35

36

pause;

37

}

38

39

40

\mathbf{int} \hspace{0.2cm} \min \hspace{0.1cm} (\hspace{0.1cm} \mathbf{int} \hspace{0.2cm} \hspace{0.2cm} \th 1 \hspace{0.1cm}, \hspace{0.1cm} \mathbf{int} \hspace{0.2cm} \hspace{0.2cm} \th 2 \hspace{0.1cm}) \hspace{0.2cm} \hspace{0.1cm} \{

41

if (th1 < th2) {

42

return th1;

43

else {

44

return th2;

45

46

}

47

48

int plus(int th1,int th2) {

49

return (th1+th2);

50

```

Figure 8: Example ForeC program for the UAV running example.

Figure 9: Possible execution trace for Figure 8.

the Flight thread forks two more parallel child threads, Navigation (line 15) and Stability (line 22), creating a hierarchy of threads. The par statement can also fork blocks of code, e.g., line 32 forks the FindL and FindR threads. The par is a blocking statement and terminates only when both its child threads have terminated and joined together. The joining of threads is represented in Figure 9 as inverted triangles.

After the Navigation, Stability, FindL, and FindR threads have forked, they start executing their respective body. For example, the Navigation thread enters the while-loop (line 16) and computes a new desired position. Next, the pause statement pauses the thread's execution (line 18), acting as a synchronization barrier. In Figure 9, the pause statements are shown as black rectangles and the program completes a global tick when all the threads pause. This is indicated by the dotted horizontal lines across the pause statements.

Every time a thread starts its local tick, it creates *local copies* of all the shared variables that its body accesses (reads or writes). The local copies are initialized at the start of the global tick with the values that have been resynchronized at the end of the previous global tick. We use combine functions to compute these resynchronized values (details below). The shared variables declared in the program remain distinct from the threads' local copies. When a thread needs to access a shared variable, it accesses its local copies instead. Thus, the changes made by a thread cannot be observed by others, yielding mutual exclusion and thread isolation. Moreover, only sequential reasoning is needed within a thread's local tick. In Figure 9, the states of a thread's copies are shown inside dotted round boxes throughout the execution trace. For example, when the Navigation thread starts its first local tick, it has a copy of obst and newPos (values equal to 0). When its local tick ends, its copy of newPos has been set to 56.

To enable thread communication, the copies of each shared variable are automatically combined into a single value when the threads join and when the global tick ends. This is achieved by a programmer-specified combine function. In Figure 8, the combine function for obst (line 6) is min (line 40), specified by the combine clause, which returns the closest obstacle. The combine clause also specifies that only the copies with new values are combined (new since the last global tick). In global tick one of Figure 9, the FindL and FindR threads set new values (2 and 3) to their copies of obst. When these threads join, the new values are combined to 2 and assigned to their parent thread Avoidance. Meanwhile, the Navigation thread only reads its copy of obst. Thus, when global tick one ends, the value of the shared variable obst is set to 2 by the min function. Had there been more copies with new values, then these copies would have been combined and assigned to obst before the next global tick started. We say that the shared variables are resynchronized at the end of each global tick. In Figure 9, the resynchronized values are shown inside solid round boxes, e.g., obst = 2 and newPos = 56. The shared variables start each global tick with their resynchronized values. For the first global tick only, the resynchronized value of a shared variable is its initialization value.

Appendix A describes more examples of combine functions and how more than two copies are combined. The following sections elaborate on the details of local and global ticks, fork/join parallelism, shared variables, and preemption.

### 4.1.1 Local and Global Ticks

We say that a thread completes its *local tick* when it pauses, terminates, or forks at least one thread that completes its local tick without terminating. For example, in Figure 8, the Avoidance thread starts its first local tick by forking the child threads FindL and FindR (line 32). Assuming that the find function does not pause, both child threads complete their local tick by terminating. After the child threads join, the Avoidance thread reaches a pause (line 36) and completes its first local tick. A program completes its global tick when all its threads have completed their

main: Parent of Flight and Avoidance.

Flight: Parent of Navigation and Stability. main and Flight: Ancestors of Navigation and

Stability.

FindL and FindR: Siblings of each other.

Navigation: Relative of Avoidance, FindL, FindR,

and Stability.

(b) Descriptive examples.

Figure 10: Thread genealogy for Figure 8.

respective local ticks. At the next global tick, the paused threads start their next local tick from their respective pauses. For brevity, we shorten "global tick" into "tick" and use "local tick" as before.

### 4.1.2 Fork/Join Parallelism

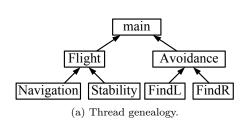

The par statement enables the forking of parallel threads. We use the well known terminology related to parallel programming. The parent thread is the thread that executes the par statement to fork its *child* threads. The parent thread is also the ancestor of its child threads and their nested child threads. Child threads forked by the same par statement are *siblings*. Because the par is a blocking statement, threads always execute sequentially with respect to their ancestors. Threads that are not ancestors of each other are relatives and can execute in parallel.

The thread genealogy of a program can be determined statically by inspecting the program's control-flow. Figure 10a shows the thread genealogy of the UAV program. Each node is a thread and arrows are drawn from the children to their parent thread. Figure 10b exemplifies the thread genealogy.

### 4.1.3 Shared Variables

All variables in ForeC follow the scoping rules of C. By default, all variables are *private* and can only be accessed (read or write) by one thread throughout its scope. To allow a variable to be accessed by multiple threads, it must be declared as a *shared* variable by using the **shared** type qualifier. Thus, any misuse of private variables are easy to detect at compile time. Appendix A.1 describes how shared variables are passed by value and by reference into functions. The semantics we propose for ForeC makes sure that the shared variables can be safely accessed by the parallel threads without the need of mutual exclusion constructs. The goal is to provide a deterministic shared variable semantics that is agnostic to scheduling, which is essential for the design and debug of parallel programs. Within each tick, the accesses to a shared variable from two threads may occur in sequence or in parallel:

**Definition 1.** Accesses from two threads are in **sequence** if both threads are not relatives or if the accesses occur in different ticks.

**Definition 2.** Accesses from two threads are in **parallel** if both threads are relatives and the accesses occur in the same tick.

Improperly managed parallel accesses to a shared variable can cause race conditions, leading to non-deterministic behavior. For example, two parallel writes to a shared variable can non-deterministically and partially overwrite each other's value. A parallel read and write to a shared

variable can result in the read returning the variable's value before, during, or after the write has completed. Table 1 in Section 2 reviewed the solutions that exist for enforcing mutual exclusion on shared variables, usually by interleaving parallel accesses into a sequence. Parallel accesses can be interleaved in many ways (influenced by the programmer, compiler, and runtime system), and relying on a particular interleaving for correct program behavior is brittle and error prone.

We propose a shared memory model that permits shared variables to be accessed deterministically in parallel, without needing the programmer to explicitly use mutual exclusion. The goals of the model are:

**Isolation:** Provide isolation between threads to enable the local reasoning of each thread. That is, the execution of a thread's local tick can be understood by only knowing the values of the variables at the start of the thread's local tick.

**Determinism** [87]: Ensure deterministic execution regardless of scheduling decisions. This guarantees that deterministic outputs are always generated at the end of each tick.

**Parallelism:** Minimize the need to serialize parallel accesses to shared variables. This maximizes the amount of parallel execution that can occur at runtime, which is important for improving the program's performance.

We propose the following mechanisms for achieving our shared memory model: All threads access their own *local copies* of the shared variables, and these copies are *resynchronized* every time threads join and when the tick ends.

### 4.1.4 Copying of Shared Variables

Every time a thread starts its local tick, it creates *local copies* of all the shared variables that its body accesses (reads or writes). When a thread is forked, its initial copy of a shared variable is created from its parent's copy if it exists, otherwise, from the shared variable's resynchronized value. A parent thread that is blocked on a par statement does not create any copies of the shared variables until the par statement terminates. For example, in tick two of Figure 9, the threads main, Flight, and Avoidance make no local copies. The child threads Navigation, Stability, FindL, and FindR must create their local copies from the shared variables' resynchronized values, e.g., obst = 2 and newPos = 56. A shared variable declared inside a thread can be shared among its child threads by passing a reference (using a pointer) into the child threads (e.g., obst on line 8 of Figure 8). When a shared variable is passed by reference into an ordinary function (e.g., obst on line 17), the function uses the calling thread's copy of the shared variable.

### 4.1.5 Resynchronization of Shared Variables

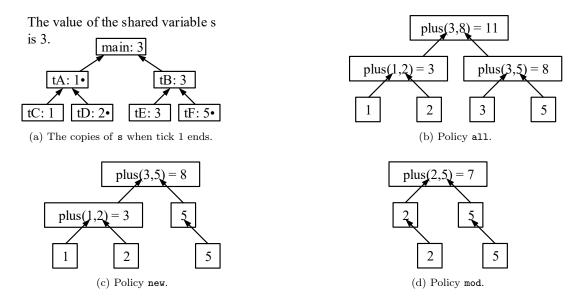

The copies are resynchronized every time the program completes its tick (before outputs are emitted). Resynchronizing at specific program points ensures that the semantics of shared variables is agnostic to scheduling. We use combine functions to compute the value of resynchronized shared variables. Combine functions must be deterministic, associative, and commutative. That is, the combine function produces the same outputs from the same inputs, regardless of previous invocations and how the copies are ordered or grouped. The signature of any combine function is  $C: Val \times Val \rightarrow Val$ . The two input parameters are the two copies to be combined. When a par statement terminates, the copies from the terminating child threads are combined and assigned to their parent thread's copies of shared variables. For example, in Figure 9, the Avoidance thread gets a copy of obst every time FindL and FindR terminate. Appendix A describes more examples of combine functions and how more than two copies are combined.

```

Constants, variables, and grouping.

Expressions:

exp ::= val \mid var \mid ptr[exp] \mid (exp)

| u \ op \ exp \ | \ exp \ b \ op \ exp

// Unary and binary expressions.

Unary

u \ op := * | & | ! | - | ~

Operators:

// Indirection, address, negation,

negative, and one's complement.

Binary

Operators:

b \ op ::= | | | && | ^ | | | & | << | >>

Logical and bitwise operators.

== | != | < | > | <= | >=

Relational operators.

+ | - | * | / | %

Arithmetic operators.

```

Figure 11: Syntax of preemption conditions.

It can be useful to ignore some of the copies when resynchronizing a shared variable. This is achieved by specifying a *combine policy* that determines what copies will be ignored. The combine policies are new, mod, and all. The combine policy of a shared variable is specified during variable declaration in the combine clause, e.g., combine new with. The new policy ignores copies that have the same value as their shared variable, i.e., which has not changed during the tick. The mod policy ignores copies that were not assigned a value during the tick, i.e., have not appeared on the lefthand side of an assignment. The default policy is all where no copies are ignored. Note that the combine function is not invoked when only one copy remains. Instead, that copy becomes the resynchronized value. Appendix A provides extensive illustrations comparing the behavior of the combine policies.

### 4.1.6 Hierarchical Preemption

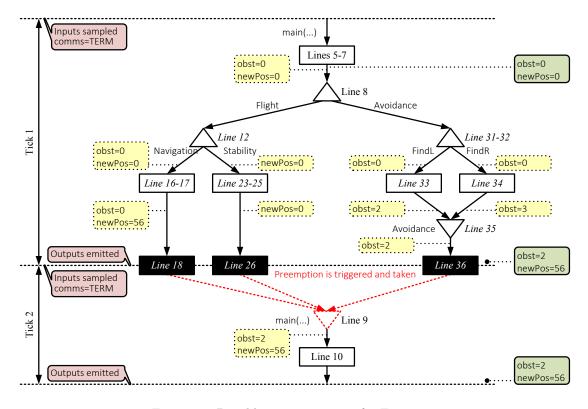

Inspired by Esterel [18], the abort st when (exp) statement provides preemption [17], which is the termination of the abort body st when the condition exp evaluates to true. Preemption can be used to model state machines succinctly. The condition exp must be a side-effect free expression produced from the syntax shown in Figure 11. In Figure 12, the main function of the UAV has been extended to respond to external commands through the input comms (line 2). The value of comms can be OK, ERROR, WARN, or TERM (line 1). The abort statement on line 7 preempts the execution of all the UAV tasks when TERM is received. A possible execution trace of the program of Figure 12 is given in Figure 13. The italicized line numbers in Figure 13 refer to the line numbers in Figure 8, while the non-italicized line numbers refer to the line numbers in Figure 12. We now explain the semantics of the abort statement. The preemption of the abort must be triggered before the abort body can be terminated. Preemption is never taken when the abort body executes for the first time (e.g., tick one in Figure 13). At the start of each subsequent tick, the condition exp is evaluated before the abort body can execute. This allows shared variables in the condition to be evaluated with their resynchronized value. If exp evaluates to true (any non-zero value following the C convention), then the preemption is triggered and the abort statement is terminated. At the start of tick two in Figure 13, preemption is triggered because the preemption condition evaluates to true. The abort statement also terminates if its body terminates normally.

Preemptions in ForeC differ from those in Esterel because Esterel uses signals for thread communication rather than shared variables. As explained in Section 1.2, signals in Esterel are either present or absent in each tick and this information is propagated instantaneously

<sup>&</sup>lt;sup>1</sup>This differs from the new policy because an assignment of the form "x=x" will be taken into account by the mod policy, but not by the new policy.

```

typedef enum {OK,ERROR,WARN,TERM} State;

2

input State comms;

// Additional input.

3

void main(void) {

4

5

shared int obst=0 combine new with min;

6

\mathbf{shared} \ \mathbf{int} \ \mathrm{newPos}{=}0 \ \mathbf{combine} \ \mathbf{new} \ \mathbf{with} \ \mathrm{plus} \ ;

7

8

par(Flight(&newPos,&obst), Avoidance(&obst));

} when (comms=TERM);

9

10

safeDescent();

11

```

Figure 12: Figure 8 extended with preemption.

Figure 13: Possible execution trace for Figure 12.

```

shared int s=0 combine all with plus;

1

2

int plus(int th1,int th2) { return (th1+th2); }

3

void main(void) {

s=1; printf(''%d'',s);

4

5

/*weak*/ abort {

par(\{s=2;pause;s=3;pause;s=4;\},

7

\{s=5; pause; s=6; pause; s=7;\});

} when /*immediate*/ (s>0);

printf(''%d'',s);

8

9

10

```

(a) Example code.

Tick 1: "1" printed. s = plus(2,5) = 7.

Tick 2: Preemption is triggered and the abort body is terminated. "7" printed.

(b) Non-immediate and strong abort.

**Tick 1:** "1" printed. Preemption is triggered and the abort body is terminated. "1" printed again.

(d) Immediate and strong abort.

Tick 1: "1" printed. s = plus(2,5) = 7. Tick 2: Preemption is triggered. s = plus(3,6) = 9. The abort body is terminated. "9" printed.

(c) Non-immediate and weak abort.

**Tick 1:** "1" printed. Preemption is triggered. s = plus(2,5) = 7. The abort body is terminated. "7" printed.

(e) Immediate and weak abort.

Figure 14: Abort variants.

among the threads without delay. Thus, preemptions in Esterel are triggered instantaneously, whereas preemptions in ForeC are triggered with a delay of one tick because the condition exp is evaluated using values computed in the previous tick. Like Esterel [17], the optional weak and immediate keywords change the temporal behavior of preemptions. The weak keyword delays the termination of the abort body until the body cannot execute any further, e.g., reaches a pause statement. The immediate keyword allows preemption to be triggered immediately when execution reaches the abort for the first time. That is, the preemption condition exp is evaluated immediately when execution reaches the abort. This is similar to Esterel's immediate abort behavior. To illustrate these four different preemption behaviors, Figure 14a presents an abort with the optional keywords commented out.

Non-immediate and strong abort: The weak and immediate keywords are commented out in Figure 14a. This gives the default preemption behavior, summarized in Figure 14b. In tick one, the main thread sets its copy of s to 1 and prints "1". Next, the threads to and t1 set their copies of s to 2 and 5, respectively. When the tick ends, using the combine policy all, the resynchronized value of s is 7. In tick two, the abort's preemption is triggered and the abort body is terminated, resulting in "7" being printed.

Non-immediate and weak abort: Only the weak keyword is uncommented in Figure 14a. Figure 14c summarizes the preemption behavior. The execution of tick one proceeds identically to the non-immediate and strong abort variant. In tick two, the abort's preemption is triggered. However, the termination of the abort body is delayed until threads to and t1 complete their local ticks. This allows t0 and t1 to set their copies of s to 3 and 6, respectively. Thus, "9" is printed.

Immediate and strong abort: Only the immediate keyword is uncommented in Figure 14a.

```

1

void main(void) {

2

int x=1;

3

weak abort {

4

x=2;

5

abort \{x=3; pause; x=4;\} when immediate (x==2);

6

x=5; pause;

7

x=6:

when immediate (x==1);

8

9

printf(", %d", x);

10

```

Figure 15: Nesting of preemptions.

Figure 14d summarizes the preemption behavior. In tick one, the main thread sets its copy of s to 1 and prints "1". Next, the abort's preemption condition is evaluated immediately. Intuitively, because "1" was printed for the value of s, the condition s>0 should evaluate to true. The counter-intuitive result of false would occur if the resynchronized value of s was used. Thus, when execution reaches an immediate abort, the condition exp is evaluated immediately with the thread's copies of the shared variables. In subsequent ticks, the resynchronized values of the shared variables are used. In tick one of Figure 14d, because the preemption has been triggered, the abort body is terminated without executing.

Immediate and weak abort: Both the weak and immediate keywords are uncommented in Figure 14a. Figure 14e summarizes the preemption behavior. In tick one, the main thread sets its copy of s to 1 and prints "1". Next, the abort's preemption is triggered immediately. However, the termination of the abort body is delayed until threads t0 and t1 complete their local ticks. This allows t0 and t1 to set their copies of s to 2 and 5, respectively. Hence, "7" is printed.

The abort statements can be nested to create a hierarchy of preemptions with the outer abort executing before the inner aborts. Thus, the preemption behavior of the outer abort takes precedence over the inner aborts. Figure 15 is an example of an immediate and weak abort (line 3) with a nested immediate and strong abort (line 5). In tick one, preemption is triggered for the outer weak abort. The variable x is set to 2 and the inner strong abort preempts immediately without executing its body. Next, x is set to 5 and the outer weak abort takes its preemption when it reaches the pause on line 6. Finally, "5" is printed.

### 4.1.7 Bounded Loops

In addition to the strict C-coding guidelines described in Section 1.3, ForeC forbids the use of unbounded recursion of function calls and thread forking to ensure static WCRT analyzability. The synchrony hypothesis requires each tick to execute in finite time, which means that all statements need to have bounded execution times. Unfortunately, loop constructs (for and while) can have unbounded iterations, leading to unbounded execution times. Thus, if a loop construct is used, then the programmer must guarantee that it always terminates or executes a pause in each iteration. Guaranteeing that a loop always executes a pause may not be possible when pause statements are enclosed by if-statements. The compiler makes conservative assumptions to prove whether a loop always executes a pause in each iteration. For example, a loop is assumed to always execute a pause in each iteration if its body has at least one statement that always executes a pause. An if-statement is assumed to always execute a pause if both its branches always execute a pause. An abort statement is assumed to never execute a pause.

| Bounded Loop                | Translation                                                           |

|-----------------------------|-----------------------------------------------------------------------|

| for (init; cond; update) #n | int cnt=0;                                                            |

| {st}                        | for (init; cond && (cnt <n); (update,cnt++))="" td="" {st}<=""></n);> |

| while (cond) #n {st}        | for ( ; cond;) #n {st}                                                |

| do {st} while (cond) #n     | int first=1;                                                          |

|                             | for ( ; cond && (first==0); first=0) #n {st}                          |

Table 3: Structural translations of bounded loops.

A par statement is assumed to always execute a pause if at least one of its child threads always executes a pause. The compiler can perform structural induction on the program's control-flow to conservatively prove whether every loop in the program will always execute a pause in each iteration.

Inspired by PRET-C [4], we have extended the syntax of loops to also allow the programmer to write bounded loops, shown in the first column of Table 3. The "#n" after the loop header specifies that only up to n iterations can be executed. The second column of Table 3 gives the structural translation of bounded loops.

### 4.2 Semantics of ForeC