### Work-in-Progress and Demo Proceedings - 2016 IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)

Vincent Nélis, Sophie Quinton

#### ▶ To cite this version:

Vincent Nélis, Sophie Quinton. Work-in-Progress and Demo Proceedings - 2016 IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS). 2016 IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), Apr 2016, Vienna, Austria. , 2016. hal-01305183

### HAL Id: hal-01305183 https://inria.hal.science/hal-01305183

Submitted on 20 Apr 2016

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### 2016 IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)

Work-in-Progress and Demo Proceedings

Vienna, Austria April 11-14, 2016

http://2016.rtas.org/work-in-progress/ http://2016.rtas.org/demos/  $\bigodot$  Copyright 2016 held by the authors

#### Message from the Work-in-Progress and Demo chairs

Dear colleagues,

Welcome to Vienna, and to the Work-in-Progress (WiP) and Demo Session of the 22nd IEEE Real-Time Embedded Technology and Applications Symposium (RTAS'16). This session is dedicated to new and on-going research as well as to work with concrete systems, tools and prototypes in the field of real-time and embedded systems. We are happy to present 12 WiP papers and 8 demos that cover innovative research and experiments from a wide range of topics, including real-time scheduling, cache contention, real-time issues related to COTS multicore platforms, and runtime monitoring.

The main goal of the WiP session is to provide researchers with an opportunity to discuss evolving and early-stage ideas, and solicit feedback from the real-time systems community at large. Similarly, the demo session offers a forum such that researchers can give a demonstration of and get feedback about their work with concrete systems, tools and prototypes in all areas of real-time embedded technology and applications. The presentations can only give a brief overview of the research approaches chosen and of the work achieved by the speakers introducing the selected contributions. We hope that these presentations will encourage you to ask questions, share your ideas, and provide valuable feedback to the authors during the poster and demo sessions that will follow. We would like to emphasize that stimulating discussions are the most important feature of the WiP and demo session.

We would like to thank the members of the WiP and demo session technical program committees for their help in publicizing the session and reviewing the papers. We would also like to thank the authors for their interesting contributions and their choice of RTAS as a means to share and improve their research. Last but not least, our special gratitude goes to the RTAS'16 program chair, Rob Davis, for his help and support.

We hope that you will enjoy the Work-in-Progress and Demos of RTAS 2016!

Vincent Nélis, CISTER/INESC TEC and ISEP, Portugal, Work-in-Progress chair Sophie Quinton, Inria Grenoble Rhône-Alpes, France, Demo chair RTAS 2016

### **Program Committees**

#### Work-in-Progress

Chaired by Vincent Nélis, CISTER/INESC TEC and ISEP, Portugal.

Borislav Nikolic CISTER/INESC TEC and ISEP, Portugal

Björn Brandenburg Max Planck Institute for Software Systems, Germany

David Bol Microelectronics laboratory – ICTEAM institute,

Université Catholique de Louvain, Belgium

Benny Åkesson CISTER/INESC TEC and ISEP, Portugal

Leandro Indrusiak University of York, U.K.

Andrea Marongiu Integrated Systems Laboratory, ETH, Swiss

Paolo Burgio University of Modena, Italy

Dakshina Dasari Research and Technology Centre at Robert Bosch, India

Gurulingesh Raravi Distributed and Mobile Computing group,

in Xerox Research Center India

Mircea Negrean IAV GmbH, Germany

#### **Demos**

Chaired by Sophie Quinton, Inria Grenoble Rhône-Alpes, France.

Luís Almeida University of Porto, Portugal

Loïc Fejoz RealTime-at-Work, France

Daniel Lohmann Friedrich-Alexander-Universitt Erlangen-Nrnberg, Germany

Martina Maggio Lund University, Sweden

Gabriel Parmer George Washington University, USA

Insik Shin KAIST, Korea

Marcus Völp University of Luxemburg, Luxemburg

Dirk Ziegenbein Bosch GmbH, Germany

### **Table of Contents**

| Work-in-Progress                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Towards Parallelizing Legacy Embedded Control Software Using the LE Programming Paradigm  Julien Hennig, Hermann von Hasseln, Hassan Mohammad, Stefan Resmerita, Stefan Lukesch and Andreas Naderlinger |

| Towards Correct Transformation: From High-Level Models to Time-Triggered Implementations  Hela Guesmi, Belgacem Ben Hedi, Simon Bliudze, Mathieu Jan and Saddek Bensalem 1                              |

| Slot-Level Time-Triggered Scheduling on COTS Multicore Platform wit<br>Resource Contentions<br>Ankit Agrawal, Gerhard Fohler, Jan Nowotsch, Sascha Uhrig and Michael Paulitsch . 1                      |

| Scheduling of Multi-Threaded Tasks to Reduce Intra-Task Cache Contention  Corey Tessler and Nathan Fisher                                                                                               |

| I/O Contention Aware Mapping of Multi-Criticalities Real-Time Application over Many-Core Architectures  Laure Abdallah, Mathieu Jan, Jérôme Ermont and Christian Fraboul                                |

| Memory-aware Response Time Analysis for P-FRP Tasks  Xingliang Zou and Albert M. K. Cheng                                                                                                               |

| Cache Persistence Aware Response Time Analysis for Fixed Priorit Preemptive Systems  Syed Aftab Rashid, Geoffrey Nelissen and Eduardo Tovar                                                             |

| An Optimizing Framework for Real-time Scheduling Sakthivel Manikandan Sundharam, Sebastian Altmeyer and Nicolas Navet                                                                                   |

| Preliminary Performance Evaluation of HEF Scheduling Algorithm  Carlos A. Rincon and Albert M. K. Cheng                                                                                                 |

| Using Linked List in Exact Schedulability Tests for Fixed Priority Scheduling Jiaming Lv, Yu Jiang, Xingliang Zou and Albert M. K. Cheng                                                                |

| Online Semi-Partitioned Multiprocessor Scheduling of Soft Real-Time Periodic Tasks for QoS Optimization  Behnaz Sanati and Albert M. K. Cheng                                                           |

| Towards Worst-Case Bounds Analysis of the IEEE 802.15.4e  Harrison Kurunathan, Ricardo Severino, Anis Koubaa and Eduardo Tovar                                                                          |

### Demos

| TEMPO: Integrating Scheduling Analysis in the Industrial Design Practices Rafik Henia, Laurent Rioux, Nicolas Sordon                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications of the CPAL Language to Model, Simulate and Program Cyber-Physical Systems  Loïc Fejoz, Nicolas Navet, Sakthivel Manikandan Sundharam and Sebastian Altmeyer 59 |

| Demonstration of the FMTV 2016 Timing Verification Challenge  Arne Hamann, Dirk Ziegenbein, Simon Kramer and Martin Lukasiewycz                                              |

| Response-Time Analysis for Task Chains in Communicating Threads with pyCPA  Johannes Schlatow, Jonas Peeck and Rolf Ernst                                                    |

| Run-Time Monitoring Environments for Real-Time and Safety Critical Systems  Geoffrey Nelissen, Humberto Carvalho, David Pereira and Eduardo Tovar                            |

| Timing Aware Hardware Virtualization on the L4Re Microkernel Systems  Adam Lackorzynski and Alexander Warg                                                                   |

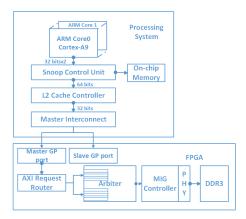

| Predictable SoC Architecture Based on COTS Multi-Core Nitin Shivaraman, Sriram Vasudevan and Arvind Easwaran                                                                 |

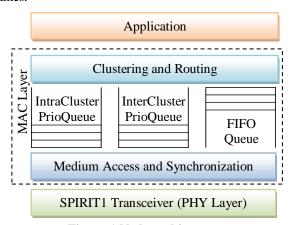

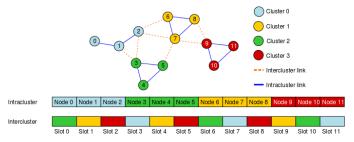

| A Real-Time Low Datarate Protocol for Cooperative Mobile Robot Teams  Gaetano Patti, Giovanni Muscato, Nunzio Abbate and Lucia Lo Bello                                      |

Work-in-Progress Papers

# Towards Parallelizing Legacy Embedded Control Software Using the LET Programming Paradigm

Julien Hennig, Hermann v. Hasseln, Hassan Mohammad Stefan Resmerita, Stefan Lukesch, Andreas Naderlinger

Daimler AG

Department of Computer Sciences, University of Salzburg

Email: {julien.hennig, hermann.v.hasseln, hassan.mohammad} Email: {stefan.resmerita, stefan.lukesch, andreas.naderlinger} @daimler.com @cs.uni-salzburg.at

Abstract—The growing demand for computing power in automotive applications can only be satisfied by embedded multi-core processors. Significant parts of such applications include OEMowned legacy software, which has been developed for singlecore platforms. While the OEM is faced with the issues of parallelizing the software and specifying the requirements to the ECU supplier, the latter has to deal with implementing the required parallelization within the integrated system. The Logical Execution Time (LET) paradigm addresses these concerns in a clear conceptual framework. We present here initial steps for applying the LET model in this respect: (1) Parallelization of legacy embedded control software, by exploiting existing inherent parallelism. The application software remains unchanged, as adaptations are only made to the middleware. (2) Using the LET programming model to ensure that the parallelized software has a correct functional and temporal behavior. The Timing Definition Language (TDL) and associated tools are employed to specify LET-based requirements, and to generate system components that ensure LET behavior. The work describes two conceptual ways for integrating TDL components in AUTOSAR.

#### I. INTRODUCTION

By now the multi-core revolution has hit embedded computing full force. Most embedded microcontroller manufacturers offer multi-core based architectures as part of their mid and high-end lineups. As was the case for mainstream computing, porting, transforming and rewriting substantial legacy software to make effective use of the new processors' parallelism is trailing the advent of the new architectures. Parallelizing proven-in-use time-critical embedded control software is posing significant challenges that call for rigorous software design patterns and programming models. For a number of years, we participated in industrial development projects implementing real-time control applications for first-of-their-kind multi-corebased electronic control units (ECUs) in the chassis, driverassistance and powertrain domains. We saw two distinct activities involved in such implementation efforts. The first activity is to expose parallelism in the legacy single-core application software by transforming the code to eliminate dependencies between individual functions. A functional redesign and parallelization of compute intensive parts is ideally avoided and only attempted when resource constraints demand even more parallelism. The second activity is to implement the exposed parallelism using specific implementation patterns that guarantee time- and value-deterministic parallel execution on the targeted multi-core processor. We observed that most of these

patterns had coordination regimes in common where state variables are updated and buffered at controlled instances in time, typically at the beginning or at the end of periodic tasks. These patterns were typically deeply project and supplier-specific and often lacked formal foundations. An automotive OEM has to consider that significant amounts of OEM-owned application software is integrated as part of a supplier-owned execution platform. It is mandatory for the OEM that changing a supplier does not result in having to redesign the application software due to supplier-specific implementation patterns. Therefore, when we found that many implementation patterns shared key concepts of the LET programming model [1] we set out to evaluate seriously whether (1) LET could be an efficient and effective basis for implementing parallel execution of periodic control functions and (2) whether such an implementation could be integrated with the runtime facilities of an important automotive software standard AUTOSAR [2]. If successful, the LET paradigm would also offer the added advantage to extend naturally to the coordination of time triggered event chains which are distributed across multiple interconnected ECUs. Predictable behavior of such distributed event chains is becoming more and more important with the growing sophistication of vehicle control functions.

The main contribution of this paper thus consists in describing first significant steps towards LET implementations for multi-core architectures using facilities of the automotive industry standard AUTOSAR. After describing a legacy powertrain control application, we sketch our approach to expose its parallelism. Then we outline the steps taken to implement the exposed parallelism using the Timing Definition Language (TDL) as an implementation of the LET programming model. We conclude with some preliminary results and a summary of next steps.

#### II. RELATED WORK

The quest for achieving predictable behavior in embedded systems is not new [3]. Embedded multi-core processors aggravate this problem to the point where rigorous restrictions at all levels of system design are required in order to have any hope for success [4]. The LET paradigm has been designed from the beginning to be a programming model that provides a basis for predictable behavior both at the design and at the implementation level [5]. The LET paradigm was and typically

still is met with healthy skepticism by the real-time and embedded community because of its underlying restrictions concerning general expressiveness and WCET estimate requirements and the hard to afford computational costs regarding buffer space and execution time in particular. But a recent application of the LET programming model to an industrial engine control software for a single-core execution platform has shown that these overhead costs can be controlled [6]. [6] also illustrates that a process for applying the LET paradigm exists by which legacy software can be transformed iteratively. At the same time, LET gains popularity again as a design principle to analyze and engineer real-time control systems [7]. Existing AUTOSAR timing services are still insufficient to support the LET model. Elements of LET were behind an early AUTOSAR concept proposal "Support for Predictable Software Execution" [8] but this concept eventually didn't receive enough support to be pursued further. If the experiment we describe in this paper is successful, we hope to revive this AUTOSAR community effort.

#### III. POWERTRAIN CONTROL CASE STUDY

The subject of our LET based parallelization effort is the central coordinator of an electric powertrain. Its core responsibility is command and control of a predictive operating strategy for the components of an electric powertrain: inverter, battery, auxiliaries, vehicle interface. A supplier is responsible for the ECU hardware and the AUTOSAR basic software (BSW) as well as for functions that directly interface with the ECU hardware. The supplier also provides an AUTOSAR compliant execution environment for integrating the application software (ASW). The ASW itself is developed by Mercedes-Benz and consists mainly of torque coordination, energy management, thermal management, auxiliary management, prediction and monitoring. The C functions that implement these features are called from a single fixed-period OS task. A reduced call rate is hard-coded in the OS task for each function whose period is a multiple of the base period. At the beginning of the task, task-external input from sensors and from the attached networks is processed, then the application functions are executed in a predefined static order, and finally output signals are processed and propagated either to their respective actuators or to the network. I/O itself is carefully coordinated either synchronously (polling) or asynchronously (interrupt based). This is a proven and pervasive software execution pattern for single-core embedded control units from which we would not want to deviate were it not for the fact that in the not too distant future single-core performance will no longer suffice for implementing advanced and innovative powertrain control features. We are thus faced with the typical exercise of parallelizing legacy software: partition the main task into independent subtasks which can be executed in parallel without affecting the overall functional correctness that is partly incorporated in the static execution order and the explicit or implicit dependencies between the individual functions.

#### IV. TOWARDS PARALLELIZATION

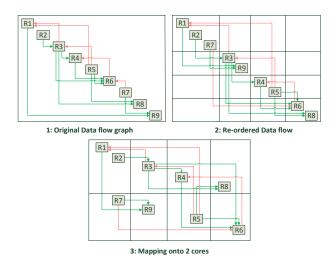

To achieve the most possible parallelization in our legcy software, we present a method which is mainly an application of [9]. Neither the functional architecture nor the software architecture of the legacy code was designed to support a distribution on cores of a multi-core processor. Nevertheless, since the code consists of a large number of 'elementary' software modules, or runnables, the dataflow architecture should be rich enough in structure to identify sufficient parallelism among the runnables to foster a possible distribution on cores. The dataflow architecture is represented as a graph, consisting of nodes identified as the runnables, and directed edges identified as global variables for data exchange among runnables. Assuming that runnables are mapped onto periodic tasks for implementation, forward dependencies represent data exchanges updated in the same cycle of the task, whereas backward dependencies represent variables updated during the next cycle of the task. The goal is to maximize inherent parallelism by identifying subsets ('clusters') of totally independent runnables. Manipulation of the graph are made possible, by allowing backward dependencies to be changed to forward dependencies while maintaining all forward dependencies. Concretely, the method consists of the following three steps (cf. Fig. 1):

- 1.) For the set of runnables mapped onto a periodic task, the corresponding dataflow graph with forward and backward dependencies has to be identified.

- 2.) In application of the procedure given in [9], with the additional requirement that there are no forward and no backward dependencies among runnables of a cluster, we start with the identification of 'starting nodes' of the data flow graph. A starting node is a node with no dependent predecessor nodes. After this first step, all edges from the runnables in this cluster are removed such that a set of new starting nodes emerge. This is continued until all nodes have been visited. From inspection of the first part of Fig. 1 we see that runnables R1, R2 and R7 satisfy our conditions and define therefore our first cluster. In the next step we remove all edges from runnables R1, R2 and R7, and find the next subset of starting nodes. These are runnables R3 and R9. Going to all nodes we eventually arrive at a clustering shown in the second part of Fig. 1. This procedure can of course be done manually as well as automatically.

- 3.) Since the runnables in each cluster are totally independent, the chronological sequence in which they are executed is arbitrary, and in particular they can be executed in parallel. These sets are then subject to distribution on cores of a multicore processor, as shown in the third part of Fig. 1, where a distribution on two cores is shown. This distribution of the independent runnables should in further steps be subject to more considerations, e.g., measured executions times of the runnables on a certain processor, number of dependencies among different cluster and thus generated cross-core overhead, functional and non-functional requirements, and further system-level considerations.

Figure 1. Parallelization with Data Flow Graph

#### V. TDL FOR AUTOSAR PARALLEL LEGACY SOFTWARE

TDL allows specification and implementation of timing properties of real-time applications according to the Logical Execution Time (LET) paradigm. In the LET programming model, a fixed logical duration is associated to each execution of a computational unit, or task [1]. The inputs of the task's execution are those available at the LET start and the outputs of the task's execution are made available at the LET end. Thus, the LET model achieves a pre-specified, platform-independent observable temporal behavior of a set of software functions, leading to both time and value determinism [5].

The top-level unit in TDL is called a module, which contains declarations of sensors, actuators, tasks, and modes. Sensors and actuators model data sources and sinks, respectively; they are employed to communicate with the environment. A task declaration specifies an application function as well as corresponding input and output ports. A mode is a periodic sequence of activities: task LET instances, actuator updates, and mode switches. Mode activities are carried out by a runtime system (virtual machine) called E-machine. More details about TDL can be found in [10].

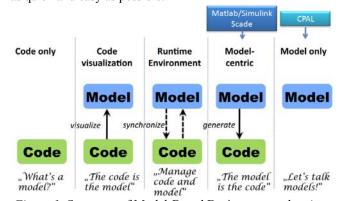

#### A. TDL Modeling of Legacy Systems

TDL is accompanied by a commercial tool suite that can be integrated in top-down, model-based development processes, as well as in bottom-up, legacy-based development. The tool suite supports four development stages, which are described for the legacy case below.

1) Programming: The TDL program can be automatically generated from legacy information about the application functions associated with TDL tasks such as: connectivity, execution sequencing, periodicity, execution time (WCRT), and distribution on cores in a multi-core system, or on nodes in a distributed system. The resulting TDL program satisfies the legacy constraints (e.g., execution sequencing is preserved) and may include default LETs generated according to a user-specified policy (e.g., LET=WCRT). The user may then

manually adjust LET values, e.g., by increasing some LETs in order to increase robustness against future additions of new functionality.

- 2) Distribution and scheduling: Mapping of TDL modules to computational nodes and cores is performed. Network communication schedules can also be generated in this step.

- 3) Code generation: The following runtime components are generated.

- The timing code, also called E-code, is compiled from the TDL program. The E-code is interpreted by the E-machine at runtime, triggering executions of LET start and LET end operations.

- Functions for implementing LET start and LET end operations for each TDL task, also called LET drivers. In order to achieve the LET data transfer semantics, certain legacy variables may need to be buffered. Input variables are buffered at the LET start of a task, while output variables are buffered throughout the execution and updated at the LET end. Optimization algorithms are put in place for minimizing the buffering.

- Setter/getter functions for the legacy variables that are subject to buffering requirements.

- 4) *Integration:* The integration of TDL components affects all levels of the legacy system.

- The E-machine employs some timing measurement capability of the hardware a programmable timer, typically. The E-machine is executed within an interrupt service routine triggered by the timer.

- LET drivers are included in dedicated high-priority OS tasks, synchronized with the E-machine. Each LET driver task is also synchronized with OS tasks containing TDL-modeled legacy functions.

- The generated setter/getter functions are integrated at the application level.

#### B. TDL Modeling of Parallelized Powertrain Control Software

Consider a legacy application with a parallelization structure as described in section IV. Assume that a cluster contains runnables with the same execution period (otherwise split the clusters accordingly). We propose the following TDL-based procedure for deploying the application on a platform with ncores. First, assign to each cluster a number of n TDL tasks (one per core) with the same LET, then group the runnables of the cluster into n sequences and associate each sequence to a TDL task. If execution time information is available per runnable, then this grouping can be done such that the resultant LET value is minimized, which means core load is balanced within the LET and data propagation delay is minimized. In general, other (non-TDL) criteria may be considered in the assignment of runnables to cores - for example, one may wish to reduce inter-core communication by allocating runnables from different clusters with intensive data transfer to the same

The TDL program is generated such that the task's LETs are sequenced according to data dependencies between clusters. A TDL module contains then all the TDL tasks allocated

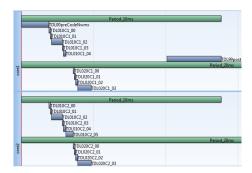

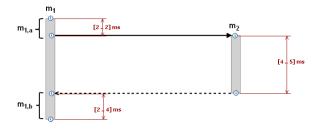

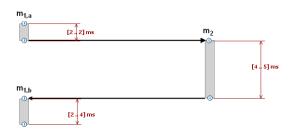

Figure 2. Visualization of a TDL program example

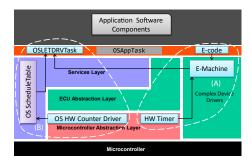

Figure 3. Integration of TDL in AUTOSAR with the two alternatives for the E-machine

to the same core. In the second stage, the module-to-core mapping is done by specifying the actual cores. In the third stage, a buffer analysis step determines a minimal number of legacy variables that must be buffered. In general, this is the case for communication variables between concurrent TDL tasks with overlapping LETs. Fig. 2 shows an extract from a TDL program, consisting of TDL tasks with periods 10ms and 20ms. The full program has 31 TDL tasks mapped to two cores, with  $LET = 3 \cdot WCET$ , plus rounding for alignment. The number of variables for inter-task communication exceeds 1500, of which only 7 need to be buffered.

In the fourth stage, integration of setter/getter functions is easily done by re-defining the implementations of ports and connections between AUTOSAR software components. LET drivers and E-code are included in the RTE. AUTOSAR OS events are employed for synchronization between the E-machine, the LET driver OS tasks, and the legacy OS tasks.

We are currently investigating two ways of integrating the E-machine into an AUTOSAR environment: (A) as a complex device driver (CDD) and (B) via OS schedule tables - see Fig. 3. The E-machine as CDD represents an additional basic software component that is able to deal with TDL programs of arbitrary complexity (in terms of modal structure and number of TDL tasks). The E-machine as OS schedule tables requires no additional AUTOSAR service or interface, but scalability is a concern that needs to be further investigated.

#### VI. CONCLUSION AND FUTURE WORK

This paper describes an approach for distributing single-core legacy software on a multi-core platform, where the application source code is kept unchanged by using runnables as the granularity for distribution. In order to ensure functional correctness, dataflow constraints across parallel execution threads are guaranteed by employing a multi-core implementation of the LET programming model. This is provided by the Timing Definition Language (TDL) and its tool suite. First analysis results indicate that the TDL overhead can be controlled to acceptable levels. Furthermore, we describe primary concepts for integrating the LET paradigm within AUTOSAR.

In the next steps, we will evaluate TDL runtime overhead and resource usage on a prototype system. We will investigate policies for choosing LET values, and for dealing with LET exceptions (violations of LET specifications). Further research will extend the approach to distributed functions, with components running on different nodes of a network (e.g., FlexRay or Ethernet).

Special attention will be dedicated to paving the way for LET standardization as part of AUTOSAR. We consider that there is enough room for different LET implementation techniques, in keeping with the AUTOSAR motto "cooperate on standards, compete on implementation". The main challenge is to gather convincing evidence that LET addresses a variety of use cases, involving different HW configurations (single- and multi-core, networked ECUs), software development processes (model-based design, including legacy software, simulation and testing, debugging), and industry players (OEMs, system suppliers, HW vendors).

#### REFERENCES

- T. Henzinger, B. Horowitz, and C. Kirsch, "Giotto: A time-triggered language for embedded programming," *Proceedings of the IEEE*, vol. 91, pp. 84–99, January 2003.

- [2] AUTOSAR, "AUTomotive Open System ARchitecture," http://www.autosar.org/, accessed: 2016-01-11.

- [3] P. Axer, R. Ernst, H. Falk, A. Girault, D. Grund, N. Guan, B. Jonsson, P. Marwedel, J. Reineke, C. Rochange et al., "Building timing predictable embedded systems," ACM Transactions on Embedded Computing Systems (TECS), vol. 13, no. 4, p. 82, 2014.

- [4] C. Cullmann, C. Ferdinand, G. Gebhard, D. Grund, C. Maiza, J. Reineke, B. Triquet, and R. Wilhelm, "Predictability considerations in the design of multi-core embedded systems," *Proceedings of Embedded Real Time Software and Systems*, pp. 36–42, 2010.

- [5] T. A. Henzinger, "Two challenges in embedded systems design: predictability and robustness," *Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences*, vol. 366, no. 1881, pp. 3727–3736, 2008.

- [6] S. Resmerita, A. Naderlinger, M. Huber, K. Butts, and W. Pree, "Applying real-time programming to legacy embedded control software," in *Real-Time Distributed Computing (ISORC)*, 2015 IEEE 18th International Symposium on. IEEE, 2015, pp. 1–8.

- [7] D. Ziegenbein and A. Hamann, "Timing-aware control software design for automotive systems," in *Proceedings of the 52nd Annual Design Automation Conference*. ACM, 2015, p. 56.

- [8] C. Aussaguès, "Deterministic and dependable (also known as predictable and robust) embedded real-time systems.....with the OASIS and PharOS technology," 2012, invited Talk at the 17th IEEE International Conference on Engineering of Complex Computer Systems.

- [9] T. C. Hu, "Parallel sequencing and assembly line problems," *Operations research*, vol. 9, no. 6, pp. 841–848, 1961.

- [10] J. Templ, "Timing Definition Language (TDL) 1.5 specification," University of Salzburg, Tech. Rep. T024, July 2009, http://www.softwareresearch.net.

# Towards Correct Transformation: From High-Level Models to Time-Triggered Implementations

Hela Guesmi\*, Belgacem Ben Hedia\*, Simon Bliudze<sup>†</sup>, Mathieu Jan\* and Saddek Bensalem<sup>‡</sup>

Abstract-In embedded systems, high-level component-based design approaches have been proposed in order to allow specification and design of complex real-time systems. However, their final implementations mostly rely on the generation of code for generic execution platforms. On the other hand, a variety of Real-Time Operating System (RTOS), in particular when based on the Time-Triggered (TT) paradigm, guarantee the temporal and behavioural determinism of the executed software. However, these TT-based RTOS do not provide high-level design frameworks enabling the scalable design of complex safety-critical realtime systems. The goal of our work is to couple a high-level component-based design approach based on the RT-BIP (Real-Time Behaviour-Interaction-Priority) framework with a safetyoriented real-time execution platform, implementing the TT approach. Thus, we combine their complementary advantages, by deriving correct-by-construction TT implementations from highlevel componentised models. To this end, we propose an automatic transformation process from RT-BIP models into applications for the target platform based on the TT execution model. This transformation is already partially implemented.

#### I. INTRODUCTION

The Time-Triggered (TT) paradigm for the design of realtime systems was introduced by Kopetz [11]. TT systems are based on a periodic clock synchronization in order to enable a TT communication and computation. Each subsystem of a TT architecture is isolated by a so-called *temporal firewall*. It consists of a shared memory element for unidirectional exchange of information between sender and receiver task components. It is the responsibility of the *TT communication* system to transport, by relying on the common global time, the information from the sender firewall to the receiver firewall. The strong isolation provided by the temporal firewall is key to ensuring the determinism of task execution and, thereby, allowing the implementation of efficient scheduling policies.

Developing embedded real-time systems based on the TT paradigm is a challenging task due to the increasing complexity of such systems and the necessity to manage, already in the programming model, the fine-grained temporal constraints and the low-level communication primitives imposed by the temporal firewall abstraction. Several Real-Time Operating Systems (RTOS) implement the TT execution model, such as for instance [3], [10]. However, they do not provide high-level programming models that would allow the developers to think on a higher level of abstraction and to tackle the complexity of large safety-critical real-time systems. Model-based design

frameworks, such as [1], [7], allow the specification, the design and the simulation of real-time systems. In particular, the framework of [1] is a component-based framework for the design of real-time systems. It allows verification of behavioural properties, such as deadlock-freedom, and lends itself well to model transformations.

To the best of our knowledge, few connections however exist between high-level component-based design frameworksand TT execution platforms. A model transformation for generating distributed implementations from (non-real-time) BIP models is presented in [5]. A method for generating a mixed hardware/software system model for many-core platforms from a high-level non-real-time application model and a mapping between software and hardware components is presented in [8]. Nevertheless, these two approaches do not target the platforms based on TT execution model, thereby falling short of exploiting the strong temporal determinism guaranteed by the latter. A design framework based on UML diagrams and targeting the TT architecture is presented in [13]. [4] presents a transformation from SCADE [7] to PharOS [3]. The former does not target generic TT implementations since it assumes the underlying TT protocol to be the FlexRay standard, while the latter is limited to the relatively simple temporal behaviours. [6] presents a method to reduce the gap between models used for timing analysis and for TT code generation. Nevertheless, these approaches do not rely on a single semantic framework.

In this work, we establish a link between the model-based design framework RT-BIP [1] and a RTOS based on TT approach. Generating TT implementations from high-level RT-BIP models is achieved by a two-step transformation. The first step [9] transforms a generic RT-BIP model into a restricted one, which lends itself well to an implementation based on TT communication primitives. The second step, which is the subject of this paper, transforms the resulting model into the TT implementation provided by the PharOS RTOS. We identify the key difficulties in defining this transformation, propose solutions to address these difficulties and study how this transformation can be proven to be semantics-preserving.

This paper is structured as follows. In Section II, we provide the necessary background on RT-BIP and PharOS. The transformation is presented in Section III, while the open issues that remain to be addressed are discussed in Section IV.

#### II. BACKGROUND

#### A. The RT-BIP Component Framework

RT-BIP is a component framework for constructing systems by superposing three layers of modelling: Behaviour, Interaction, and Priority. The Behaviour layer consists of a set of components represented by timed automata extended by data and functions given in C. The Interaction layer describes possible interactions between atomic components. Interactions are sets of ports allowing synchronizations between components. The third layer includes priorities between interactions using mechanisms for conflict resolution. Thus, in RT-BIP, systems are built by composing *atomic components* with *interactions* (presented by *connectors*) and *priorities*.

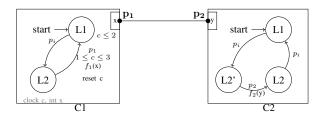

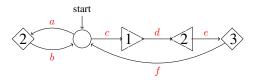

A component in RT-BIP is essentially a timed automaton [2] labelled by ports that represent the component's interface for communication with other components. A transition in RT-BIP automata can be constrained by a guard, i.e., a predicate on a set of its variables. A transition can also be constrained by timing constraint tc which is a guard over a set of clocks. Timing constraint is used to specify when actions of a system are enabled regarding system clocks. If c is a clock, a timing constraint tc over c is of the form:  $l_c \leq c \leq u_c$ , where  $l_c, u_c \in \mathbb{R}_+$ . Furthermore, in RT-BIP automata, a state l can be constrained by a time progress conditions (tpc) used to specify whether time can progress at a given state of the system. Any time progress condition tpc can be written as:  $tpc = c \le u_c$ , where  $u_c \in \mathbb{R}_+ \cup \{+\infty\}$ . In the example of Figure 1, we display two RT-BIP components C1 and C2, composed by a binary connector. Let us assume that the system reaches the state L1 of C1 with a tpc equals to  $c \le 2$  and  $c \in [1, 2]$ . It can then either let the time progress until c=2, or execute the transition enabled for these instants. If the state L1 is reached when c=2, the system can not let time progress. It has to execute the transition  $p_1$ .

Fig. 1. Example of RT-BIP automata

#### B. TCA computation model and PharOS platform

Time-Constrained Automata (TCA) [12] is a formal computation model of TT tasks. The temporal behaviour of a task is specified using a directed graph, where arcs represent the successive jobs of the task to be executed (one at a time), and the nodes bear the temporal constraints of the jobs. There are four kinds of nodes:

After node (after(d)): defines d as the relative release date of the following job. It is symbolized by ▷<sub>d</sub>;

- Before node (before(d)): defines d as the relative deadline of the preceding job. It is symbolized by ⊲<sub>d</sub>;

- Advance node (advance(d)): is a combination of ▷<sub>d</sub> and

¬d nodes. It is symbolized by ¬¬d and defines the absolute visibility date of the job data;

- No constraint node: imposes no temporal constraints on preceding and following jobs. It is symbolized by o<sub>d</sub>.

A job can consult data whose absolute visibility dates are less or equal than the absolute release date of the job. The execution of an application can be seen as cyclically walking in the graph of each task and let the underlying scheduler choose when each encountered job is actually executed in the time interval defined by its release date and its deadline.

In the TCA example displayed in Figure 2, we have six jobs, labelled a to f, and five nodes. The release date of job d is one unit of time after the previous advance node. Two units of time after, job d should have ended. After jobs e and a are executed, communications take place since an advance node is used. The visibility date of data produced by e is three units of time later the previous after node.

Fig. 2. Example of TCA automata

TCA computation model is implemented in PharOS [3]. PharOS is a method to design, implement and execute safety-critical multitasking applications based on the time-triggered paradigm. PharOS implements different variants of TT communication mechanisms. We are specially interested in the *temporal variables* which are real-time data flows. Values, available to all agents, are stored and updated by a single writer –the owner agent– at a predetermined temporal rhythm.

#### III. WORK-IN-PROGRESS: FROM RT-BIP TO PHAROS

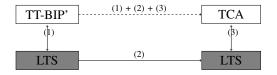

In order to derive TT implementation from a high-level RT-BIP model, we follow a two-step transformation (see Figure 3).

Step1: RT-BIP model adaptation. This transformation consists in adapting the initial model, in order to comply with the TT paradigm, and especially the TT communication pattern. Each intertask interaction –initially held by connectors– is transformed in order to be handled by a dedicated component, standing for a medium between communicating tasks. The obtained model consists only of atomic RT-BIP components and connectors allowing unidirectional data transfer. Ports in TT-BIP model are send, receive or internal ports. This transformation is published in a previous work [9], and is proven to be semantics preserving.

**Step 2: RT-BIP to TCA transformation.** In this step, the output of the previous step is transformed into TCA automaton. In this section, we first detail challenges of the second step transformation. Then, we present the actual algorithm and how we are going to tackle the correctness proof part.

$$\boxed{\text{RT-BIP}} \xrightarrow{\text{step 1}} \boxed{\text{TT-BIP}} \xrightarrow{\text{step 2}} \boxed{\text{TCA}}$$

Fig. 3. From RT-BIP to the TCA TT computation model: a 2-step transformation.

#### A. Transformation subtleties

Transforming a component-based high-level model into a RTOS based system requires to address several subtleties.

Timing constraints mapping subtlety. The initial TT-BIP model is based on an abstract notion of time. In particular, it assumes that actions, corresponding to the computational steps of the system, are atomic and have zero execution times. Only start instant of these actions have timing constraints (tc) and timing progress conditions (tpc). However in TCA models, both release date and deadline of actions can be specified.

This issue is addressed by making use of the tpc notion in TT-BIP model, in order to extract the deadline of the following action. In fact the semantics of the tpc (used to specify whether time can progress at a given state of the system) and the before node in TCA are strictly similar. Both of them constraint the action preceding the node to finish before a certain date. The action succeeding the node starts right after the previous one. Timing constraint  $l_c \leq c \leq u_c$  in TT-BIP, constrains only the start instant of the transition. In order to keep the same semantics in TCA, an empty action can be executed between nodes  $after(l_c)$  and  $before(u_c)$ . Right after, the actions of the initial transition can be executed.

From absolute to relative constraints subtlety. In TT-BIP, all constraints are defined using absolute labelling. However, TCA nodes bear only relatively expressed constraints, i.e., as an increment to the previous  $\triangleright_d$  or  $\diamond_d$  node.

In order to address this second issue, we make use of the variable  $d_{ref}$ . It is initiated to zero and updated whenever a *before* node is instantiated. It stores then the current local clock value. Relative constraint  $(d_{relative})$  is computed from its corresponding absolute constraint  $(d_{absolute})$  following this formula:

$$d_{relative} = d_{absolute} - d_{ref} \tag{1}$$

Communication mapping subtlety. In the initial TT-BIP model, all tasks are related to communication components via connectors. Connectors provide not only unidirectional data transfer but also synchronization between sending and receiving actions of respectively the sender and the receiver components. In TCA, one communication model is called *temporal variable*. New values of temporal variables are made visible by their owners, i.e senders, at each of their synchronization points. Receivers of these data can consult their new values when their current time is equal or higher to the timing of these synchronization points. In our transformation two requirements need to be satisfied; (1) the receive must consult an updated temporal variable (i.e., after the sending action of the sender task) and (2) we need to respect communication semantics of the initial model.

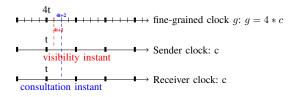

This subtlety is addressed by generating TCA synchronization points (advance nodes) that depends on whether the TT-BIP transition is triggered by a send, receive or an internal port. After each nodes that corresponds to a communicating transition we instantiate an advance(n) node defined over a fine-grained clock. For example let a sender and receiver components having the same clock, and suppose they are meant to communicate in the same instant t in TT-BIP model. We can define a smaller clock, allowing to instantiate advance nodes (send and receive) at  $t+\epsilon$ . If we take the example of time lines displayed in Figure 4, the visibility instant of the sender data is 4\*t+1 of the clock g. The receiver will consult these data in the instant 4\*t+2 of the clock g.

Fig. 4. Example of advance nodes defines on a fine-grained clock.

#### B. Transformation Algorithm

In Algorithm 1, for each transition of each automaton in TT-BIP model, we check if the transition source state has a tpc constraint. If this constraint exists, we instantiate a before node defined on the relative bound instant of this tpc. This before node defines the deadline of the previous action. The out transition of that node executes actions of the initial TT-BIP transition. If the transition source state tpc does not exist, and

```

Algorithm 1 Translation algorithm: Step 1

d_{ref} = 0;

for t=transition do

if t.source.hasTpc then

newTcaNode(before(t.source.tpc.value - d_{ref}));

Synchro(t.labelPort);

newOutTransition(t.actions);

else if t.hasConstraint then

newTcaNode(after(t.constraint.lowBound - d_{ref}));

newOutTransition(update(d_{ref}));

newTcaNode(before(t.constraint.upBound - d_{ref}));

Synchro(t.labelPort);

newOutTransition(t.actions);

else

newTcaNode(NoConstraint());

Synchro(t.labelPort);

newOutTransition(t.actions);

```

a timing constraint is defined over the transition, we instantiate two consecutive *after* and *before* nodes, defined successively over the lower and the upper bounds of the timing constraint of the initial transition. The transition relating these two states executes no actions. And then, we instantiate a transition to execute the initial actions. If neither tpc nor timing constraint are defined in the initial automata, a node with no constraint is instantiated. Its out transition executes the initial actions.

NewTcaNode() and newOutTransition() functions and different considered cases answer to the first subtlety of the transformation. The use of the variable  $d_{ref}$  and update( $d_{ref}$ ) function goes with solving the second subtlety.

The Synchro() function in algorithm 1, answers to the third issue. It is responsible of adding synchronization points depending on if the transition is triggered by a send, receive or an internal port. Mainly it instantiates after/before variables updating, the suitable advance node bearing a well defined label at the rhythm of a fine-grained clock. The computation of the relation between the task clock and the fine-grained clock as well as the constraint supported by each instantiated advance node are subject of ongoing work.

#### C. Approach to prove the transformation correctness

An essential point to the transformation correctness proof approach is that the semantics of an RT-BIP component is defined as a Labelled Transition System (LTS).

In order to prove this correctness, we follow the method displayed in Figure 5. In this method we (i) express the semantics of TCA models in terms of LTS, (ii) consider the transformation between LTSs instead of the transformation between models directly and (iii) we prove that this transformation is semantics preserving using weak bisimulation technique. Then the direct transformation between models is correct by construction. This correctness proof method

Fig. 5. Approach of the transformation correctness proof.

concerns correctness between an atomic component of TT-BIP model and its associated TCA model. However, to prove that the hole TT-BIP model is equivalent to the set of the obtained TCA models and their communication system calls, we need to prove that synchronization points preserve the same production/consumption order as in the initial model.

#### IV. OPEN CHALLENGES

We have identified several open challenges that we believe should be addressed when defining an optimized and generic transformation process.

Identification of OS service patterns potentially existing in the initial model: any OS has a number of services (communication, synchronization, etc.). We strongly think that in some initial models, and in components intended for handling communication, we can identify exactly the same behavioural pattern of one or more OS services. Transformation should take this redundancy into account, and only transform into TCA automata the part of the component which can not be

mapped into an OS services. The identified pattern is thus mapped to a system call.

What about a generic transformation process? We strongly believe that the transformation process defined above can be generalized to any RTOS-based implementation approach with TT execution model. In fact, we just need to present the semantics of the computation model of the target platform as an LTS system.

#### V. CONCLUSION

In this paper we outline our approach to generate correct-by-construction TT implementation from high-level RT-BIP models. We divide this transformation into two steps; first we transform RT-BIP model in order to express intertask communication according to TT communication system, then we transform the obtained model into TCA automata (the computation model of PharOS applications). The first step is being done in previous work, we are now working on the second one. We define different subtleties induced by this transformation, and we give a short outline of the planned transformation strategy as well as the correctness proof process. We further identify open challenges related to our approach, that we plan to address with further research.

#### REFERENCES

- [1] Tesnim Abdellatif. Rigourous Implementation of Real-Time Systems. PhD thesis, UJF, 2012.

- [2] Rajeev Alur and David L Dill. A theory of timed automata. *Theoretical computer science*, 126(2):183–235, 1994.

- [3] C Aussagues, D Chabrol, V David, D Roux, N Willey, A Tournadre, and M Graniou. PharOS, a multicore OS ready for safety-related automotive systems: results and future prospects. *Proc. of The Embedded Real-Time* Software and Systems (ERTS2), 2010.

- [4] Simon Bliudze, Xavier Fornari, and Mathieu Jan. From model-based to real-time execution of safety-critical applications: Coupling SCADE with OASIS. In *Embedded Real Time Software and Systems*, ERTS2, page 10, February 2012.

- [5] Borzoo Bonakdarpour, Marius Bozga, Mohamad Jaber, Jean Quilbeuf, and Joseph Sifakis. From high-level component-based models to distributed implementations. In *Proceedings of the tenth ACM international conference on Embedded software*, pages 209–218. ACM, 2010.

- [6] Etienne Borde, Smail Rahmoun, Fabien Cadoret, Laurent Pautet, Frank Singhoff, and Pierre Dissaux. Architecture models refinement for fine grain timing analysis of embedded systems. In Rapid System Prototyping (RSP), 2014 25th IEEE International Symposium on, pages 44–50. IEEE, 2014

- [7] Jean-Louis Boulanger, François-Xavier Fornari, Jean-Louis Camus, and Bernard Dion. SCADE: Language and applications. 2015.

- [8] Paraskevas Bourgos. Rigorous Design Flow for Programming Manycore Platforms. PhD thesis, Grenoble, 2013.

- [9] Hela Guesmi, Belgacem Ben Hedia, Simon Bliudze, Saddek Bensalem, and Jacques Combaz. Towards time-triggered component-based system models. In *ICSEA15*, pages 157–169, Barcelone, Spain, November 2015. ThinkMind.

- [10] Robert Kaiser and Stephan Wagner. Evolution of the pikeos microkernel. In Proceedings of the 1st International Workshop on Microkernels for Embedded Systems, pages 50–57, 2007.

- [11] Hermann Kopetz. The time-triggered approach to real-time system design. Predictably Dependable Computing Systems. Springer, 1995.

- [12] Matthieu Lemerre, Vincent David, Christophe Aussaguès, and Guy Vidal-Naquet. An introduction to time-constrained automata. In Proc. of the 3<sup>rd</sup> Interaction and Concurrency Experience (ICE 2010), volume 38 of EPTCS, pages 83–98, 2010.

- [13] Kathy Dang Nguyen, PS Thiagarajan, and Weng-Fai Wong. A UML-based design framework for time-triggered applications. In *Real-Time Systems Symposium*, 2007. RTSS 2007. 28th IEEE International, pages 39–48. IEEE, 2007.

## Slot-Level Time-Triggered Scheduling on COTS Multicore Platform with Resource Contentions

Ankit Agrawal, Gerhard Fohler Chair of Real-Time Systems TU Kaiserslautern, Germany {agrawal,fohler}@eit.uni-kl.de Jan Nowotsch, Sascha Uhrig

Airbus Group Innovations

Munich, Germany

{jan.nowotsch,sascha.uhrig}@airbus.com

Michael Paulitsch Thales Austria GmbH Vienna, Austria michael.paulitsch@thalesgroup.com

#### I. INTRODUCTION AND MOTIVATION

A number of safety-critical domains, such as avionics, use time-triggered (TT) architectures for reasons of reliability, ease of certification, reduced integration and maintenance costs, system-wide determinism, etc. [1].

The move to multicore platforms poses a number of fundamental problems for real-time scheduling in particular, even in idealized scenarios without consideration of overheads or platform characteristics. COTS multicore platforms generally share various hardware resources such as on-chip network, memory sub-system etc. amongst cores, introducing resource contentions and inter-core interferences. This results in large variability in the execution time of a task depending on the latency and number of inter-core interferences from coexecuting tasks on the other cores. Further, the execution of each new task, in turn, introduces additional inter-core interferences, affecting the variability in execution time of already co-executing tasks. E.g., it is shown in [2] that the single store request latency increases by 25.82 times when the number of active cores are increased from 1 to 8.

These challenges effect TT systems even more, as schedules have to be determined offline. The extension of offline scheduling to multicore platforms raises great concern in safety-critical application domains using single core platforms. E.g., in the avionics domain, in which certification and long product life are essential, only very limited steps are currently considered: The position paper from EASA and FAA proposes, as next step, at most 2 active processing cores [3]. Even with only one core active, certification is a challenge.

The problem of scheduling for TT systems on COTS multicore platform considering inter-core interferences is difficult because of three primary reasons: Firstly, we need to provide guarantees that offline computed bounds on variability in execution time of each task will hold at runtime, warranting runtime regulation of inter-core interferences during task execution. Secondly, we need to bound the variability in execution time of a task in the offline phase considering possible runtime inter-core interferences and task's deadline, as reserving hardware resources for each task considering worst-case inter-

core interferences would be very pessimistic. Finally, we need to estimate at design time the maximum runtime inter-core interferences for each task in each slot, as we cannot obtain this information using traditional static WCET analysis tools due to unavailability of architecture models for the complex COTS multicore processors.

Related Work In [4], Yun et al. propose controlling memory accesses from all but one cores to limit inter-core interferences experienced by hard real-time tasks executing on just 1 core. Yun et al. extended the work in [5] allowing all cores to execute hard real-time tasks by regulating memory accesses using a memory server on each core. However, they assume that the given memory server budget reservations for each core are constant for each server period. Yao et al. [6] present a method to bound variability in execution time of each task on all cores considering round-robin arbitration between cores for memory accesses. However, the work does not consider additional arbitration and contention delay introduced by shared on-chip network in the analysis. In [2], [7], Nowotsch et al. consider a timeline divided into unequal length process frames and provide a method that bounds variability in execution time of each task in a given process frame by considering maximum inter-core interferences in the offline phase. The runtime mechanism enforces the offline computed bound in each process frame. However, they impose restrictions such as a new task is only allowed to execute on the completion of all tasks in a process frame.

A common way of operation in TT systems is to assume a minimum temporal granularity of operation, called slots [1], at runtime. Offline, a schedule table is created which assigns parts of task executions to these slots. Slots can be seen as units of resource reservation, i.e., reserving chunks of CPU time to the assigned tasks. In this paper, we propose to extend these reservations to several resources. We propose a two-part slotlevel based resource-control method using a TT scheduling approach that enables the use of multicore platforms for executing hard real-time tasks in TT systems. We propose a runtime mechanism consisting of two servers running on each core - processing time server and memory access server each having a fixed server period equal to the slot length. We guarantee the offline computed bound on variability in execution time of each task by enforcing offline computed slotlevel server budget reservations on each core, thereby limiting

<sup>&</sup>lt;sup>1</sup>By variability in execution time of a task, we mean the variability introduced beyond the traditional single-core WCET due to the inter-core interferences in a multicore system.

inter-core interferences from co-executing tasks, as well as, additional inter-core interferences introduced by the task under consideration. In the offline phase, we propose to generate schedule table containing mapping, scheduling and server budget reservations, that bounds the variability in execution time of each task due to inter-core interferences, such that all tasks meet their deadlines. The computation of the bound on variability in execution time of each task involves estimating maximum inter-core interferences from already scheduled co-executing tasks in each slot, as well as, limiting the slot-level inter-core interferences that may be introduced by the task at hand, at runtime.

Overall, our proposed method considers a real COTS multicore platform - Freescale P4080 - and accounts for the delay introduced by arbitration and contention in the on-chip network and the memory sub-system. Further, we did a preliminary bare-metal implementation of our proposed runtime mechanism on the P4080 platform. Moreover, our method adheres to the TT architecture model [1] preserving system-wide properties like slot-level determinism, clock synchronization, etc., enabling integration of COTS multicores in safety-critical systems using a TT approach.

#### II. SYSTEM MODEL, TASK MODEL, AND JOB MODEL

#### A. System Model

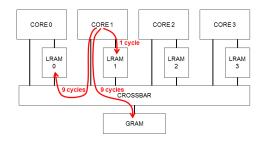

We consider an abstract multicore hardware architecture inspired by the readily available real COTS multicore system - Freescale QorIQ P4080 platform [8]. We focus only on the hardware resources essential for task scheduling on the P4080 platform. These are 8 e500mc cores, the memory sub-system, and the crossbar CoreNet on-chip network. Along similar lines, we assume that the abstract multicore hardware comprises only two types of hardware resources: N homogeneous processing cores (including private caches) from 1,...,n,...,N, and 1 shared resource consisting of a on-chip network with a memory sub-system. As this work is a first step, we only consider 1 memory controller in the memory sub-system, even though the P4080 platform has 2 memory controllers. Further, we assume that the hardware mechanisms like prefetchers, cache-coherency etc., that may implicitly introduce unaccounted inter-core interferences are disabled.

The inter-core interference latency, includes the time taken by a load/store request issued from a core to access the on-chip network and the memory sub-system, considering contentions. We consider the same latencies for our abstract multicore architecture as used in [2], [7]. The measurement-based approach as described in [9], using which these latencies are obtained, tries its best to create worst-case inter-core interference scenario, but is not guaranteed to do so, as the hardware model is not provided by Freescale. However, this is not a potential limitation of our proposed method in Section III as, when available, it will also work with intercore interference latencies obtained through static analysis.

As shown in Table I, the latency of inter-core interference varies with the number of active processing cores partly due to varying arbitration delay from shared hardware resources.

Each inter-core interference latency  $\delta_j$  depends on the j number of active cores. E.g., as shown in Table I, if (say) j=3 cores are active from time [t,t+1), we consider all inter-core interferences that occur during this time interval to have latency  $\delta_3$  (worst case) as listed in column 2 in Table I.

We consider a time-triggered (TT) scheduling approach and assume the timeline is divided into fixed equal length slices called slots [1]. A slot  $S_{t,n}$  represents a time interval [t, t+1), (where t is an integer multiple of slot length |S|) on core n. We also assume the system is preemptive at each slot boundary.

TABLE I: Inter-core interference latency and corresponding memory access server budget reservation for different number of active cores

| No. of       | Inter-core                           | Memory access server  |

|--------------|--------------------------------------|-----------------------|

| active cores | interference latency                 | budget reservation in |

| (j)          | $(\delta_j \text{ in clock cycles})$ | $1 ms (Acc_j)$        |

| 1            | 41                                   | 29385                 |

| 2            | 164                                  | 7346                  |

| 3            | 245                                  | 4917                  |

| 4            | 463                                  | 2602                  |

| 5            | 517                                  | 2330                  |

| 6            | 737                                  | 1634                  |

| 7            | 784                                  | 1536                  |

| 8            | 1007                                 | 1196                  |

|              |                                      |                       |

#### B. Task Model and Job Model

The set  $\Gamma$  represents V hard real-time periodic tasks with arbitrary deadlines. Each task  $\tau_i$  is characterized by the tuple  $\langle C_i^s, MA_i, T_i, D_i \rangle$ , where,  $C_i^s$  is the single core WCET excluding the time taken by memory accesses,  $MA_i$  is the maximum number of memory accesses to the shared resource,  $T_i$  is the period, and  $D_i$  is the relative deadline.  $C_i^s$  and  $MA_i$  are obtainable using a combination of static timing analysis tool like aiT and measurements [7]. Tasks may have precedence and communication constraints specified in graph  $\mathcal{G}$ .

In our proposed method (Section III), as we allow each instance of a task to have a different bound on variability in execution time, we convert the given task set to jobs, where each instance of a task is a job. The set  $\mathcal{J}$  represents all jobs W of all tasks in a task set  $\Gamma$  in time [0,H), where H is the hyperperiod of the task set  $\Gamma$ . Each job  $\tau_{i,k}$  is characterized by the tuple  $\langle C_{i,k}^s, MA_{i,k}, C_{i,k}^m, r_{i,k}, d_{i,k} \rangle$ .  $C_{i,k}^s$  and  $MA_{i,k}$  are same across all jobs of task  $\tau_i$ .  $C_{i,k}^m$  is the multicore execution time i.e. the bound on variability in execution time of job  $\tau_{i,k}$ , computed offline, considering possible runtime inter-core interferences.  $C_{i,k}^m$  may differ between different jobs of the same task  $\tau_i$ .  $r_{i,k}$  is the absolute release time and  $d_{i,k}$  is the absolute deadline of job  $J_{i,k}$ , which are computed based on the related parameters of the corresponding task.

#### III. PROPOSED SLOT-LEVEL BASED METHOD

In this section, we present our slot-level based method using a TT scheduling approach. The runtime mechanism is described in Section III-A and the offline phase in Section III-B

#### A. Runtime mechanism

We propose two server types - processing time server and memory access server, implemented using built-in hardware monitors. Each server type runs on each core and controls only one type of resource.

- 1) Processing time server: On each core n, a processing time server  $\tau_{sp_n}$  regulates the execution time in each server period based on the slot-level server budget reservations computed in the offline phase. During runtime, an executing job at time t consumes the server budget reservation  $Q_{sp_n,t}$  for the computation time on core n and stall time due to cache misses and/or memory accesses, resulting in a corresponding decrease of the server budget.

- 2) Memory access server: The memory access server  $\tau_{sm_n}$  regulates the total number of memory accesses allowed from each processing core n in each slot  $S_t$  based on slot-level offline computed server budget reservations  $Q_{sm_n,t}$ , thereby controlling the inter-core interferences. At runtime, an executing job uses the server budget reservation only for memory accesses, resulting in a decrease of server budget by 1 for each memory access issued.

- 3) Runtime behaviour: During runtime, each core-level scheduler, at the start of each slot, assigns a job to the respective core and sets the corresponding server budget reservations for each server based on the schedule table obtained in the offline phase. On each core, if the budget of any server reaches 0, the corresponding core-level scheduler suspends the executing job, irrespective of the remaining budget of the other server. Jointly, the two servers on each core guarantee that the server budget reservations provided for each slot in the offline schedule table hold at runtime, thereby enabling bounding of variability in execution time for each job in the offline phase considering possible runtime inter-core interferences.

- 4) Inter-relationship amongst two servers, slots, and intercore interference latencies: We consider the server period of each server is equal to the slot length |S|. For each processing time server instance, we allow only two mutually exclusive server budget reservation values: Either the budget reservation equals to zero which means an idle slot (no task is allowed to execute), or it equals to some fixed positive value X chosen by the system designer, such that  $X \leq |S|$ . For each memory access server instance, we allow N+1 mutually exclusive server budget reservation values. The N different budget reservation values directly associate with the different number of active cores. An additional budget reservation value of 0 relates to the idle slot, resulting in a total of N+1possible budget reservation values. Based on the description of each server, the relationship between the server budget reservations of the two servers and the inter-core interference latency  $\delta_i$ , for each active core n, is given by the formula  $Q_{sm_n,t} = \left\lfloor rac{Q_{sp_n,t}}{\delta_j(t)}

ight

floor, orall t,$  where j represents the number of active cores at time t. E.g., we consider a slot length |S| of 1ms and processing time server budget of 1ms. Table I then, shows the memory access server budget reservation values  $Acc_i$  (column 3) for j active processing cores (column 1).

- 5) Preliminary implementation: We did a preliminary baremetal implementation of our proposed runtime mechanism running on all cores of the P4080 COTS multicore platform. We implemented the processing time server using the multicore programmable interrupt controller (MPIC) timer

that enables slot-level synchronization amongst all cores. The MPIC timer also allows to set multiple processing cores as interrupt recipients, and provides each recipient core a unique interrupt copy [8]. We implemented the memory access server using a core-level hardware performance monitor that counts requests to the on-chip network [10]. We implemented our proposed suspension rules in interrupt service routines of the MPIC timer and hardware performance monitor on each core.

Though the idea to regulate memory accesses from each core using memory access server may seem similar to Mem-Guard [5], there are three key differences. Firstly, Mem-Guard considers minimum guaranteed memory bandwidth as constant, whereas our proposed method considers it as variable depending on the number of active cores (see Table I). Secondly, MemGuard assumes the memory server budget reservations for each core as given and constant across all server periods, whereas we do not make such an assumption. Thirdly, MemGuard does not consider if the given server budgets meet task deadlines, whereas our proposed method (introduced later in the Section III-B) gives offline guarantees.

#### B. Offline phase: Bounding variability in execution time

In the offline phase, we bound the variability in execution time of each job by computing server budget reservations for each slot, such that all tasks meet their deadlines. This limits, at runtime, the maximum inter-core interferences from coexecuting jobs as well as the additional inter-core interferences introduced by the job under consideration.

In the offline phase, let's consider at slot  $S_t$  on core n, the offline scheduler tries to schedule job  $\tau_{i,k}$ , such that the job  $\tau_{i,k}$  meets its deadline without affecting the already scheduled jobs. In order to compute the multicore execution time  $C^m_{i,k}$ , the offline scheduler first tries the simple case, where it considers a job  $\tau_{i,k}$  executes in each slot on some core n with constant memory access server budget reservation  $Acc_j$ . In this simple case, we compute the multicore execution time of job  $\tau_{i,k}$  using the formula  $C^m_{i,k} = \left[C^s_{i,k} + \frac{MA_{i,k}}{Acc_j}\right]$  based on some memory access server budget reservation  $Acc_j$  chosen by the offline scheduler (slot length S of 1ms).

However, it is possible that the offline scheduler is unable to find and reserve enough slots for the job  $\tau_{i,k}$  that fulfill chosen memory access server budget reservations  $Acc_j$  on core n until its deadline. In that case, we propose a different way to compute the multicore execution time.

Let's consider on core n, in the time [t,t+z+1), due to already scheduled jobs on remaining cores, the offline scheduler only finds slots with different memory access server budget reservations in time [t,t+z+1). Then (say) from slot  $S_{t+z+1}$ , the scheduler finds slots with constant memory access server budget reservations  $Acc_{jl}$ . In this case, we propose to first determine the minimum progress the job  $\tau_{i,k}$  can make in time [t,t+z+1) (both computation time and memory accesses). Then, we subtract the same while computing the remaining multicore execution time  $c^m_{i,k}(t+z+1)$  based on new budget reservation  $Acc_{jl}$  from time t+z+1 onwards. The offline scheduler then reserves the slots in time [t,t+z+1)

with the available server budget reservations, and from time t+z+1 to  $t+z+c_{i,k}^m(t+z+1)$  with  $Acc_{j}$ . If the job  $\tau_{i,k}$  still cannot meet its deadline, the offline scheduler will try to reschedule some already scheduled jobs, e.g., by backtracking.

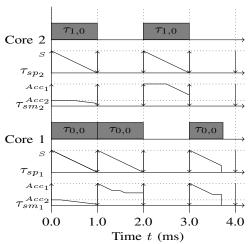

#### IV. EXAMPLE

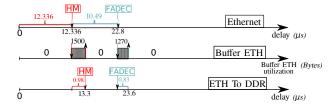

Figure 1 shows an example of our proposed method considering only 2 cores due to the space constraints. Each core n has two servers: processing time server  $\tau_{sp_n}$  and memory access server  $\tau_{sm_n}$ , with server period equal to the slot length |S| of 1ms. For each server, the dotted horizontal lines depict the possible server budget reservation values. During runtime, at the start of each slot, each core-level scheduler assigns a job to the respective core and sets the corresponding server budgets for each server, based on the offline schedule table.

At time t = 0, as both the cores are active, each corelevel scheduler sets the corresponding processing time server budget reservation to 1ms and memory access server budget reservation to  $Acc_2 = 7346$  accesses (based on Table I). At time t=1ms, only job  $\tau_{0,0}$  is active resulting in memory access server budget  $Q_{sm_1,1} = Acc_1 = 29385$  accesses (based on Table I) and processing time server budget of 1ms. In the time interval [1, 1.33)ms, the job  $\tau_{0,0}$  issues memory access as shown by corresponding decrease in memory access server budget. Then in the time interval [1.33, 2)ms, it does not perform any memory accesses as shown by memory access server budget being constant. Later, it again briefly issues memory accesses for the next  $100\mu s$ . In the time interval [1.6, 2)ms, since, only the processing time server budget decreases and not the memory access server budget, the job  $\tau_{0,0}$  only performs computations. At time t=3ms, the job  $\tau_{1,0}$ completes execution and the scheduler of core 2 discards the unused memory access server budget from the previous server instance  $\tau_{sm_2,2}$ . Further, at time t=3ms, as only job  $\tau_{0,0}$  is active, the memory access server budget  $Q_{sm_1,3}$  equals  $Acc_1$ . The job  $\tau_{0,0}$  issues memory accesses in the first half of the slot as shown by decrease in memory access server budget. Then, for the next  $200\mu s$ , it does not issue any memory accesses as the memory access server budget does not decrease and at time t = 3.7ms completes execution, resulting in discarding of unused server budgets by the core-level scheduler.

#### V. CONCLUSION AND FUTURE WORK

In this work, we presented an initial step towards enabling time-triggered (TT) scheduling on a real COTS multicore platform P4080. It takes into account inter-core interferences in the on-chip network and the memory sub-system. Our proposed method comprises a runtime mechanism and an offline phase. For the runtime mechanism, we proposed a processing time server and a memory access server for each core. Jointly, the two servers on each core, enforce slot-level offline computed server budget reservations, thereby limiting the maximum inter-core interferences introduced and experienced by each task considering different inter-core interference latencies. In the offline phase, we proposed a procedure for the offline scheduler to compute the bound on variability in execution

Fig. 1: Example of our proposed slot-level based method

time of each task while allowing different slot-level memory access server budget reservations. Overall, our proposed method facilitates integration of COTS multicore platforms in TT systems, while maintaining features of TT architecture like slot-level determinism, clock synchronization, etc.

We did a preliminary bare-metal implementation of our proposed runtime mechanism on a real COTS multicore platform P4080. In future work, we aim to provide safe bounds for the variability in execution time and will integrate the procedure in our existing offline scheduler to generate schedule tables containing mapping, schedule and server budget reservations.

#### ACKNOWLEDGMENT

The work was supported by ARTEMIS project 621429 EMC2. We thank the referees for several useful comments.

#### REFERENCES

- [1] H. Kopetz, Real-Time Systems: Design Principles for Distributed Embedded Applications, 2nd ed. Springer-Verlag, 2011.

- [2] J. Nowotsch, M. Paulitsch, D. Buhler, H. Theiling, S. Wegener, and M. Schmidt, "Multi-core interference-sensitive weet analysis leveraging runtime resource capacity enforcement," in *Real-Time Systems (ECRTS)*, 2014 26th Euromicro Conference on, July 2014, pp. 109–118.

- [3] CAST-32 Multi-core Processors. Certification Authorities Software Team, May 2014.

- [4] H. Yun, G. Yao, R. Pellizzoni, M. Caccamo, and L. Sha, "Memory access control in multiprocessor for real-time systems with mixed criticality," in *Real-Time Systems (ECRTS)*, 2012 24th Euromicro Conference on, July 2012, pp. 299–308.

- [5] —, "Memguard: Memory bandwidth reservation system for efficient performance isolation in multi-core platforms," in *Real-Time and Em*bedded Technology and Applications Symposium (RTAS), 2013 IEEE 19th, April 2013, pp. 55–64.

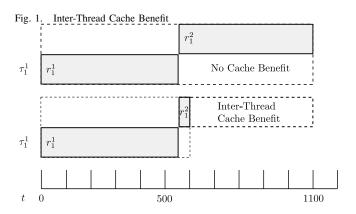

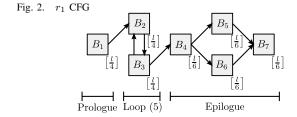

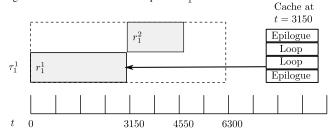

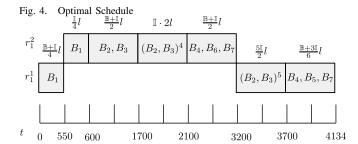

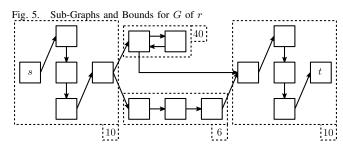

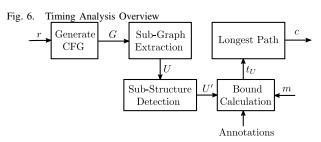

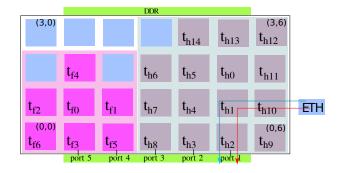

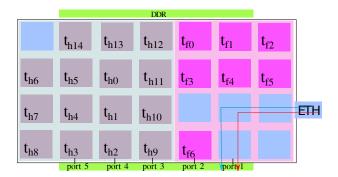

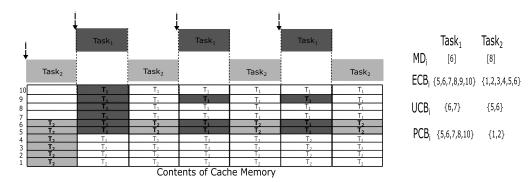

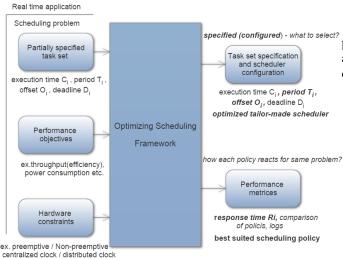

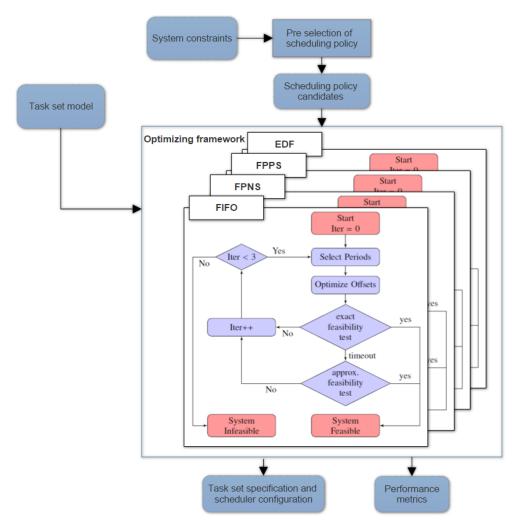

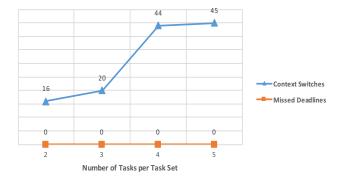

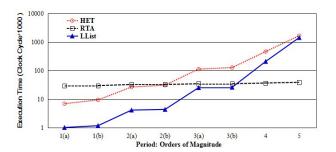

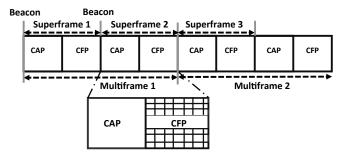

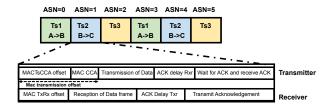

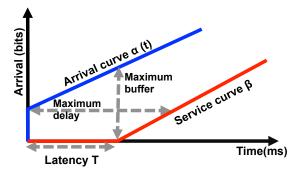

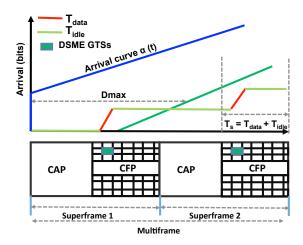

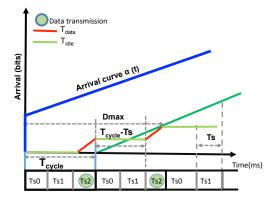

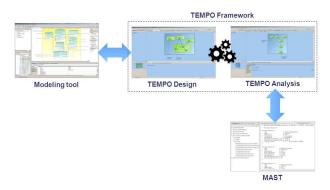

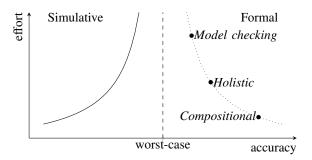

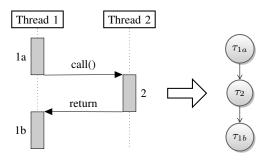

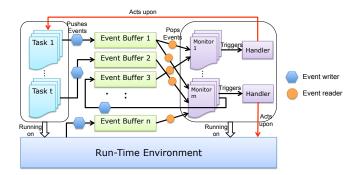

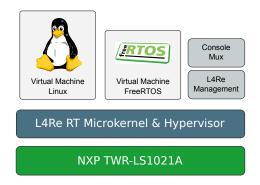

- [6] G. Yao, H. Yun, Z. P. Wu, R. Pellizzoni, M. Caccamo, and L. Sha, "Schedulability analysis for memory bandwidth regulated multicore realtime systems," *Computers, IEEE Transactions on*, vol. 65, no. 2, pp. 601–614, Feb 2016.