# Sliding Mode Control of Unified Power Quality Conditioner for 3 Phase 4 Wire Systems

Nelson Santos, J. A. Silva, João Santana

# ▶ To cite this version:

Nelson Santos, J. A. Silva, João Santana. Sliding Mode Control of Unified Power Quality Conditioner for 3 Phase 4 Wire Systems. 5th Doctoral Conference on Computing, Electrical and Industrial Systems (DoCEIS), Apr 2014, Costa de Caparica, Portugal. pp.443-450,  $10.1007/978-3-642-54734-8\_49$ . hal-01274807

# HAL Id: hal-01274807 https://inria.hal.science/hal-01274807

Submitted on 16 Feb 2016

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Sliding Mode Control of Unified Power Quality Conditioner for 3 Phase 4 Wire Systems

Nelson Santos<sup>1</sup>, J. Fernando Silva<sup>2</sup>, João Santana<sup>2</sup>

<sup>1</sup> Instituto Superior de Engenharia de Lisboa

R. Conselheiro Emídio Navarro, 1959-007 Lisboa, Portugal

nsantos@deea.isel.ipl.pt

<sup>2</sup> Instituto Superior Técnico, Instituto Superior Técnico, INESC-id, DEEC, AC Energia Av. Rovisco Pais, 1049-001 Lisboa, Portugal jsantana@ist.utl.pt, fernandos@alfa.ist.utl.pt

**Abstract.** This paper presents the sliding mode control (SMC) of unified power quality conditioners (UPQC) intended to compensate power quality issues in three-phase four-wires systems. The SMC UPQC can be applied in electrical grids or isolated grids to mitigate power quality problems at the consumer facilities and also to minimize issues for the grid supplier. The UPQC is configured as a shunt-series filter. The shunt Active Power Filter (APF) uses a three-phase rectifier with SMC to enforce sinusoidal mains currents. The series APF uses three single-phase H-bridge inverters and SMC to improve the voltage quality at the point of common coupling. SMC design, analysis and simulation results are presented and discussed.

**Keywords:** Unified Power Quality Conditioner; Active Power Filter; Sliding Mode Control.

#### 1 Introduction

In recent years, economic and environmental reasons entail the best possible use of energy resources. Recent technological developments enabled better usage of energy resources, mainly alternative energies [1]. However, due to the usually relatively low duty-cycle and randomness of these energies, their interconnection to the electrical grid might require the use of power electronics systems, and power quality mitigating devices, such APF, to increasing power quality [2], according to the standards recommended maximum power quality disturbances (IEEE 519, IEC 50160).

Most common power quality issues arise in the distribution grids, including voltage variations, harmonics, voltage sags and swells, voltage unbalances, harmonic currents, high reactive power burden and excessive neutral wire current. APFs can solve voltage and current waveform issues, reducing harmonics in a wide frequency band without resonance problems [3].

#### 2 Contribution to Collective Awareness Systems

This paper proposes a UPQC system with the ability to increase the quality of distribution of electrical power to achieve better efficiency. It proposes a contribution towards the sustainability of global systems considering the economic aspect and the environmental, reaching an important advance in the sustainable growth systems while benefiting from future collective awareness system to take informed decisions, making effective the involvement of the customer and sustainable energy systems.

## 3 UPQC Topology

Conventional UPQC have two basic configurations [3]. The most common is the series-shunt which injects the voltage compensation at the source side and the current compensation at the load side. This configuration has the advantage of the current flowing through the series transformer containing only the fundamental frequency. The shunt-series UPQC injects currents at the source side and compensates voltage at the load side. This configuration has the advantage of avoiding the interference between the shunt inverter and the passive filters, caused by the high frequency switching of the UPQC [3].

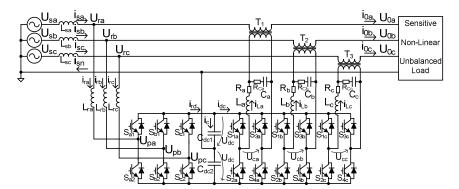

This paper presents the study of a shunt-series configuration provided with a passive LC filter on the series side as depicted in Fig. 1.

Fig. 1. Shunt-Series UPQC.

To compensate the neutral current a split capacitor topology ( $C_{dc1}$ ,  $C_{dc2}$ ), with the midpoint connected to the neutral wire, enables return currents through the capacitors, being  $i_{sa}+i_{sb}+i_{sc}=i_{sn}$ . The return of the neutral current through the DC bus capacitors unbalances the voltage of the two capacitors and decreases the dynamic response of the shunt APF. To minimize this problem, an extra control system to equalize the voltage on the two capacitors is usually included [3], even for small neutral currents, with zero average values, flowing into the source due the high switching harmonics.

#### 3 Control

#### 3.1 Shunt APF

The shunt APF must enforce sinusoidal  $i_{sa}$ ,  $i_{sb}$  and  $i_{sc}$  currents in the mains source, [4]. Additionally, the shunt APF must stabilize the DC bus voltage [3].

**Sliding Mode Internal Current Control.** The shunt APF injects the necessary currents to cancel unwanted harmonics produced by non-linear and unbalanced loads. A SMC technique is used to control the mains current. Considered one generic single phase k of the corresponding source, as represented in Fig. 1. Assuming ideal switches and ideal components, the dynamics of the  $i_{sk}$  current  $k \in \{a, b, c\}$  can be described considering that the voltage  $U_{pk}$ , relative to the neutral voltage, is dependent on the switches states of the shunt inverter semiconductors, as in (1).

$$U_{pk} = \delta(t) U_{dc} = \begin{cases} U_{pk} = U_{dc} & \text{for } \delta(t) = +1 \ (S_{k1} \ ON \ and \ S_{k2} \ OFF) \\ U_{pk} = -U_{dc} & \text{for } \delta(t) = -1 \ (S_{k1} \ OFF \ and \ S_{k2} \ ON) \end{cases}$$

(1)

The first time derivative of the  $i_{rk}$  current is given as  $\frac{di_{rk}}{dt} = \frac{U_{rk} - \delta(t)U_{dc}}{L_{rk}}$  considering that  $i_{sk} = i_{rk} + i_{0k}$ , and  $\frac{di_{sk}}{dt} = \frac{di_{rk}}{dt} + \frac{di_{0k}}{dt}$ , then, the phase canonical model of current  $i_{sk}$  is written as (2).

$$\frac{di_{sk}}{dt} = \frac{U_{rk}}{L_{rk}} - \frac{\delta(t)U_{dc}}{L_{rk}} + \frac{di_{0k}}{dt}$$

(2)

The first time derivative of  $i_{sk}$  contains the control action  $\delta(t)U_{dc}$ , thus the strong relative degree [5] of  $i_{sk}$  is 1, and a suitable sliding surface can be obtained as a linear combination of the control error  $e_{i_{sk}} = i_{sk}^{ref} - i_{sk} r$ , where  $i_{sk}^{ref}$  is the reference value to be tracked by the  $i_{sk}$  current. Considering a positive gain  $K_p$ , used to limit the semiconductors switching frequency, a suitable sliding surface  $S(ei_{sk}, t)$  [5] is:

$$S(e_{i_{sk}}, t) = K_p e_{i_{sk}} = K_p (i_{sk}^{ref} - i_{sk}) = 0$$

(3)

The switching strategy is obtained applying the sliding mode stability condition  $S(e_{i_{sk}}, t) \dot{S}(e_{i_{sk}}, t) < 0$  [6], with  $\dot{S}(e_{i_{sk}}, t) = K_p \left( \frac{d \iota_{sk}^{ref}}{dt} - \frac{U_{rk}}{L_{rk}} + \frac{\delta(t) U_{dc}}{L_{rk}} - \frac{d \iota_{0k}}{dt} \right)$ . As  $S(e_{i_{sk}}, t)$  is proportional to  $e_{i_{sk}}$ , the stability condition is written as:

$$\begin{cases} \text{if } e_{i_{sk}} > 0, & \text{then } \frac{de_{i_{sk}}}{dt} < 0 \ \Rightarrow \ \frac{di_{sk}^{ref}}{dt} - \frac{U_{rk}}{L_{rk}} + \frac{\delta(t)U_{dc}}{L_{rk}} - \frac{di_{0k}}{dt} < 0 \\ \text{if } e_{i_{sk}} < 0, & \text{then } \frac{de_{i_{sk}}}{dt} > 0 \ \Rightarrow \ \frac{di_{sk}^{ref}}{dt} - \frac{U_{rk}}{L_{rk}} + \frac{\delta(t)U_{dc}}{L_{rk}} - \frac{di_{0k}}{dt} > 0 \end{cases}$$

$$(4)$$

From (4), the sliding mode reaching condition can be obtained as  $\frac{\delta(t)U_{dc}}{L_{rk}} >$  MAX $\left(-\frac{di_{sk}^{ref}}{dt} + \frac{U_{rk}}{L_{rk}} + \frac{di_{0k}}{dt}\right)$ . Supposing that  $U_{dc}$  is high enough to satisfy this reaching condition and if  $e_{i_{sk}} > 0$  then  $\frac{de_{i_{sk}}}{dt} < 0$  the control action is  $\delta(t) = -1$  or if  $e_{i_{sk}} < 0$

444

then  $\frac{de_{i_{sk}}}{dt} > 0$  the control action is  $\delta(t) = 1$ . To define a finite switching frequency, the  $i_{sk}$  current must have a non-zero ripple content  $\Delta i_{sk}$ . The switching law is then:

$$\delta(t) = \begin{cases} -1 \operatorname{for} S(e_{i_{sk}}, t) > +\Delta i_{sk}/2\\ 1 \operatorname{for} S(e_{i_{sk}}, t) < -\Delta i_{sk}/2 \end{cases}$$

(5)

The sliding surface (3) and the non-linear switching law (5) do not depend on any load parameter, but only on the measured  $i_{sk}$  current error  $e_{i_{sk}}$ . To generate the sinusoidal and balanced  $i_{sk}^{ref}$  current references in the abc frame the inverse Park Transform (dq0 to abc), is used where  $i_d$ ,  $i_q$  and  $i_0$  are the direct, quadrature and zero sequence component of the current reference. The  $i_{sk}^{ref}$  current references in dq0 ( $i_d$ ,  $i_q$  and  $i_0$ ) will be obtained using a slow enough linear controller to minimize current total harmonic distortion (THD). The response time should be tailored to avoid DC bus voltage dropouts in the case where fast increments of load currents are required, which can affect the global dynamic of series APF.

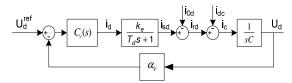

Linear External DC Bus Voltage Control. The external loop to regulate the voltage in the DC bus capacitors uses a PI controller,  $C_{v(s)} = \frac{1+sT_z}{sT_p}$ , designed to present small load sensitivity. The PI output is the reference for the current  $i_d$  component of Park Transform [7], while the  $i_q$  and  $i_0$  components of Park Transform are set to zero to have near unity power factor  $(v_q = 0)$  and to balance the three phases. The previously designed sliding mode internal current control closed loop behavior is modelled by a first order system represented as  $\frac{i_r k}{i_s^{ref}} = \frac{k_e}{T_d s+1}$  where  $k_e = \frac{U_{sd}}{2U_{dc}}$  and  $T_d$  is estimated knowing that line currents should be sinusoidal to avoid line current distortion. The PI parameters  $T_z$  and  $T_p$  of the voltage controller  $C_v(s)$  are calculated using the Symmetrical Optimum technique, [8]. Assuming  $U_d = 2U_{dc}$  and  $C = C_{dc1}/2 = C_{dc2}/2$ , the differential equation of the DC bus voltage is  $\frac{dU_d}{dt} = \frac{i_r d - i_d c}{c}$ . Applying superposition with zero disturbances and supposing  $\alpha_v = 1$  (sensor voltage gain), the closed-loop transfer function of the DC bus voltage control has a third order polynomial denominator,  $\frac{U_d}{v_d} = \frac{1+sT_z}{k_o} + s^2 \frac{1+sT_z}{k_o} + s^2 \frac{1-sT_z}{k_o} + s^2 \frac{1-sT_z$

Fig. 2. DC bus voltage control.

Applying Symmetrical Optimum criteria  $b_k^2 = 2b_{k-1}b_{k+1}$ , to ensure a low enough sensitivity to the UPQC disturbances. The value  $T_d$ =4ms was used to obtain the  $T_z$  and  $T_p$ , so that line currents are almost sinusoidal and DC bus voltage response is fast

enough to avoid affecting the series APF performance [5]. The PI parameters are  $T_z=4T_d$  and  $T_p=\frac{8T_d^2k_e}{C}$ .

#### 3.2 Series APF

To compensate the voltage distortion, the three series transformer primaries are driven using three single-phase H-bridge inverters (Fig. 1) controlled using SMC. Considering the per-phase equivalent of the series APF, with  $k \in \{a, b, c\}$ , where the  $C_k$  is the filter capacitor and the load is reduced to the transformer primary.

The  $U_{ck}$  output voltage depends on the switches states  $S_{1k}$ ,  $S_{2k}$ ,  $S_{3k}$  and  $S_{4k}$ .

$$U_{ck} = \gamma_c(t)U_d = \begin{cases} U_{ck} = U_d & \text{for } \gamma_c(t) = +1 \quad (S_{1k}, S_{4k} \, ON) \\ U_{ck} = 0 & \text{for } \gamma_c(t) = 0 \, (S_{1k}, S_{3k} \, ON \, or \, S_{2k}, S_{4k} \, ON) \\ U_{ck} = -U_d \, \text{for } \gamma_c(t) = - \, (S_{2k}, S_{3k} \, ON) \end{cases}$$

(6)

Assuming ideal components, the dynamic model with state variables  $u_{0k}$  and  $i_{Lk}$  is written as (7), were  $i_{0k}$  is the load current:

$$\frac{d}{dt}\begin{bmatrix} u_{0k} \\ i_{lk} \end{bmatrix} = \begin{bmatrix} 0 & 1/C_k \\ -1/L_k & -R_k/L_k \end{bmatrix} \begin{bmatrix} u_{0k} \\ i_{lk} \end{bmatrix} + \begin{bmatrix} -1/C_k & 0 \\ 0 & 1/L_k \end{bmatrix} \begin{bmatrix} i_{0k} \\ \delta_c(t)U_d \end{bmatrix} \tag{7}$$

The proposed of the series APF is compensate the voltage at the load side. According to [5], [6] and [9], to control the load voltage  $u_{0k}$  is necessary to obtain a equation which includes the dynamic of switching. The first order derivative of  $u_{0k}$  doesn't include the switch condition  $\delta_c(t)$ , for this reason we need to calculate the second order derivative for the  $u_{0k}$ . Thus, the strong relative degree of  $u_{0k}$  is 2 written as  $\frac{d^2u_{0k}}{dt^2} = -\frac{1}{C_k}\frac{di_{0k}}{dt} - \frac{u_{0k}}{L_kC_k} - \frac{R_k I_{Lk}}{L_kC_k} + \frac{\delta_c(t)U_d}{L_kC_k}$ .

The robust sliding surface (8) is a linear combination of the control error  $e_{u_{0k}}$  and its derivative,  $e_{u_{0k}}=u_{0k}^{ref}-u_{0k}$ , where  $u_{0k}^{ref}$  is the voltage reference to be tracked and  $u_{0k}$  the voltage feedback.

$$S(e_{u_{0k}}, t) = k_1 e_{u_{0k}} + k_2 \frac{de_{u_{0k}}}{dt} = 0$$

(8)

The system response depends on the coefficients  $k_1$  and  $k_2$  which must be selected to ensure stability and fast response for operating conditions. Considering  $\beta = k_2/k_1$  the sliding surface is written as:

$$S(e_{u_{0k}}, t) = \frac{C_k}{\beta} (u_{0k}^{ref} - u_{0k}) + C_k \frac{du_{0k}^{ref}}{dt} + i_{0k} - i_{Lk} = 0$$

(9)

The switching strategy is obtained applying the sliding mode stability condition  $S(e_{u_{0k}},t) \dot{S}(e_{u_{0k}},t) < 0$ , with  $\dot{S}(e_{u_{0k}},t) = \frac{i_{Lk}}{C_k} - \frac{i_{0k}}{C_k} + \beta \left(\frac{1}{C_k} \frac{di_{0k}}{dt} + \frac{u_{0k}}{L_k C_k} + \frac{R_k i_{Lk}}{L_k C_k} - \frac{\delta_c(t) U_d}{L_k C_k}\right)$ . As  $S(e_{u_{0k}},t)$  is proportional to  $e_{u_{0k}}$ , the stability condition is written as:

$$\begin{cases} \text{if } e_{u_{0k}} > 0, & \text{then } \frac{de_{u_{0k}}}{dt} < 0 \Rightarrow \frac{i_{Lk}}{C_k} - \frac{i_{0k}}{C_k} + \beta \left( \frac{1}{C_k} \frac{di_{0k}}{dt} + \frac{u_{0k}}{L_k C_k} + \frac{R_k i_{Lk}}{L_k C_k} - \frac{\delta_c(t) U_d}{L_k C_k} \right) < 0 \\ \text{if } e_{u_{0k}} < 0, & \text{then } \frac{de_{u_{0k}}}{dt} > 0 \Rightarrow \frac{i_{Lk}}{C_k} - \frac{i_{0k}}{C_k} + \beta \left( \frac{1}{C_k} \frac{di_{0k}}{dt} + \frac{u_{0k}}{L_k C_k} + \frac{R_k i_{Lk}}{L_k C_k} - \frac{\delta_c(t) U_d}{L_k C_k} \right) > 0 \end{cases}$$

From (10), the sliding mode reaching condition is  $\beta \frac{\delta_c(t) U_d}{L_k C_k} > \text{MAX} \left( \frac{i_{Lk}}{C_k} - \frac{i_{0k}}{C_k} + \beta \left( \frac{1}{C_k} \frac{di_{0k}}{dt} + \frac{u_{0k}}{L_k C_k} + \frac{R_k i_{Lk}}{L_k C_k} \right) \right)$ . Supposing that  $U_d$  is high enough to satisfy this reaching condition and using a hysteresis comparator, with  $\Delta u_{0k}$  as hysteresis, to avoid infinite switching frequency, the switching law is (11), being  $\delta_c(t) \in \{-1; 0; 1\}$  to obtain three possible  $U_{ck}$  levels.

$$\begin{cases} \text{if } e_{u_{0k}} > \frac{\Delta u_{0k}}{2}, & \text{then } \frac{de_{u_{0k}}}{dt} < 0 \Rightarrow \delta_c(t) = 1 \\ \text{if } \frac{-\Delta u_{0k}}{2} < eu_{0k} < \frac{\Delta u_{0k}}{2}, & \text{then } \delta_c(t) = 0 \\ \text{if } e_{u_{0k}} < \frac{-\Delta u_{0k}}{2}, & \text{then } \frac{de_{u_{0k}}}{dt} > 0 \Rightarrow \delta_c(t) = -1 \end{cases}$$

$$(11)$$

This technique samples  $u_0$ ,  $i_0$  and  $i_L$ , but the closed loop dynamics does not depend on load parameters. Fast response with zero steady-state errors are also attained [10].

#### 4 Simulation

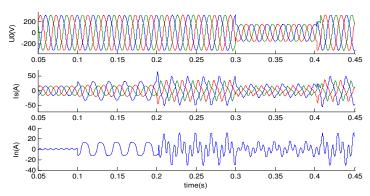

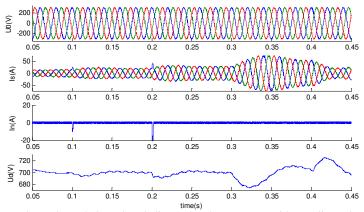

The UPQC was simulated using Matlab/Simulink considering non-ideal mains voltage with 5% THD. Several loads, described in the Appendix, were tested.

To evaluate the UPQC response with wide operating conditions, different loads and conditions were tested successively. The test begins with a balanced R load. Then, an unbalanced RL load is switched on to add to the existing balanced R load. In a third step it is added a non linear load, made by three single-phase bridge rectifiers, with upstream inductance L and parallel RC type circuit downstream of the bridge. In the fourth step a voltage sag in the main source appears, being cleared in the fifth step.

The first simulation (Fig. 5) is performed without any compensation. High neutral current exists due to the switching on of unbalanced and non-linear loads. The load voltage has a THD of 5.4%. The THD of currents reach a maximum of 25,1% in the worse case.

Using the compensating UPQC, the delivered voltage (Fig. 6) has a maximum THD of 0.6%, and currents drops to a maximum THD of 2.37%. The UPQC clearly improves the quality power to the main source (current) and to the load side (voltage). The neutral current is mostly zero throughout the simulation (except for switching harmonics and switch on transients).

Fig. 5. Results under unbalanced and distorted voltage source with non-linear loads without compensation.

Fig. 6. Results under unbalanced and distorted voltage source with non-linear loads with compensation.

### 5 Conclusion

This study demonstrates the sliding mode control of UPQC to improve power quality on three-phase four-wire systems. The UPQC can mitigate the harmonic content of voltage at the load side (88% reduction), and the harmonic current at the source side (90% reduction), while virtually eliminating the neutral current and improving the power factor. The measured values of the harmonic distortion of current source and the voltage delivered to the load were well within the recommended values according to standards IEEE-519 or IEC61000.

**Acknowledgments.** This work supported by Portuguese national funds through FCT – Fundação para a Ciência e a Tecnologia, under project PEst-OE/EEI/LA0021/2013.

### **Appendix**

The UPQC parameters are presented in Tab. 1.

Table 1. System Parameters

| Parameter | Value               | Parameter | Value       | Parameter                  | Value       | Parameter                     | Value  |

|-----------|---------------------|-----------|-------------|----------------------------|-------------|-------------------------------|--------|

| $U_{sk}$  | $230V_{ef}$         | $L_r$     | 1mH         | 1°st - R <sub>abc</sub>    | 20Ω         | $3^{\circ}$ st - $L_{NL}$     | 8.4mH  |

| $R_s$     | $10 \text{m}\Omega$ | $C_k$     | 112μF       | $2^{\circ}$ st - $L_{abc}$ | 5mH         | $3^{\circ}$ st - $C_{NL}$     | 1000μF |

| $L_s$     | 0.1mH               | $L_k$     | 0,9mH       | $2^{\circ}$ st – $R_{0a}$  | $R_{abc}$   | 3°st - <i>R</i> <sub>NL</sub> | 50Ω    |

| $U_d$     | 700V                | $R_{Ck}$  | 15Ω         | $2^{\circ}$ st – $R_{0b}$  | $50R_{abc}$ | 4°st - R <sub>sag</sub>       | $R_s$  |

| $C_{dc}$  | 5mF                 | $U_{ref}$ | $230V_{ef}$ | $2^{\circ}$ st - $R_{0c}$  | $5R_{abc}$  | $4^{\circ}$ st - $L_{sag}$    | $L_s$  |

#### References

- Farias, M.F.; Battaiotto, P.E.; Cendoya, M.G., "Wind Farm to Weak-Grid Connection using UPQC custom power device", *Industrial Technology (ICIT)*, *IEEE International Conference on*, vol., no., pp.1745, 1750, March 2010

- C. Babu and S. S. Dash, "Design of Unified Power Quality conditioner (UPQC) to improve the Power Quality Problems by Using P-Q Theory", *International Conference on Computer Communication and Informatics*, 2012

- V. Khadkikar, "Enhancing Electric Power Quality Using UPQC: A Comprehensive Overview", Power Electronics, IEEE Transactions on, vol. 27, no. 5, pp. 2284–2297, 2012

- Hirve S., Chatterjee K., Fernandes B. G., Imayavaramban M., and Dwari S., "PLL-Less Active Power Filter Based on One-Cycle Control for Compensating Unbalanced Loads in Three-Phase Four-Wire System", IEEE Trans. Power Delivery, Vol.22, no.4, pp. 2457-2465, Oct. 2007

- 5. J. F. Silva, S. F. Pinto, "Advanced Control of Switching Power Converters", in Muhammad Rashid et al, editors: Power Electronics Handbook 3ed, Vol Chennai: Butterworth Heinemann, chapter 36, pp. 1037-1114, 2011

- J. F. Silva, "PWM Audio Power Amplifiers: Sigma Delta Versus Sliding Mode Control", Proc. IEEE/ICECS'98 (ISBN 0-7803-5008-1), vol. 1, pp. 359-362, Lisboa, Portugal, Set., 1998

- X. B. X. Bin, D. K. D. Ke, and K. Y. K. Yong, "DC voltage control for the three-phase four-wire Shunt split-capacitor Active Power Filter", *IEEE International Electric Machines* and Drives Conference, pp. 1669–1673, May 2009

- C. Bajracharya, M. Molinas, M. Ieee, J. A. Suul, T. M. Undeland, and F. IEEE, "Understanding of tuning techniques of converter controllers for VSC-HVDC", Nordic Workshop on Power and Industrial Electronics, June 2008

- J. F. Silva, N. Rodrigues, J. Costa, "Space Vector Alpha-Beta Sliding Mode Current Controllers for Three-Phase Multilevel Inverters", IEEE Proc. PESC 2000, CD ROM ISBN 0-7803-5695-0, Galway, Ireland, June, 2000.

- J. F. Martins, A. J. Pires, J. Fernando Silva, A Novel and Simple Current Controller for Three-Phase PWM Power Inverters, IEEE Trans. on Industrial Electronics, vol. 45, no. 5, pp 802-805, 1998.