Towards Modeling and Simulation of Exascale Computing Platforms

Luka Stanisic

Supervised by: A.Legrand, B.Videau and J.F.Méhaut Laboratoire d'Informatique de Grenoble MESCAL and NANOSIM teams

June 21, 2012

ELE NOR

▶ ∢ ≣

#### Introduction

- Future super-computer platforms will be facing big challenges due to the enormous power consumption

- This internship was part of two research projects:

- Mont-Blanc (European): Developing scalable and power efficient HPC platform based on low-power ARM processors

- SONGS (ANR): Designing unified and open simulation framework for performance evaluation of next generation systems

- Adequate models are required

- **Goal**: Investigate is it possible to model CPU behavior at coarse grain, especially **ARM** processors

< □ > < 同 > < 三 > < 三 > < 三 > < □ > < □ > < ○ </p>

#### Simulation vs. alternative approach

Simulation (cycle-accurate simulation) and emulation:

- Often too slow

- Questionable accuracy

三日 のへの

(3)

#### Simulation vs. alternative approach

Simulation (cycle-accurate simulation) and emulation:

- Often too slow

- Questionable accuracy

We need *coarse-grain* models:

- Lots of existing projects: LAPSE, MPI-SIM, BigSIM, MPI-NetSim, MicroGrid, **PMAC**, ...

- Memory is the bottleneck of most HPC applications

- Starting point of this work were 2 articles from Allan Snavely and his team (PMAC) that seemed very promising:

- "A Framework for Application Performance Modeling and Prediction". A.Snavely, L.Carrington, N.Wolter, J.Labarta, R.Badia, A.Purkayastah, in *SuperComputing* 2002

- A Genetic Algorithms Approach to Modeling the Performance of Memorybound Computations". M. Tikir, L. Carrington, E. Strohmaier, A. Snavely in *SuperComputing* 2007

# Framework for Application Performance Modeling and Prediction

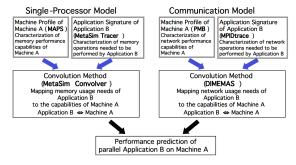

Authors propose a macroscopic approach:

Trying to characterize the code as a whole with parameters that can later be related to platform characteristics in order to evaluate performances

# Framework for Application Performance Modeling and Prediction

Authors propose a macroscopic approach:

Trying to characterize the code as a whole with parameters that can later be related to platform characteristics in order to evaluate performances

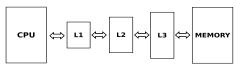

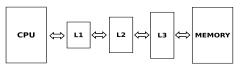

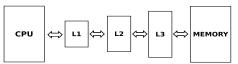

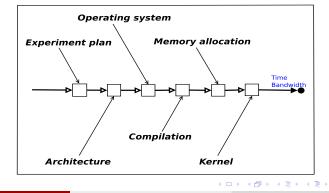

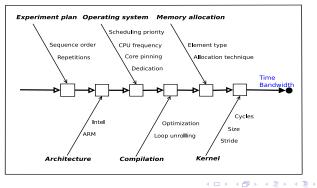

#### MultiMAPS(size,stride,nloops)

MultiMAPS(size,stride,nloops)

#### MultiMAPS(size,stride,nloops)

<ロト < 母 > < 臣 > < 臣 > 三日 の Q @

#### MultiMAPS(size,stride,nloops)

<ロト < 母 > < 臣 > < 臣 > 三日 の Q @

#### MultiMAPS(size,stride,nloops)

< □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □

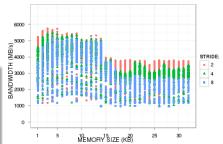

#### MultiMAPS(size,stride,nloops)

Our first experiments:

#### Methodology

- Problem with the related work is that it is not very well documented, it is not suited for NUMA, multicore architectures and experiments are not reproducible

- We wanted to do the measurements in a clean, coherent and systematic way

#### Methodology

- Problem with the related work is that it is not very well documented, it is not suited for NUMA, multicore architectures and experiments are not reproducible

- We wanted to do the measurements in a clean, coherent and systematic way

EL SQA

#### Outline

- 2 Memory Allocation Parameters

- Optimization Parameters

- Operating System Parameters

EL SOCO

A B K A B K

#### Outline

- 2) Memory Allocation Parameters

- 3 Optimization Parameters

- Operating System Parameters

- 5 Conclusion

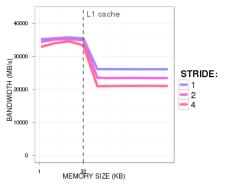

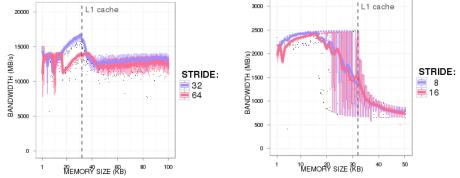

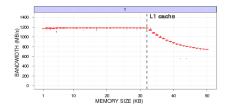

# Influence of Stride Parameter

- Comparing with the results from MultiMAPS:

- Clear plateaus

- Sharp drop when getting out of the L1 cache size

- Performance is lower for larger strides

# Intel Core i7 Sandy Bridge processor: Few max values

June 21, 2012 9 / 22

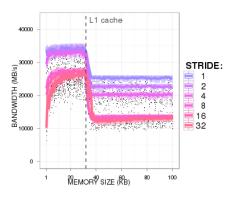

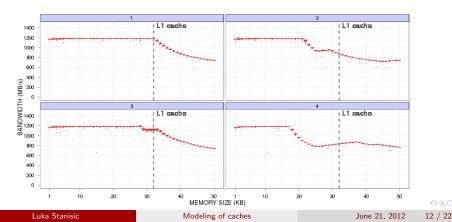

# Influence of Stride Parameter

- MultiMAPS:

- Clear plateaus

- Sharp drop when getting out of the L1 cache size

- Operation of the second sec strides

- Oifferent bandwidths for strides 8, 16, 32 inside L1 cache size

- Operation Performance drop for higher memory size values stop after stride 8

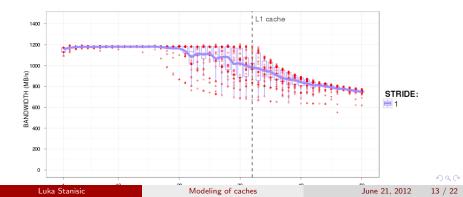

#### • Comparing with the results from Intel Core i7 Sandy Bridge processor: **Randomization** + **Boxplots**

June 21, 2012 9 / 22

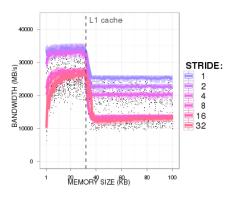

# Influence of Stride Parameter

- MultiMAPS:

- Clear plateaus

- 2 Sharp drop when getting out of the L1 cache size

- Operation of the second sec strides

- Oifferent bandwidths for strides 8, 16, 32 inside L1 cache size

- Operation Performance drop for higher memory size values stop after stride 8

- This is general behavior, but with many exceptions

#### • Comparing with the results from Intel Core i7 Sandy Bridge processor: **Randomization** + **Boxplots**

## **Unexpected Behavior**

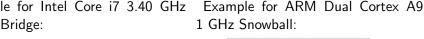

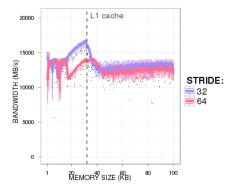

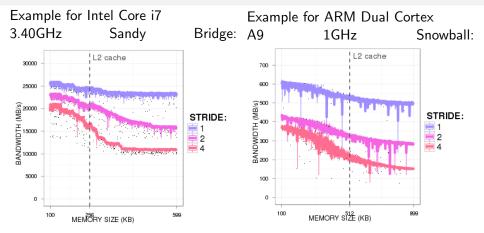

# Example for Intel Core i7 3.40 GHz Sandy Bridge:

• Irregular behavior inside L1 cache size!

Luka Stanisic

June 21, 2012 10 / 22

# Kerne

## **Unexpected Behavior**

Example for Intel Core i7 3.40 GHz Sandy Bridge:

Irregular behavior inside L1 cache size!

Luka Stanisic

June 21, 2012 10 / 22

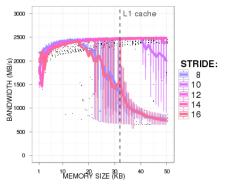

# **Unexpected Behavior**

Example for Intel Core i7 3.40 GHz Sandy Bridge:

Example for ARM Dual Cortex A9 1 GHz Snowball:

- Irregular behavior inside L1 cache size!

- Strides 10, 12, 14 have better performance than Stride 8 ?!?

Luka Stanisic

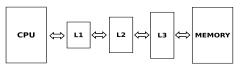

Modeling of caches

June 21, 2012 10 / 22

#### Outline

#### 2 Memory Allocation Parameters

Optimization Parameters

Operating System Parameters

#### 5 Conclusion

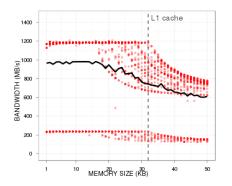

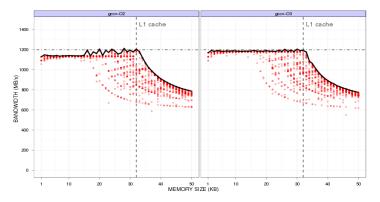

## Reproducibility Issue on ARM

- Same input parameters, consecutive experiments

- 42 repetitions per each memory size, NO NOISE!

- Results from ARM Dual Cortex A9 1GHz (Snowball):

# Reproducibility Issue on ARM

- Same input parameters, consecutive experiments

- 42 repetitions per each memory size, NO NOISE!

- Results from ARM Dual Cortex A9 1GHz (Snowball):

# Influence of Allocation Strategy on ARM

Different memory allocation technique:

Performance depend on actual physical address:

#### Outline

2 Memory Allocation Parameters

#### Optimization Parameters

Operating System Parameters

#### Conclusion

EL SOCO

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

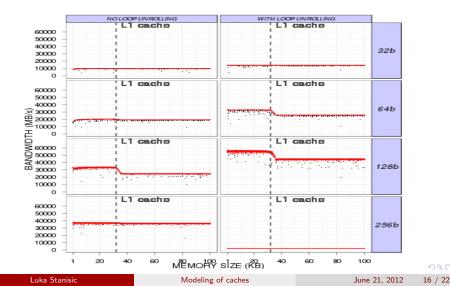

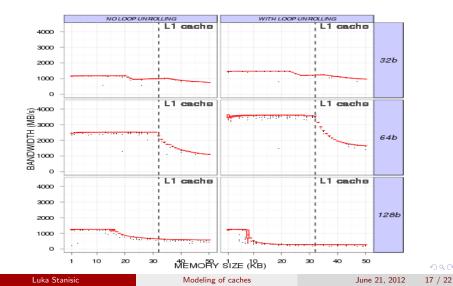

# Influence of Code Optimizations

#### Element type

Using *long long int* which is 64b instead of regular *int* 32b Vectorized instructions:

- On Intel: 128b SSE and 256b AVX

- On ARM: 128b NEON

#### Loop unrolling

```

Standard execution:

for(j=0;j<buffersize;j+=STRIDE)

{

sum+=buffer[j];

}

```

With loop unrolling: for(j=0;j<buffersize;j+=STRIDE\*8) { sum+=buffer[j]; ... sum+=buffer[j+7\*STRIDE]; }

# Results from Intel Sandy Bridge:

# Results from ARM Snowball:

#### Outline

- 2 Memory Allocation Parameters

- 3 Optimization Parameters

- Operating System Parameters

#### Conclusion

ELE NOR

★ 3 > < 3</p>

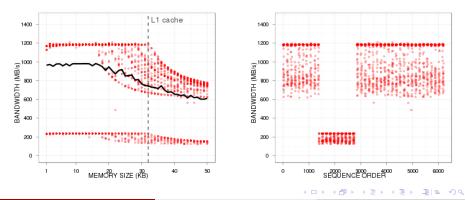

# Influence of OS Scheduling Policy on ARM

- Default priority-results shown on previous slides

- Nice priority-same behavior as default priority

- 8 Real-time priority-distinctive output

# Influence of OS Scheduling Policy on ARM

- Default priority-results shown on previous slides

- Ø Nice priority-same behavior as default priority

- Real-time priority-distinctive output

- Demonstration of 2 modes of execution for real-time priority:

# Influence of OS Scheduling Policy on ARM

- Default priority-results shown on previous slides

- Ø Nice priority-same behavior as default priority

- 8 Real-time priority-distinctive output

- Demonstration of 2 modes of execution for real-time priority:

#### Outline

Kernel Parameters

- 2 Memory Allocation Parameters

- 3 Optimization Parameters

- Operating System Parameters

ELE DOG

・ロト ・聞ト ・ヨト・

#### Conclusion

- This research provides insights on the possible use of ARM processors in HPC

- Predicting memory behavior is harder than the literature suggests

- Many unexpected parameters have great influence

- ARM processors should have been simpler but they are not (e.g. physical address on ARM)

- Optimized versions are generally more regular and easier to model

- Finding the good factor combination is non trivial

- Open Science: organize so that anyone can check and easily reproduce!

#### Future work

- Investigate more elaborate kernels that put more pressure on CPU

- Multi-threaded version of kernel (share data): synchronization protocol overhead, hierarchy

- Different kernels on the same node and sharing cache hierarchy:

JI SOCO

#### Future work

- Investigate more elaborate kernels that put more pressure on CPU

- Multi-threaded version of kernel (share data): synchronization protocol overhead, hierarchy

- Different kernels on the same node and sharing cache hierarchy:

- Incorporate HPC network models, GPU models, ....

- Use these models with simulation tools (SimGrid) to predict performance of future computer platforms

- Try to use open-science/reproducible research techniques in the HPC field and advertise for it

◆□▶ ◆母▶ ◆ヨ▶ ◆ヨ▶ ヨヨ シタペ

#### Sweave + Beamer

```

Activities

Emacs

Tue 21:09

•

()

stanisic

en

emacs23@pawnee.imag.fr

File Edit Options Buffers Tools TeX Noweb Help

- 🥱 🕌 📫 📮 🖾 👩

\mathbb{X}

<slabel=firstplot.include=FALSE.cache=TRUE>>=

df1 <- read.table("data/Snow2Data0.dat")</pre>

df1[.2] <- df1[.2]/1024

names(dfl)<-c("STRIDE", "SIZE", "t1", "t2", "TIME", "BANDWIDTH", "MODE")

df1<-df1[1:(32*7*3).]

df1<-df1[df1$STRIDE<16 & df1$STRIDE>1.]

attach(df1)

png('pictures/Rplots/FirstMeasurement.png', width=450,height=300)

p <- ggplot(data = df1[1:286,], aes(SIZE, BANDWIDTH)) + aes(shape = factor(STRIDE)) +</pre>

geom point(aes(colour = factor(STRIDE)), size = 2) +

labs(shape = "STRIDE:", colour = "STRIDE:")

D <- D +

scale v continuous("BANDWIDTH (MB/s)",limits=c(0, max(BANDWIDTH) * 1.2)) +

scale _ continuous("MEMORY SIZE (KB)", breaks=c(1,5,10,15,20,25,30))

p < -p + theme bw()

D

garbage <- dev.off()</pre>

detach(df1)

k

СП

\begin{frame}[fragile,t]{Kernel from MultiMAPS}

\begin{columns}[t]

\column{.5\textwidth}

-U:**- Presentation.Rnw 25% L253 (LaTeX Noweb NWFL)----

\begin{center}

\null\vspace{-6cm}\null

Our first experiments:

\includegraphics[width=\linewidth]{pictures/Rplots/FirstMeasurement.png}

\end{center}

Luka Stanisic

Modeling of caches

June 21, 2012

23 / 22

```

## Data file

| A                                               | ctivities                                                                                                                                               | Emac                    | s                                                |                                     | Т                                                                                | ue 18:25                                 |                                                                                        | •                                    | en | ())<br><b>x</b>         | □ <b>,</b>                   | 🗬 stanisi            | c                           |  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------|----|-------------------------|------------------------------|----------------------|-----------------------------|--|

|                                                 |                                                                                                                                                         |                         |                                                  |                                     | emacs23@                                                                         | pawnee.im                                | ag.fr                                                                                  |                                      |    |                         |                              |                      | ×                           |  |

| Fi                                              | le Edit                                                                                                                                                 | Options E               | Buffers                                          | Tools Help                          |                                                                                  |                                          |                                                                                        |                                      |    |                         |                              |                      |                             |  |

|                                                 | <u> </u>                                                                                                                                                | e x                     |                                                  | § 🥱 🔏                               | ч 🖹 Q                                                                            |                                          |                                                                                        |                                      |    |                         |                              |                      |                             |  |

| <pre>####################################</pre> |                                                                                                                                                         |                         |                                                  |                                     |                                                                                  |                                          |                                                                                        |                                      |    |                         |                              |                      |                             |  |

|                                                 | # 1024       =TYPE_MEM       //The size in bytes of one block in memory for statical memory allocation fo?         #################################### |                         |                                                  |                                     |                                                                                  |                                          |                                                                                        |                                      |    |                         |                              |                      |                             |  |

| III                                             | 0<br>1<br>2<br>3<br>4<br>5                                                                                                                              | 1<br>1<br>1<br>1<br>1   | 19456<br>47104<br>7168<br>43008<br>11264<br>1024 | 0x20d9490<br>0x20d9490              | 1339162656<br>1339162656<br>1339162656<br>1339162656<br>1339162656<br>1339162656 | .528887<br>.539708<br>.541551<br>.547010 | 1339162656.<br>1339162656.<br>1339162656.<br>1339162656.<br>1339162656.<br>1339162656. | 539663<br>541354<br>546983<br>548162 |    | 0.00                    | 0776<br>1646<br>5432<br>1152 | 42<br>42<br>77<br>95 | 6><br>5><br>3><br>5>        |  |

| ~                                               | 6<br>7<br>8<br>Luka                                                                                                                                     | 1<br>1<br>1<br>Stanisic | 22528<br>3072<br>36864                           | 0x20d9490<br>0x20d9490<br>0x20d9490 | 1339162656<br>1339162656<br>1339162656<br>Modeli                                 | 550491                                   | 1339162656.<br>1339162656.<br>1339162656.                                              | 550794                               |    | 00.00<br>00.00<br>00.00 | 0303<br>3598                 | 99                   | 1<br>0<br>0<br>0<br>24 / 22 |  |

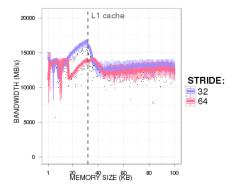

# Large Buffer Size

The drop around L2 is smooth, no sharp plateaus

Luka Stanisic

Modeling of caches

June 21, 2012 25 / 22

# Influence of Compiler Optimization Option

Using different compilation optimizations affect the performance Results from ARM Dual Cortex A9 1GHz Snowball:

Intel processors also show better performance with gcc=-O3 ,

Luka Stanisic

Modeling of caches

June 21, 2012 26 / 22