# Fences in weak memory models (extended version)

Jade Alglave, Luc Maranget, Susmit Sarkar, Peter Sewell

# ▶ To cite this version:

Jade Alglave, Luc Maranget, Susmit Sarkar, Peter Sewell. Fences in weak memory models (extended version). Formal Methods in System Design, 2012, 40 (2), pp.170 - 205. 10.1007/s10703-011-0135-z. hal-01100778

# HAL Id: hal-01100778 https://inria.hal.science/hal-01100778

Submitted on 7 Jan 2015

HAL is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Fences in Weak Memory Models (Extended Version)

$\textbf{Jade Alglave}^{1,3} \, \cdot \, \textbf{Luc Maranget}^{1} \, \cdot \, \textbf{Susmit Sarkar}^{2} \, \cdot \, \textbf{Peter Sewell}^{2}$

the date of receipt and acceptance should be inserted later

Abstract We present a class of relaxed memory models, defined in Coq, parameterised by the chosen permitted local reorderings of reads and writes, and by the visibility of inter- and intra-processor communications through memory (e.g. store atomicity relaxation). We prove results on the required behaviour and placement of memory fences to restore a given model (such as Sequential Consistency) from a weaker one. Based on this class of models we develop a tool, diy, that systematically and automatically generates and runs litmus tests. These tests can be used to explore the behaviour of processor implementations and the behaviour of models, and hence to compare the two against each other. We detail the results of experiments on Power and a model we base on them.

#### 1 Introduction

Most multiprocessors exhibit subtle relaxed-memory behaviour, with writes from one thread not immediately visible to all others; they do not provide sequentially consistent memory [21]. For some, such as x86 [2,1,26,24,28] and Power [25], the vendor documentation is in inevitably-ambiguous informal prose, leading to confusion. Thus we have no foundation for software verification of concurrent systems code, and no target specification for hardware verification of microarchitecture. To remedy this state of affairs, we take a firmly empirical approach, developing, in tandem, testing tools and models of multiprocessor behaviour—the test results guiding model development and the modelling suggesting interesting tests. In this paper we make five contributions:

- 1. We introduce a class of axiomatic memory models, defined in Coq [13], which we show how to instantiate to produce Sequential Consistency (SC), Sparc Total Store Order (TSO) [30], and a Power model (see item 4 below).

- 2. We describe our diy testing tool. Much discussion of memory models has been in terms of *litmus tests* (e.g. **iriw** [14]): ad-hoc multiprocessor programs for which particular final states may be allowed on a given architecture. Given a

<sup>&</sup>lt;sup>1</sup> INRIA <sup>2</sup> University of Cambridge <sup>3</sup> Oxford University

potential violation of SC, div systematically and automatically generates litmus tests (including classical ones such as iriw) and runs them on the hardware. These tests can be used to explore the behaviour of processor implementations and also the outcomes permitted by a model, and hence to compare the two; we illustrate this by our exploration of Power machines.

- 3. We use diy to generate about 800 tests, running them up to 1e12 times on three Power machines. They identified a rarely occurring implementation error in Power 5 memory barriers (for which IBM is providing a workaround), and further suggest that Power 6 does not suffer from this.

- 4. Based on these, and on other test results, we developed an axiomatic memory model (the CAV 2010 model) for Power which captures several important aspects of the processor's behaviour. Notably, it describes the lack of multi-copy store atomicity [5,12], despite being in a simple global-time style rather than the per-processor timelines implied by the architecture text. It also models the ordering relaxations we observe and A-cumulative barriers [25]. The model is sound with respect to all our experimental results, though for some of the Power barriers it is weaker than one might like; we discuss this in detail.

- 5. We prove in Coq theorems about the strength and placement of memory barriers required to regain a strong model from a weaker model.

The experimental details and the sources and documentation of diy are available online<sup>1</sup>, as are the Coq development and typeset outlines of the proofs<sup>2</sup>, which are further described in the first author's PhD thesis [7]. This paper extends a conference paper in CAV 2010 [9], adding more explanation and more details of diy and of the axiomatic Power model introduced there.

## 2 Our class of models

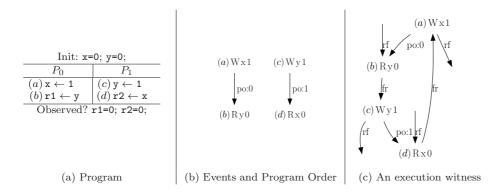

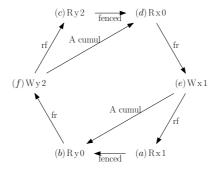

A memory model determines whether a candidate execution of a program is *valid*. For example, Fig. 1(a) shows a simple litmus test, comprising an initial state (which gathers the initial values of registers and memory locations used in the test), a program in pseudo- or assembly code, and a final condition on registers and memory (we write x, y for memory locations and r1, r2 for registers). If each location initially holds 0 (henceforth we omit the initial state if so), then, *e.g.* on x86 processors, there are valid executions with the specified final state [24].

# 2.1 Informal overview of our approach

We start here by explaining the concepts that we use at a high level. We then define these concepts formally in the forthcoming subsections.

Describing executions of programs We study concurrent programs such as the one given in Fig. 1(a). Each of these programs gives an initial state describing the initial values in memory locations and registers initially, e.g. x=0; y=0 in Fig. 1(a), meaning that we suppose that the memory locations x and y hold the value 0

$<sup>^{1}</sup>$  http://diy.inria.fr/

<sup>2</sup> http://diy.inria.fr/wmm/

Fig. 1 A program and a candidate execution

initially. Except when the examples are specific to our study of the Power architecture, *i.e.* in Sec. 6 and 7, we write the instructions in pseudo-code; for example  $x \leftarrow 1$  is a store of value 1 into memory location x, and  $r1 \leftarrow y$  is a load from memory location y into a register r1. We depict a concurrent program as a table, where the columns are processors (*e.g.*  $P_0$  and  $P_1$  in Fig. 1(a)), and the lines are labelled with letters—for example in Fig. 1(a), the first line, which holds  $x \leftarrow 1$ , is labelled (a).

We describe a candidate execution of a given program using *memory events*, corresponding to the memory accesses yielded by executing the instructions of the program. For example, we give in Fig. 1(b) the memory events of one candidate execution of the program of Fig. 1(a): the write event (a) W x 1 corresponds to the store  $x \leftarrow 1$  at line (a). In this candidate execution both reads read value 0.

In addition to these memory events, a candidate execution of a program consists of several relations over them. One of these relations represents the program order as given by an unfolding of a control-flow path through the text of the program—in any execution of the program Fig. 1(a), the execution of the instruction at line (a) is program-order-before execution of the instruction at line (b). This is expressed as the  $\stackrel{\text{po}}{\rightarrow}$  relation between the corresponding events in Fig. 1(b). Other relations represent the interaction with memory: the reads-from relation  $\stackrel{\text{rf}}{\rightarrow}$  indicates which write the value of a each read event comes from; and the write serialisation  $\stackrel{\text{ws}}{\rightarrow}$  represents the coherence order for each location (for each location, there is a total order over the writes to that location). Reads-from edges with no source or target represent reads from the initial state or writes that appear in the final state respectively.

Defining the validity of an execution We then define the validity of a given candidate execution as acyclicity checks of certain unions of these relations.

Many interesting candidate executions (and all the executions that we will show in this paper) contain at least one cycle, such as that depicted in Fig. 1(c). Typically, this cycle will exhibit the fact that the execution that we choose to depict is invalid in the Sequential Consistency (SC) model [21]. The execution in Fig. 1(c) is allowed in TSO and in Power, but not in SC, where at least one of the reads would have to read 1.

In addition, our test programs contain a constraint on the final state. For example, the program in Fig. 1(a) shows the line "Observed? r1=0;r2=0". We use several different keywords to express the final state of our programs. The keyword "Observed" (or its counterpart "Not observed") refers to empirical results. This means that we actually observed an execution satisfying the final state constraint on a given machine. When there is a question mark, as in "Observed?", this means that we question whether the outcome is observable or not on a given machine. The keyword "Allowed" (or its counterpart "Forbidden") refers to whether a given model allows (or forbids) the specified outcome. This means that we can deduce from the definition of the model that this outcome is allowed (or forbidden).

The fact that the specified final state of a given program—such as "Observed? r1=0; r2=0" in Fig. 1(a)—is observable or allowed relates to the graphs describing the executions of this program—such as the one given in Fig. 1(c).

Let us examine the Allowed/Forbidden case first. As we said above, the validity of an execution in the model we present here boils down to the presence of certain cycles in the execution graph. Thus, if an execution graph contains a cycle, then we have to examine if the model that we are studying allows some 'relaxation' of the relations that are involved in this cycle. If some relaxations are allowed, then the cycle does not forbid the execution, and the final state is allowed by the model. For example in Fig. 1(c), on a model such as SC where no relaxation is allowed, the cycle forbids the execution. On a model such as x86, where the program order between a write and a read may be relaxed, the cycle does not forbid the execution, for the program order relation (written  $\stackrel{\text{po}}{\rightarrow}$  in Fig. 1(c)) between (a) and (b) (and similarly (c) and (d)) is relaxed.

For the Observed/Not observed case, we have to run the test against hardware to check whether the specified final outcomes appears. If we observe a given final state, we sometimes can deduce which is the feature of the hardware—as represented by our model—that allows this outcome. For example, we were able to observe the final state of Fig. 1(a) on x86 machines. From this we deduce that the cycle in Fig. 1(c) does not forbid the execution on some x86 machines, and furthermore that the x86 model allows the reordering of write-read pairs. Of course, as usual with black-box testing, one cannot deduce anything with certainty from the absence of an empirical observation.

## 2.2 Events and program order

As sketched above, rather than dealing directly with programs, our models are in terms of the events  $\mathbb E$  occurring in a candidate program execution. A memory event m represents a memory access, specified by its direction (write or read), its location  $\log(m)$ , its value  $\operatorname{val}(m)$ , its processor  $\operatorname{proc}(m)$ , and a unique label. The store to  $\mathbf x$  with value 1 marked (a) in Fig. 1(a) generates the event (a) W x 1 in Fig. 1(b). Henceforth, we write r (resp. w) for a read (resp. write) event. We write  $\mathbb{M}_{\ell,v}$  (resp.  $\mathbb{R}_{\ell,v}$ ,  $\mathbb{W}_{\ell,v}$ ) for the set of memory events (resp. reads, writes) to a location  $\ell$  with value v (we omit  $\ell$  and v when quantifying over all of them). A barrier instruction generates a barrier event v; we write v for the set of all such events.

| Name                    | Notation                                    | Comment                                                                                                                                                                             | Sec. |

|-------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| program order           | $m_1 \stackrel{\text{po}}{\rightarrow} m_2$ | per-processor total order                                                                                                                                                           | 2.2  |

| dependencies            | $m_1 \stackrel{\mathrm{dp}}{\to} m_2$       | dependencies                                                                                                                                                                        | 2.2  |

| po-loc                  | $m_1 \stackrel{\text{po-loc}}{\to} m_2$     | program order restricted to the same location                                                                                                                                       | 2.5  |

| preserved program order | $m_1 \stackrel{\text{ppo}}{\to} m_2$        | pairs maintained in program order                                                                                                                                                   | 2.4  |

| read-from map           | $w \stackrel{\mathrm{rf}}{\to} r$           | links a write to a read reading its value                                                                                                                                           | 2.3  |

| external read-from map  | $w \stackrel{\mathrm{rfe}}{\to} r$          | $\stackrel{\mathrm{rf}}{\to}$ between events from distinct processors                                                                                                               | 2.4  |

| internal read-from map  | $w \stackrel{\mathrm{rfi}}{\to} r$          | $\stackrel{\mathrm{rf}}{\to}$ between events from the same processor                                                                                                                | 2.4  |

| global read-from map    | $w \stackrel{\text{grf}}{\rightarrow} r$    | $\stackrel{\mathrm{rf}}{	o}$ considered global                                                                                                                                      | 2.4  |

| write serialisation     | $w_1 \stackrel{\mathrm{ws}}{\to} w_2$       | total order on writes to the same location                                                                                                                                          | 2.3  |

| from-read map           | $r \stackrel{\mathrm{fr}}{\rightarrow} w$   | $r$ reads from a write preceding $w$ in $\stackrel{\text{ws}}{\rightarrow}$                                                                                                         | 2.3  |

| barriers                | $m_1 \stackrel{\mathrm{ab}}{\to} m_2$       | ordering induced by barriers                                                                                                                                                        | 2.4  |

| global happens-before   | $m_1 \stackrel{\mathrm{ghb}}{\to} m_2$      | union of global relations                                                                                                                                                           | 2.4  |

| communication           | $m_1 \stackrel{\mathrm{com}}{\to} m_2$      | $(m_1, m_2) \in (\stackrel{\mathrm{rf}}{\to} \cup \stackrel{\mathrm{ws}}{\to} \cup \stackrel{\mathrm{fr}}{\to}) \text{ (written } \stackrel{\mathrm{hb-seq}}{\to} \text{ in } [9])$ | 2.5  |

Fig. 2 Table of relations

The models are defined in terms of binary relations over these events, and Fig. 2 has a first table of the relations we use. The relations given in Fig. 2 are entirely generic; we give some more relations that are specific to Power in Fig. 17.

As usual, the program order  $\stackrel{\text{po}}{\to}$  is a total order amongst the events from the same processor that never relates events from different processors. It reflects the sequential execution of instructions on a single processor: given two instruction execution instances  $i_1$  and  $i_2$  that generate events  $e_1$  and  $e_2$ ,  $e_1 \stackrel{\text{po}}{\to} e_2$  means that a sequential processor would execute  $i_1$  before  $i_2$ . When instructions may perform several memory accesses, we take intra-instruction dependencies [26] into account to build a total order.

We postulate a  $\stackrel{\text{dp}}{\rightarrow}$  relation to model the dependencies between instructions, such as *data* or *control dependencies* [25, pp. 653-668]. This relation is a subrelation of  $\stackrel{\text{po}}{\rightarrow}$ , and always has a read as its source.

#### 2.3 Execution witnesses

Although  $\stackrel{\text{po}}{\to}$  conveys important features of program execution, e.g. branch resolution, it does not characterise an execution. To do so, we postulate, as part of the data of a candidate execution, two additional relations  $\stackrel{\text{ws}}{\to}$  and  $\stackrel{\text{rf}}{\to}$  over memory events.

Write serialisation We assume all values written to a given location  $\ell$  to be serialised, following a *coherence order*. This means, following the Power documentation [25, p.657, 1st col, last  $\S$ ], that all stores to a given memory location  $\ell$  are totally ordered:

Memory coherence refers to the ordering of stores to a single location. Atomic stores to a given location are *coherent* if they are serialised in some order, and no processor or mechanism is able to observe any subset of those stores as occurring in a conflicting order.

This property is widely assumed by modern architectures, including for example Sparc TSO [30] and x86-TSO [24].

Consequently, we define  $\stackrel{\text{ws}}{\rightarrow}$  as the union of the coherence orders for all memory locations, which must be well formed following the wf-ws predicate:

$$\text{wf-ws}(\overset{\text{ws}}{\to}) \; \triangleq \; \left(\overset{\text{ws}}{\to} \subseteq \bigcup_{\ell} (\mathbb{W}_{\ell} \times \mathbb{W}_{\ell})\right) \; \wedge \; \left(\forall \ell. \; \text{total-order}\left(\overset{\text{ws}}{\to}, (\mathbb{W}_{\ell} \times \mathbb{W}_{\ell})\right)\right)$$

Reads-from map We write  $w \stackrel{\mathrm{rf}}{\to} r$  to mean that r loads the value stored by w (so w and r must share the same location and value). Given a read r there exists a unique write w such that  $w \stackrel{\mathrm{rf}}{\to} r$ . The write w can be an *init* store when r loads from the initial state. The initial store to a location x is defined as the first write in the coherence order for x. Thus,  $\stackrel{\mathrm{rf}}{\to}$  must be well formed following the wf-rf predicate:

$$\text{wf-rf}(\overset{\text{rf}}{\to}) \triangleq \left( \overset{\text{rf}}{\to} \subseteq \bigcup_{\ell,v} (\mathbb{W}_{\ell,v} \times \mathbb{R}_{\ell,v}) \right) \wedge (\forall r, \exists! \, w. \, w \overset{\text{rf}}{\to} r)$$

From-read map It is useful to define a derived relation  $\stackrel{\text{fr}}{\to}$  (as in [6]) which gathers all pairs of reads r and writes w such that r reads from a write that is before w in  $\stackrel{\text{ws}}{\to}$  (as in Fig. 3):

$$r \stackrel{\text{fr}}{\rightarrow} w \triangleq \exists w'. w' \stackrel{\text{rf}}{\rightarrow} r \wedge w' \stackrel{\text{ws}}{\rightarrow} w$$

The significance of  $\stackrel{fr}{\rightarrow}$  is as follows. Some of the weaknesses of multiprocessor memory models arises from the fact that a write is not necessarily made available to all potential reading threads in one atomic step. In TSO models (e.g. for Sparc and x86-TSO), this is true in a relatively benign way: the writing thread might read 'early' from its own write before that is propagated to all other threads. In more relaxed models (e.g. for Power and ARM) there may be more complex behaviour, for example with a write being made available first to the writing thread itself, then to near-neighbours of that thread (that share some level of the cache hierarchy), and later to other threads. If one thinks of a write event as representing the point in time when a write has been made available to all threads, and a read event as the point when the value of the read is determined, then reads-from  $\stackrel{\text{rf}}{\rightarrow}$  edges are not necessarily forwards in time (a read can have read from a write before the write is made available to all), but a from-read  $\stackrel{\text{fr}}{\rightarrow}$  edge, from a read to a coherence-successor of the write it read from, is necessarily forwards in time (otherwise the read would have to read from the coherence-later write).

Execution witnesses We define an execution witness X as follows:

$$X \triangleq (\mathbb{E}, \stackrel{\text{po}}{\rightarrow}, \stackrel{\text{dp}}{\rightarrow}, \stackrel{\text{rf}}{\rightarrow}, \stackrel{\text{ws}}{\rightarrow})$$

The well-formedness predicate wf on execution witnesses is the conjunction of those for  $\stackrel{\text{ws}}{\rightarrow}$  and  $\stackrel{\text{rf}}{\rightarrow}$ :

$$\operatorname{wf}(X) \triangleq \operatorname{wf-ws}(\stackrel{\operatorname{ws}}{\to}) \wedge \operatorname{wf-rf}(\stackrel{\operatorname{rf}}{\to})$$

**Fig. 3** The  $\stackrel{fr}{\to}$  relation is derived from  $\stackrel{ws}{\to}$  and  $\stackrel{rf}{\to}$

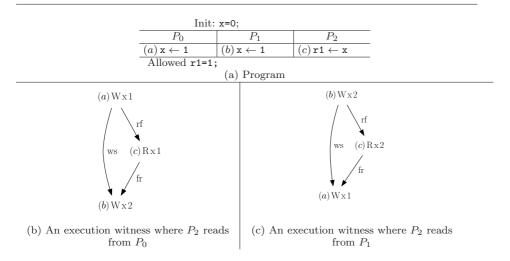

Fig. 4 A program and its two different write serialisations

Fig. 1(c) shows one particular execution witness for the test of Fig. 1(a). The load (d) reads the initial value of x, later overwritten by the store (a). Since the initial store to x comes first in  $\stackrel{\text{ws}}{\rightarrow}$ , hence before (a), we have  $(d) \stackrel{\text{fr}}{\rightarrow} (a)$ .

Note that an execution witness describes only one candidate execution of a program. A given program can have many candidate execution witnesses, with different control-flow paths, different values read from memory, different readsfrom relations, and different write serialisations; a memory model will permit some of these and forbid others. Consider for example the program given in Fig. 4(a). The processors  $P_0$  and  $P_1$  both write to the same location x. This program has two candidate executions, shown in Fig. 4(b) and (c), with different write serialisations. The one in Fig. 4(b) covers the case where  $P_0$ 's write is coherence-before  $P_1$ 's. The second one, in Fig. 4(c), covers the converse.

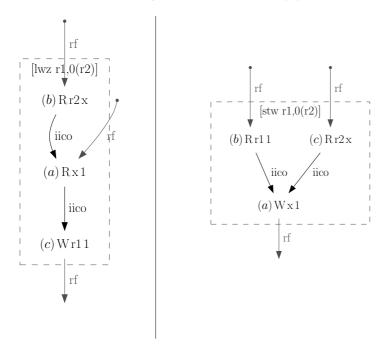

For an example of candidate executions differing in the writes that are the sources of a read-from edge, consider the program in Fig. 5(a). The processors  $P_0$  and  $P_1$  both write the value 1 into memory location x. The processor  $P_2$  reads from x. Hence, this program can have at least two distinct execution witnesses, given in Fig. 5(b) and (c). The one in Fig. 5(b) covers the case where  $P_2$  reads from  $P_0$ . The second one, given in Fig. 5(c), covers the case where  $P_2$  reads from  $P_1$ .

#### 2.4 Global Happens-Before

In the family of memory models we use in this paper, a candidate execution witness is *valid* if the memory events can be embedded in an acyclic *global happens-before* relation  $\stackrel{\mathrm{ghb}}{\to}$  (together with two auxiliary conditions detailed in Sec. 2.5). Each

${f Fig.~5}$  A program and two possible read-from maps

model is determined by the choice of relations which we include in this global happens-before relation. The position of a write in  $\stackrel{\mathrm{ghb}}{\Rightarrow}$  represents a point in global time when this write becomes visible to all processors (we say it is globally performed then); whereas the position of a read in  $\stackrel{\mathrm{ghb}}{\Rightarrow}$  represents the point in global time when the read takes place. Note that these are concepts associated with the model; the precise relationship between the model events and concrete microarchitectural events in processor implementations may be subtle — for example, in an implementation write might never actually be propagated to threads that do not read the associated cache line. There remain key choices as to which relations we include in  $\stackrel{\mathrm{ghb}}{\Rightarrow}$  (i.e. which we consider to be in global time), which leads us to define a class of models.

Globality Writes are not necessarily made available to all processors at once, so  $\overset{\text{rf}}{\to}$  edges are not necessarily included in  $\overset{\text{ghb}}{\to}$ . Let us distinguish between internal (resp. external)  $\overset{\text{rf}}{\to}$ , when the two events in  $\overset{\text{rf}}{\to}$  are on the same (resp. distinct) processor(s), written  $\overset{\text{rfi}}{\to}$  (resp.  $\overset{\text{rfe}}{\to}$ ):  $w \overset{\text{rfi}}{\to} r \triangleq w \overset{\text{rf}}{\to} r \land \text{proc}(w) = \text{proc}(r)$  and  $w \overset{\text{rfe}}{\to} r \triangleq w \overset{\text{rf}}{\to} r \land \text{proc}(w) \neq \text{proc}(r)$ . Some architectures allow store forwarding (or read own writes early [5]): the processor issuing a given write can read its value before any other participant accesses it. Then  $\overset{\text{rfi}}{\to}$  is not included in  $\overset{\text{ghb}}{\to}$ . Other architectures allow two processors sharing a cache to read a write issued by their neighbour w.r.t. the cache hierarchy before any other participant that does not share the same cache—a particular case of read others' writes early [5]. Then  $\overset{\text{rfe}}{\to}$  is not considered global. We write  $\overset{\text{grf}}{\to}$  for the subrelation of  $\overset{\text{rf}}{\to}$  included in  $\overset{\text{ghb}}{\to}$ .

In our class of models,  $\stackrel{\text{ws}}{\to}$  and  $\stackrel{\text{fr}}{\to}$  are always included in  $\stackrel{\text{ghb}}{\to}$ . Indeed, the write serialisation for a given location  $\ell$  is the order in which writes to  $\ell$  are globally performed. Moreover, as  $r \stackrel{\text{fr}}{\to} w$  expresses that the write w' from which r reads is globally performed before w, it forces the read r to be globally performed (since

a read is globally performed as soon as it is performed) before w is globally performed.

Preserved program order In any given architecture, certain pairs of events in the program order are guaranteed to occur in that order. We postulate a global relation  $\stackrel{\text{ppo}}{\to}$  gathering all such pairs. For example, the execution witness in Fig. 1(c) is only valid if the writes and reads to different locations on each processor have been reordered. Indeed, if these pairs were forced to be in program order, we would have a cycle in  $\stackrel{\text{ghb}}{\to}$ : (a)  $\stackrel{\text{ppo}}{\to}$ : (b)  $\stackrel{\text{fr}}{\to}$ : (c)  $\stackrel{\text{ppo}}{\to}$ : (d)  $\stackrel{\text{fr}}{\to}$ : (a).

Barrier constraints Architectures also provide barrier instructions, e.g. the Power sync (discussed in Sec. 3) to enforce ordering between pairs of events. We postulate a global relation  $\stackrel{\text{ab}}{\rightarrow}$  gathering all such pairs.

Architectures We call a particular model of our class an architecture, written A (or  $A^{\epsilon}$  when  $\stackrel{\text{ab}}{\to}$  is empty). Let ppo (resp. grf, ab, ghb) be the function returning the  $\stackrel{\text{ppo}}{\to}$  (resp.  $\stackrel{\text{grf}}{\to}$ ,  $\stackrel{\text{ab}}{\to}$  and  $\stackrel{\text{ghb}}{\to}$ ) relation when given an execution witness. Thus, we have:

$$A \triangleq (ppo, grf, ab)$$

We define  $\stackrel{\text{ghb}}{\rightarrow}$  as the union of the global relations:

$$\overset{\mathrm{ghb}}{\rightarrow} \overset{\triangle}{\rightarrow} \overset{\mathrm{ppo}}{\rightarrow} \cup \overset{\mathrm{ws}}{\rightarrow} \cup \overset{\mathrm{fr}}{\rightarrow} \cup \overset{\mathrm{grf}}{\rightarrow} \cup \overset{\mathrm{ab}}{\rightarrow}$$

2.5 Validity of an execution w.r.t. an architecture

We now add two sanity conditions to the above.

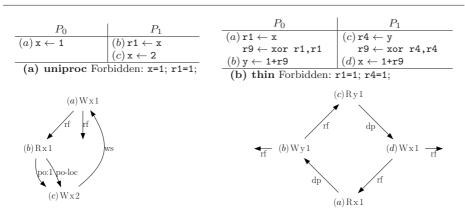

Uniprocessor First, we require each processor to respect memory coherence for each location [16]. If a processor writes e.g. v to  $\ell$  and then reads v' from  $\ell$ , v' should not precede v in the write serialisation. We define the relation  $\overset{\text{po-loc}}{\to}$  over accesses to the same location in the program order, and require  $\overset{\text{po-loc}}{\to}$ ,  $\overset{\text{rf}}{\to}$ ,  $\overset{\text{ws}}{\to}$  and  $\overset{\text{fr}}{\to}$  to be compatible (writing  $\overset{\text{com}}{\to}$  for  $\overset{\text{rf}}{\to} \cup \overset{\text{ws}}{\to} \cup \overset{\text{fr}}{\to}$ ):

$$m_1 \stackrel{\text{po-loc}}{\to} m_2 \triangleq m_1 \stackrel{\text{po}}{\to} m_2 \wedge \text{loc}(m_1) = \text{loc}(m_2)$$

$$\text{uniproc}(X) \triangleq \text{acyclic}(\stackrel{\text{com}}{\to} \cup \stackrel{\text{po-loc}}{\to})$$

For example, in Fig. 6 (a), the final value of x shows that the write (a) is the last one in coherence order. Since  $\stackrel{\text{ws}}{\to}$  is a total order of the writes to x, we have  $(c) \stackrel{\text{ws}}{\to} (a)$ . Similarly, the final value of r1 shows that the read (b) read its value from the write (a), hence  $(a) \stackrel{\text{rf}}{\to} (b)$ . The uniproc check on this program formalises the fact that the cycle  $(a) \stackrel{\text{rf}}{\to} (b) \stackrel{\text{po-loc}}{\to} (c) \stackrel{\text{ws}}{\to} (a)$  invalidates this execution: (b) cannot read from (a) as it is a future value of x in  $\stackrel{\text{ws}}{\to}$ .

Fig. 6 Invalid executions according to the uniproc and thin criteria

Thin air Second, we rule out programs where values come out of thin air [23]. This means that we forbid certain causal loops, following the terminology employed in the Alpha documentation [10].

Consider the test given in Fig. 6 (b). In this example, the write (b) to y on  $P_0$  is dependent on the read (a) from x on  $P_0$ , because the xor instruction between them does a calculation on the value written by (a) in r1, and writes the result into r9, later used by (b). Similarly on  $P_1$ , (c) and (d) are dependent. Suppose the read (a) from x on  $P_0$  reads from the write (d) to x on  $P_1$ , and similarly the read (c) from y on  $P_1$  reads from the write (b) to y on  $P_0$ , as depicted by the execution in Fig. 6 (b). In this case, the values read by (a) and (c) seem to come out of thin air, because they cannot be determined. We formalise the check that forbids such a scenario as follows:

$$thin(X) \triangleq acyclic(\stackrel{rf}{\rightarrow} \cup \stackrel{dp}{\rightarrow})$$

All together We define the validity of an execution w.r.t. an architecture A as the conjunction of three checks independent of the architecture, namely wf(X), uniproc(X) and thin(X) with a last one that characterises the architecture:

$$A.valid(X) \triangleq wf(X) \wedge uniproc(X) \wedge thin(X) \wedge acyclic(ghb(X))$$

# 2.6 Comparing architectures via validity predicates

From our definition of validity arises a simple notion of comparison among architectures.  $A_1 \leq A_2$  means that  $A_1$  is weaker than  $A_2$ :

$$A_1 \leq A_2 \triangleq (\overset{\text{ppo}_1}{\rightarrow} \subseteq \overset{\text{ppo}_2}{\rightarrow}) \land (\overset{\text{grf}_1}{\rightarrow} \subseteq \overset{\text{grf}_2}{\rightarrow})$$

The validity of an execution is decreasing w.r.t. the strength of the predicate; *i.e.* a weak architecture exhibits at least all the behaviours of a stronger one:

#### Theorem 1 (Validity is decreasing)

$$\forall A_1 A_2, (A_1 < A_2) \Rightarrow (\forall X, A_2^{\epsilon}. \operatorname{valid}(X)) \Rightarrow A_1^{\epsilon}. \operatorname{valid}(X))$$

Programs running on an architecture  $A_1^{\epsilon}$  exhibit executions that would be valid on a stronger architecture  $A_2^{\epsilon}$ ; we characterise all such executions as follows:

$$A_1.\mathrm{check}_{A_2}(X) \triangleq \mathrm{acyclic}(\overset{\mathrm{grf}_2}{\to} \cup \overset{\mathrm{ws}}{\to} \cup \overset{\mathrm{fr}}{\to} \cup \overset{\mathrm{ppo}_2}{\to})$$

Then, we show that executions that are valid on  $A_1$  and that satisfy this predicate are valid on  $A_2$  and conversely:

#### Theorem 2 (Characterisation)

$$\forall A_1 A_2, \ (A_1 \leq A_2) \Rightarrow (\forall X, (A_1^{\epsilon}.valid(X) \land A_1.check_{A_2}(X)) \Leftrightarrow A_2^{\epsilon}.valid(X))$$

These two theorems, though fairly simple, will be useful to compare two models and to restore a strong model from a weaker one, as in Sec. 3.

# 2.7 Examples

We propose here alternative formulations of Sequential Consistency (SC) [21] and Sparc's Total Store Ordering (TSO) [30] in our framework, which we proved equivalent to the original definitions. We omit proofs and the formal details for brevity, but they can be found at http://diy.inria.fr/wmm. We write po(X) (resp. rf(X), rfe(X)) for the function extracting the  $\stackrel{po}{\rightarrow}$  (resp.  $\stackrel{rf}{\rightarrow}$ ,  $\stackrel{rfe}{\rightarrow}$ ) relation from X. We define notations to extract pairs of memory events from the program order:  $MM \triangleq \lambda X. ((\mathbb{M} \times \mathbb{M}) \cap po(X)), RM \triangleq \lambda X. ((\mathbb{R} \times \mathbb{M}) \cap po(X))$  and  $WW \triangleq \lambda X. ((\mathbb{W} \times \mathbb{W}) \cap po(X)).$

SC allows no reordering of events ( $\stackrel{\mathrm{ppo}}{\to}$  equals  $\stackrel{\mathrm{po}}{\to}$  on memory events). In addition, SC makes writes available to all processors as soon as they are issued ( $\stackrel{\mathrm{rf}}{\to}$  are global). By this we mean that write events take immediately their place in the global-happens before relation, *i.e.* that once they become to one processor, they are visible to all processors. Thus, there is no need for barriers, and any architecture is weaker than SC:

$$SC \triangleq (MM, rf, \lambda X.\emptyset).$$

The following criterion characterises, as in Sec. 2.6, valid SC executions on any architecture:  $A.\operatorname{check}_{SC}(X) = \operatorname{acyclic}(\stackrel{\operatorname{com}}{\to} \cup \stackrel{\operatorname{po}}{\to})$ . Thus, the outcome of Fig. 1 will never be the result of an SC execution, as it exhibits the cycle:  $(a) \stackrel{\operatorname{po}}{\to} (b) \stackrel{\operatorname{fr}}{\to} (c) \stackrel{\operatorname{po}}{\to} (d) \stackrel{\operatorname{fr}}{\to} (a)$ .

TSO allows two relaxations [5]: write to read program order, meaning its  $\stackrel{\mathrm{PPO}}{\rightarrow}$  includes all pairs but the store-load ones  $(ppo_{tso} \triangleq (\lambda X. (RM(X) \cup WW(X)))$  and read own write early  $(\stackrel{\mathrm{rfi}}{\rightarrow}$  are not global). We elide barrier semantics, detailed in Sec. 3:  $TSO^{\epsilon} \triangleq (ppo_{tso}, \mathrm{rfe}, \lambda X.\emptyset)$ . Sec. 2.6 shows the following criterion characterises valid executions (w.r.t. any  $A \leq TSO$  that would be valid on  $TSO^{\epsilon}$ , e.g. in Fig. 1:  $A.\mathrm{check}_{TSO}(X) = \mathrm{acyclic}(\stackrel{\mathrm{ws}}{\rightarrow} \cup \stackrel{\mathrm{fr}}{\rightarrow} \cup \stackrel{\mathrm{rfe}}{\rightarrow} \cup \stackrel{\mathrm{ppo-tso}}{\rightarrow})$ .

#### 3 Semantics of barriers

In this section we characterise the semantics and placement in the code that barriers should have to restore a stronger model from a weaker one.

It is clearly enough to have  $w \stackrel{\text{ab}_1}{\to} r$  whenever  $w \stackrel{\text{grf}_2}{\to} r$  holds to restore store atomicity, *i.e.* a barrier ensuring  $\stackrel{\text{rf}}{\to}$  is global. But then a processor holding such a barrier placed after r would have to wait until w is globally performed before executing the read. We provide a less costly requirement: consider the case where  $w \stackrel{\text{rf}}{\to} r \stackrel{\text{po}}{\to} m$ , where r may take its value before w is visible to all processors. Inserting a barrier instruction that has our semantics between the instructions generating r and m only forces the processor generating r and m to delay m until w is globally performed.

We give here an intuition of the strength that the barriers of the architecture  $A_1$  should have to restore the stronger  $A_2$ . They should:

- 1. restore the pairs that are preserved in the program order on  $A_2$  and not on  $A_1$ , which is a static property;

- 2. compensate for the fact that some writes may not be globally performed at once on  $A_1$  while they are on  $A_2$ , which we model by (some subrelation of)  $\stackrel{\text{rf}}{\rightarrow}$  not being global on  $A_1$  while it is on  $A_2$ ; this is a dynamic property.

Formally, we write  $\stackrel{\mathbf{r}_2 \setminus \mathbf{r}}{\Rightarrow} \stackrel{\triangle}{\Rightarrow} \stackrel{\mathbf{r}_2}{\Rightarrow} \stackrel{\mathbf{r}_3}{\Rightarrow} \stackrel{\mathbf{r}_4}{\Rightarrow} \text{ for the set difference. In addition, we write } x \stackrel{\mathbf{r}_3}{\Rightarrow} y \stackrel{\triangle}{\Rightarrow} \exists z. x \stackrel{\mathbf{r}_4}{\Rightarrow} z \wedge z \stackrel{\mathbf{r}_2}{\Rightarrow} y \text{ for the sequence of two relations. Given } A_1 \leq A_2,$  we define the predicate fb (fully barriered) on executions X by

$$A_1.\mathrm{fb}_{A_2}(X) \; \triangleq \; \left( (\stackrel{\mathrm{ppo}_2}{\to})^{\scriptscriptstyle 1} \right) \cup (\stackrel{\mathrm{grf}_2}{\to})^{\scriptscriptstyle 1}; \stackrel{\mathrm{ppo}_2}{\to}) \right) \; \subseteq \; \stackrel{\mathrm{ab}_1}{\to}$$

We can then prove that the above condition on  $\stackrel{\mathrm{ab}_1}{\to}$  is sufficient to regain  $A_2^{\epsilon}$  from  $A_1$ :

#### Theorem 3 (Barrier guarantee)

$$\forall A_1 A_2, (A_1 \leq A_2) \Rightarrow (\forall X, A_1. \operatorname{valid}(X) \land A_1. \operatorname{fb}_{A_2}(X) \Rightarrow A_2^{\epsilon}. \operatorname{valid}(X))$$

The static property of barriers is expressed by the condition  $\overset{\text{ppo}_{\circ}}{\to} \overset{\text{l}}{\to} \overset{\text{ab}_{\circ}}{\to}$ . A barrier provided by  $A_1$  should ensure that the events generated by a same processor are globally performed in program order if they are on  $A_2$ . In this case, it is enough to insert a barrier between the instructions that generate these events.

The dynamic property of barriers is expressed by the condition  $\overset{\text{grf}}{\to}^{\downarrow_1}$ ;  $\overset{\text{ppo}}{\to}^{\circ} \subseteq \overset{\text{ab}_1}{\to}$ . A barrier provided by  $A_1$  should ensure store atomicity to the write events that have this property on  $A_2$ . This is how we interpret the cumulativity of barriers, as stated by Power [25], in our framework: the A-cumulativity (resp. B-cumulativity) property applies to barriers that enforce ordering of pairs in  $\overset{\text{rf}}{\to}$ ;  $\overset{\text{po}}{\to}$  (resp.  $\overset{\text{po}}{\to}$ ;  $\overset{\text{rf}}{\to}$ ). We consider a barrier that only preserves pairs in  $\overset{\text{po}}{\to}$  to be non-cumulative. Thm. 3 states that, to restore  $A_2$  from  $A_1$ , it suffices to insert an A-cumulative barrier between each pair of instructions such that the first one in the program order reads from a write which is to be globally performed on  $A_2$  but is not on  $A_1$ .

| iriw                    |                                                                                                               |                      |                        |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------|----------------------|------------------------|--|

| $P_0$                   | $P_1$                                                                                                         | $P_2$                | $P_3$                  |  |

| $(a)$ r1 $\leftarrow$ x | $(c)$ r2 $\leftarrow$ y                                                                                       | $(e) x \leftarrow 1$ | $(f)$ y $\leftarrow$ 2 |  |

| $(b)$ r2 $\leftarrow$ y | $ \begin{array}{c} (c)\mathtt{r2} \leftarrow \mathtt{y} \\ (d)\mathtt{r1} \leftarrow \mathtt{x} \end{array} $ |                      |                        |  |

Observed? 0:r1=1; 0:r2=0; 1:r2=2; 1:r1=0;

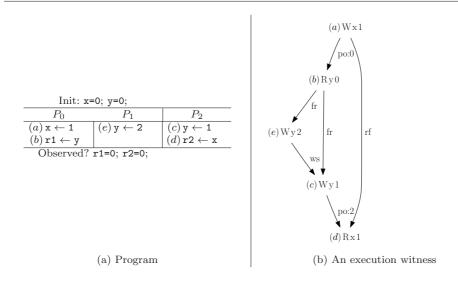

Fig. 7 The iriw test and a non-SC execution

Restoring SC We model an A-cumulative barrier as a function returning an ordering relation when given a placement of the barriers in the code:

$$\begin{array}{ccc} m_1 \stackrel{\text{fenced}}{\to} m_2 & \triangleq & \exists b.\, m_1 \stackrel{\text{po}}{\to} b \stackrel{\text{po}}{\to} m_2 \\ \text{A-cumul}(X, \stackrel{\text{fenced}}{\to}) & \triangleq & \stackrel{\text{fenced}}{\to} \cup \stackrel{\text{rf}}{\to} \stackrel{\text{fenced}}{\to} \\ \end{array}$$

The following corollary of Thm. 3 (with  $A_1 = A$  and  $A_2 = SC$ ) shows that inserting such a barrier between all  $\stackrel{\text{po}}{\rightarrow}$  pairs restores SC:

# Corollary 1 (Barriers restoring SC)

$$\forall A \ X, (A.valid(X) \land A-cumul(X, MM) \subseteq \stackrel{ab}{\rightarrow}) \Rightarrow SC.valid(X)$$

Consider e.g. the **iriw** test depicted in Fig. 7. The specified outcome may be the result of a non-SC execution on a weak architecture in the absence of barriers, as shown in Fig. 7. Our A-cumulative barrier placed between each pair of reads on  $P_0$  and  $P_1$  forbids this outcome, as shown in Fig. 8. The non-cumulative property of the barrier (expressed formally by  $\stackrel{\text{fenced}}{\rightarrow}$  being included in the definition of A-cumulative) ensures that none of the two pairs of reads can be reordered. The A-cumulative property of the barrier (expressed formally by  $\stackrel{\text{rf}}{\rightarrow}$ ;  $\stackrel{\text{fenced}}{\rightarrow}$  being included in the definition of A-cumulative) also ensures that the write (e) on  $P_2$  (resp. (y)  $P_3$ ) is globally performed before the second read (b) on  $P_0$  (resp. (d) on  $P_1$ ).

Thus, we force a program to have an SC behaviour by fencing all pairs in  $\stackrel{\text{po}}{\to}$ . Yet, it would be enough to invalidate non-SC executions, by fencing only the  $\stackrel{\text{po}}{\to}$  pairs in the  $\stackrel{\text{com}}{\to} \cup \stackrel{\text{po}}{\to}$  cycles of these executions. We believe the static analysis of [29] (based on compile-time approximation of  $\stackrel{\text{com}}{\to} \cup \stackrel{\text{po}}{\to}$  cycles) applies to architectures relaxing store atomicity, if their barriers offer A-cumulativity.

| iriw                                   |                         |                      |                        |  |

|----------------------------------------|-------------------------|----------------------|------------------------|--|

| $P_0$                                  | $P_1$                   | $P_2$                | $P_3$                  |  |

| $(a)$ r1 $\leftarrow$ x                | $(c)$ r2 $\leftarrow$ y | $(e) x \leftarrow 1$ | $(f)$ y $\leftarrow$ 2 |  |

| fence                                  | fence                   |                      |                        |  |

| $(b)\mathtt{r2} \leftarrow \mathtt{y}$ | $(d)$ r1 $\leftarrow$ x |                      |                        |  |

Observed? 0:r1=1; 0:r2=0; 1:r2=2; 1:r1=0;

Fig. 8 Study of iriw with A-cumulative barriers

#### 4 diy: a testing tool

We now present our diy (do it yourself) tool, which generates litmus tests in x86 or Power assembly code by enumerating possible violations of SC in terms of our axiomatic model, i.e., cycles in  $\stackrel{\text{com}}{\to} \cup \stackrel{\text{po}}{\to}$ . A diy tutorial is available at http://diy.inria.fr.

# 4.1 Informal overview of our method

We start here by explaining the idea of the method employed by diy at a high level, then give further details in the following subsections.

As we described in the previous section, the outcome of the **iriw** test in Fig. 7 leads to the  $\stackrel{\text{com}}{\to} \cup \stackrel{\text{po}}{\to}$  cycle depicted there. Conversely, that test can be built from the sequence  $\stackrel{\text{rfe}}{\to} ; \stackrel{\text{po}}{\to} ; \stackrel{\text{fre}}{\to} ; \stackrel{\text{fre}}{\to} ; \stackrel{\text{po}}{\to} ; \stackrel{\text{fre}}{\to} ; \stackrel{\text{po}}{\to} ; \stackrel{\text{fre}}{\to} ; \stackrel{\text{fre}}{\to$

More precisely, a global cycle in an execution graph forbids the specified outcome of a test in the model, as we explained in Sec. 2. This means that if a machine implements exactly the studied model, then the outcome of this test should not be observed. To check this, we thus build tests from cycles in execution graphs. If the outcome of a test is observed, we conclude that the cycle from which it is generated does not actually forbid the outcome.

In addition, to make the analysis of the results of such tests feasible, we generate our cycles so that there can be only one possible reason—in the model—why the

outcome can be exhibited. For example, in the cycle  $\stackrel{\text{rfe}}{\to}; \stackrel{\text{po}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{po}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{po}}{\to}; \stackrel{\text{fre}}{\to}; \stackrel{\text{fre$

Of course, this practice supposes that the other relations from which a cycle is built are global. We check this assumption by generating cycles where all the relations are global in the model, and run them to check that their outcomes are not observed.

#### 4.2 Candidate Relaxations

We wrote the diy testing tool to automatically generate litmus tests that exercise relations specified by the user. When given a certain sequence of relations, diy produces tests such that one of their executions contains at least one occurrence of the given sequence. Hence, if we want to check whether the external read-from maps are relaxed on a given machine, we specify  $\stackrel{\text{rfe}}{\rightarrow}$  to be relaxed to diy, following the concrete syntax we give in Fig. 9.

We write Po for a program order candidate relaxation and Dp for a dependency. We handle the communication relaxations as follows: we write Rf for a read-from, Ws for a write serialisation, Fr for a from-read. We also deal with barrier candidate relaxation: thus, we write Fence for a non-cumulative barrier, ACFence for an Acumulative one, BCFence for a B-cumulative one, and ABCFence for the sequence of an A- and a B-cumulative ones.

We specify if the two accesses related by the candidate relaxation access the same location by the letter s; we use the letter d if they access different locations. We specify the directions of the accesses related by the candidate relaxation, using W for write and R for read. Note that in the case of a dependency relation Dp, we just need to specify the direction of the target access, since dependency candidate relaxations always have a read as their source, following the definition of the  $\stackrel{\mathrm{dp}}{\to}$  relation given in Sec. 2.2.

For communication candidate relaxations such as Rf, Fr or Ws, we specify whether the candidate relaxation is internal (resp. external)—i.e. relating two accesses that belong to the same processor (resp. distinct processors)— by the letter i (resp. e).

Thus Rfe represents a  $\stackrel{\text{rfe}}{\to}$  arrow and Fre a  $\stackrel{\text{fre}}{\to}$  arrow. The candidate relaxation DpdR should be read as (1) Dp, which means that we generate a  $\stackrel{\text{dp}}{\to}$  arrow, (2) R, which means that this arrow targets a read, and (3) d, which means that the two accesses have different source and target locations. For Power, we instantiate the barrier candidate relaxation Fence with either Sync or LwSync.

Note that some of the candidate relaxations might be redundant. For example PosWW (two write events to the same location in program, hence on the same processor) is a particular case of Wsi (internal write serialisation). Yet, we actually care for this redundancy, for two reasons. First, this helps us covering all possibilities in enumerating test cases for model exploration. Second, it helps us to spot precisely the reason why a given test might reveal a bug in a hardware implementation.

| Name                | Notation                                                    |

|---------------------|-------------------------------------------------------------|

| program order       | Po(s d)(W R)(W R)                                           |

| dependencies        | $\mathrm{Dp}(\mathrm{s} \mathrm{d})(\mathrm{W} \mathrm{R})$ |

| read-from map       | Rf(i e)                                                     |

| write serialisation | Ws(i e)                                                     |

| from-read map       | Fr(i e)                                                     |

| barriers            | Fence(s d)(W R)(W R)                                        |

| A-cumulativity      | $ACFenceld_1d_2 \triangleq [Rfe; Fenceld_1d_2]$             |

| B-cumulativity      | $BCFenceld_1d_2 \triangleq [Fenceld_1d_2; Rfe]$             |

| AB-cumulativity     | ABCFence $ld_1d_2 \triangleq [Rfe; Fenceld_1d_2; Rfe]$      |

Fig. 9 Table of Candidate Relaxations

```

#rfe PPC conf file

-arch PPC

-nprocs 4

-size 6

-name rfe

-safe Fre DpdR

-relax Rfe

```

Fig. 10 Example Configuration File for diy

## 4.3 Input and Output of the diy tool

In practice, the diy tool takes as input a configuration file such as the one in Fig. 10. This configuration file forces diy to generate tests in Power assembly up to 4 processors, as specified by the -arch PPC and -nprocs 4 arguments, so that the number of relations involved in the generated cycles is 6 at most, because of the -size 6 argument. Moreover, the candidate relaxations Fre (external from-read map) and DpdR (data dependency between two reads from distinct locations) are considered global, and Rfe is considered relaxed, as specified by the -safe Fre DpdR and -relax Rfe arguments. Finally, all the tests generated by diy running on this configuration file will have the prefix rfe in their name, followed by a fresh number, as specified by the -name rfe argument.

The tool outputs x86 or Power assembly tests. More precisely, the tool internally generates cycles from the candidate relaxations supplied as argument to the -safe and -relax specifications, up to the specified bounds on cycle length and number of processors. Each cycle then commands the generation of one test.

# 4.4 Exercising One Relaxation at a Time

So as to make the analysis of the testing results feasible, we focus on tests which exercise a single weakness of the memory model at a time. Hence, if the outcome of a given test is exhibited, we know that the feature we tested is used by the machine on which we ran the test.

For example, suppose that we modify the test of Fig. 7 and impose dependencies between the pairs of reads on  $P_0$  and  $P_1$ , so that these dependencies are global, e.g. by being included in  $\stackrel{\text{ppo}}{\rightarrow}$ . Hence (a) is in data dependency with (b),

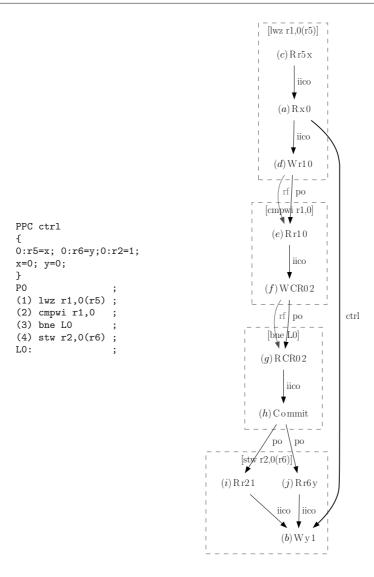

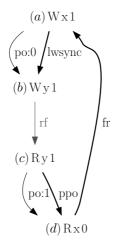

Fig. 11 iriw with dependencies in Power assembly

and so is (c) with (d), resulting in the cycle  $\xrightarrow{\text{rfe}}$ ;  $\xrightarrow{\text{ppo}}$ ;  $\xrightarrow{\text{fre}}$ ;  $\xrightarrow{\text{ppo}}$ ;  $\xrightarrow{\text{fre}}$ . This corresponds to the test given in Fig. 11, written in Power assembly code. The xor r3,r1,r1 between the load (b) and the load (c) on  $P_0$  implements such a dependency.

In this case the only reason why the specified outcome may arise is the non-globality of external read-from maps. Hence, the test of Fig. 11 is significant to check whether an architecture relaxes the atomicity of stores. More generally, we say that a test built from a cycle containing global relations only and a relation r targets r, because it can exhibit its outcome only because of r being relaxed. We shall also make use of tests built from global relations only, such a test is called a safe test.

#### 4.5 Cycle Generation

The input to diy must specify which candidate relaxations are to be assumed not relaxed (considered global, or safe) and which are to be investigated. When given a pool of safe candidate relaxations, a single potential relaxation to be investigated, and a size n (i.e. the number of arrows in the cycle, e.g. 6 for the **iriw** test of Fig. 7), diy generates cycles up to size n that contains at least one occurrence of the non-global candidate relaxation. If no non-global candidate relaxation is specified, diy generates cycles up to size n that contain the specified global candidate relaxations.

We do not generate tests for all these cycles: we eliminate some sequences of candidate relaxations. First, we eliminate any sequence of two candidate relaxations when the target of the first one is incompatible with the source of the second one: for example, we eliminate a sequence  $\stackrel{\text{Rfe}}{\longrightarrow}$ ;  $\stackrel{\text{Rfe}}{\longrightarrow}$  because the target of the first  $\stackrel{\text{Rfe}}{\longrightarrow}$  is a read, whereas the source of the second one is a write. Notice that no assembly program exists that corresponds to such cycles. However, eliminating impossible sequences early accelerates the production of cycles. More significantly, diy eliminate some additional sequences of candidate relaxations:

- 1. For communication candidate relaxations (*i.e.* Ws, Fr and Rf), we do not generate the sequence [Ws\_;Ws\_] for it reduces to Ws\_ in the model. Similarly, we do not generate the sequence [Ws\_;Fr\_], for it reduces to Fr\_ in the model. Hence we generate only five sequences of communication candidate relaxations, namely Ws\_, Fr\_, Rf\_, [Ws\_;Rf\_] and [Fr\_;Rf\_].

- 2. For program order candidate relaxations, we do not generate sequences [po<sub>1</sub>;po<sub>2</sub>] when the sequence is subsumed by another safe candidate relaxation (where po<sub>1</sub> and po<sub>2</sub> range over Po, Dp, Fence, and internal communication (*i.e.* Rfi, Fri and Wsi)). This means for example that, if FencedWR and Fence\_WW

Fig. 12 A program and a candidate execution

are safe, we do not generate [FencedWR;PodRW], for it reduces to Fence\_WW (assumed safe).

As a result, we do not generate all cycles up to a given size. However, the executions associated to the cycles we discard (for example a cycle involving a sequence [Fr\_;Ws\_] feature other shorter cycles (the cycle where [Fr\_;Ws\_] is reduced to Fr\_), which are generated.

Consider for example the test given in Fig. 12(a), which corresponds to the test of Fig. 1(a), where we added a new processor holding the store (e) y  $\leftarrow$  2. In this case, the final state of interest to us is still the one specified in Fig. 1, *i.e.* r1=0; r2=0;. This final state corresponds to the execution witness given in Fig. 12(b). More precisely, this final state corresponds to the cycle  $(a) \xrightarrow{\text{PodWR}} (b) \xrightarrow{\text{Fre}} (e) \xrightarrow{\text{Wse}} (c) \xrightarrow{\text{PodWR}} (d) \xrightarrow{\text{Fre}} (a)$ .

Observe that the read from y at line (b) on  $P_0$  is in  $\stackrel{\mathrm{fr}}{\hookrightarrow}$  with the write (e) to y on  $P_2$ , because of the final value of register r1. Moreover, in this particular execution, the write (e) to y on  $P_1$  is in  $\stackrel{\mathrm{ws}}{\rightarrow}$  before the write (c) to y on  $P_2$ . Therefore, by definition of  $\stackrel{\mathrm{fr}}{\rightarrow}$  and since  $\stackrel{\mathrm{ws}}{\rightarrow}$  is transitive, we know that  $(b) \stackrel{\mathrm{fr}}{\rightarrow} (c)$  as well. Thus, the final state corresponds to the shorter cycle  $(a) \stackrel{\mathrm{PodWR}}{\rightarrow} (b) [\stackrel{\mathrm{Fre}}{\rightarrow} ; \stackrel{\mathrm{Wse}}{\rightarrow} ](c) \stackrel{\mathrm{PodWR}}{\rightarrow} (d) \stackrel{\mathrm{Fre}}{\rightarrow} (a)$ , i.e.  $(a) \stackrel{\mathrm{PodWR}}{\rightarrow} (b) \stackrel{\mathrm{Fre}}{\rightarrow} (c) \stackrel{\mathrm{PodWR}}{\rightarrow} (d) \stackrel{\mathrm{Fre}}{\rightarrow} (a)$ , from which we generate the test of Fig. 1(a). Thus in such a case, we would generate only the test of Fig. 1(a), and not the test of Fig. 12(a).

### 4.6 Code Generation

diy interprets a sequence of candidate relaxations as a cycle from which it either computes a litmus test or fails. The final condition of a generated test is a conjunction of equalities on the values held by registers and memory locations in the final state, which ensures that at least one of the execution witnesses of this test includes a cycle following the input sequence.

#### 4.6.1 Algorithm

Test generation performs the following successive steps:

- 1. We map the edge sequence to a circular double-linked list. The cells represent memory events, with direction, location, and value fields, together with the edge starting from the event. This list represents the *input cycle* and will appear in at least one of the execution witnesses of the produced test.

- 2. A linear scan sets the directions (write or read) of the events, by comparing each target direction with the following source direction. When they are equal, the in-between cell direction is set to the common value; otherwise (e.g. Rfe; Rfe), the generation fails.

- 3. We pick an event e which is the target of a candidate relaxation specifying a location change. If there are none, the generation fails. Otherwise, a linear scan starting from e sets the locations of each event. At the end of the scan, if e and its predecessor have the same location  $(e.g. \xrightarrow{\text{Rfe}} e \xrightarrow{\text{PodRW}})$ , the generation fails, since we picked e to correspond to a location change.

- 4. We cut the input cycle into maximal sequences of events with the same location, each being scanned w.r.t. the cycle order: we give the value 1 to the first write in this sequence, 2 to the second one, etc. For each location in cycle, the sequence of values 0, 1, etc. defines a certain write serialisation order, which the final condition of test will characterise (step 7 below).

- 5. We define significant reads as the sources of  $\stackrel{fr}{\rightarrow}$  edges and the targets of  $\stackrel{rf}{\rightarrow}$  edges. We associate each significant read with the write on the other side of the edge. In the  $\stackrel{rf}{\rightarrow}$  case, the value of the read is the one of its associated write. In the  $\stackrel{fr}{\rightarrow}$  case, the value of the read is the value of the predecessor of its associated write in  $\stackrel{ws}{\rightarrow}$ , i.e. by construction the value of its associated write minus 1 (see step 4). Non-significant reads do not appear in the test condition.

- 6. We cut the cycle into maximal sequences of events from the same processor, each being scanned, generating load instructions to (resp. stores from) fresh registers for reads (resp. writes). We insert some code implementing a dependency in front of events targeting  $\stackrel{\mathrm{dp}}{\to}$  and the appropriate barrier instruction for events targeting  $\stackrel{\mathrm{fenced}}{\to}$  edges. We build the initial state at this step: stores and loads take their addresses from fresh registers, and their contents (addresses of memory locations) are defined in the initial state. Part of the final condition is also built: for any significant read with value v resulting in a load instruction to register r, we add the equality r=v.

- 7. We complete the final condition to characterise write serialisations. The write serialisation for a given location x is defined by the sequence of values 0 (initial value of x), ..., n, where n is the last value allocated for location x at step 4. If n is 0 or 1 then no addition to the final condition needs to be performed, because the write serialisation is either a singleton or a pair. If n is 2, we add the equality x = 2. Otherwise (n > 2), we add an observer to the program, i.e. we add a thread performing n loads from x to registers  $r1, \ldots, rn$  and add the equalities  $r1 = 1 \land \ldots \land rn = n$  to the final condition.

## 4.6.2 Example

20

We show here how to generate a Power litmus test from a given cycle of candidate relaxations by an example. We write  $_{-}$  for the information not yet set by diy:  $_{--}$  is an undetermined event,  $W_{--}$  a write with as-yet unset location and value, and  $Rx_{-}$  a read from x with undetermined value.

1. Consider e.g. the input cycle, issued by diy's cycles generation phase, with the input being the configuration file given in Fig. 10:

$$(a) \longrightarrow \xrightarrow{\text{Rfe}} (b) \longrightarrow \xrightarrow{\text{DpdR}} (c) \longrightarrow \xrightarrow{\text{Fre}} (d) \longrightarrow \xrightarrow{\text{Rfe}} (e) \longrightarrow \xrightarrow{\text{DpdR}} (f) \longrightarrow \xrightarrow{\text{Fre}} (a)$$

2. A linear scan sets the directions from the edges. Observe e.g. the last edge;  $\xrightarrow{\text{Fre}}$  requires a R source and a W target:

$$(a)W_{--} \xrightarrow{\text{Rfe}} (b)R_{--} \xrightarrow{\text{DpdR}} (c)R_{--} \xrightarrow{\text{Fre}} (d)W_{--} \xrightarrow{\text{Rfe}} (e)R_{--} \xrightarrow{\text{DpdR}} (f)R_{--} \xrightarrow{\text{Fre}} (a)$$

3. As  $\stackrel{\text{DpdR}}{\longrightarrow}$  specifies a location change, we pick (c) to be the first event and rewrite the cycle as:

$$(c)R_- \overset{\operatorname{Fre}}{\longrightarrow} (d)W_- \overset{\operatorname{Rfe}}{\longrightarrow} (e)R_- \overset{\operatorname{DpdR}}{\longrightarrow} (f)R_- \overset{\operatorname{Fre}}{\longrightarrow} (a)W_- \overset{\operatorname{Rfe}}{\longrightarrow} (b)R_- \overset{\operatorname{DpdR}}{\longrightarrow} (c)$$

We set the locations starting from (c), with a change of location e.g. between (e) and (f) since  $\stackrel{\text{DpdR}}{\longrightarrow}$  specifies a location change:

$$(c)Rx_{-} \xrightarrow{\operatorname{Fre}} (d)Wx_{-} \xrightarrow{\operatorname{Rfe}} (e)Rx_{-} \xrightarrow{\operatorname{DpdR}} (f)Ry_{-} \xrightarrow{\operatorname{Fre}} (a)Wy_{-} \xrightarrow{\operatorname{Rfe}} (b)Ry_{-} \xrightarrow{\operatorname{DpdR}} (c)$$

4. We cut the input cycle into maximal sequences of events with the same location  $(i.e.\ (c)(d)(e)$  and (f)(a)(b), each being scanned w.r.t. the cycle order. The values then reflect the write serialisation order for the specified location:

$$(c)Rx_{-} \xrightarrow{\operatorname{Fre}} (d)Wx1 \xrightarrow{\operatorname{Rfe}} (e)Rx_{-} \xrightarrow{\operatorname{DpdR}} (f)Ry_{-} \xrightarrow{\operatorname{Fre}} (a)Wy1 \xrightarrow{\operatorname{Rfe}} (b)Ry_{-} \xrightarrow{\operatorname{DpdR}} (c)$$

- 5. All the reads are significant here; we set their values according to step 5:  $(c)Rx0 \xrightarrow{\operatorname{Fre}} (d)Wx1 \xrightarrow{\operatorname{Rfe}} (e)Rx1 \xrightarrow{\operatorname{DpdR}} (f)Ry0 \xrightarrow{\operatorname{Fre}} (a)Wy1 \xrightarrow{\operatorname{Rfe}} (b)Ry1 \xrightarrow{\operatorname{DpdR}} (c)$

- 6. We generate the litmus test given in Fig. 11 for Power according to the steps 6 and 7 given in Sec. 4.6.1. For example on P<sub>0</sub>, we add a xor instruction between the instructions lwz r1,0(r2) and lwzx r4,r3,r5 associated with the events (b) and (c) to implement the dependency required by the → relation between them. The events (d) and (e), associated respectively to stw r1,0(r2) on P<sub>1</sub> and lwz r1,0(r2) on P<sub>2</sub>, are specified in the cycle to be in → Hence, we specify in the final state that the register r1 on P<sub>2</sub> holds finally 1. Indeed the store associated with (d) writes 1 into the address x addressed by r2 on P<sub>1</sub>, since the contents of the register r1 on P<sub>1</sub> is 1 (because of the preceding li r1, 1 instruction). Since (d) → (e), the load associated with (e) on P<sub>2</sub> reads the value 1 from the address x addressed by r2, and writes 1 into the register r2.

The test in Fig. 11 is a Power implementation of **iriw** [14] with dependencies. It can be obtained by running diy on the configuration file given in Fig. 10.

# 4.7 Coverage

Given a test generation tool such as diy, one should ask in what sense it provides good coverage and whether it generates useful tests.

One way to assess coverage is to check that it can generate 'classical' litmus tests in the literature. We just explained how one can generate the **iriw**

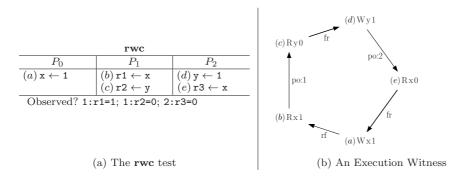

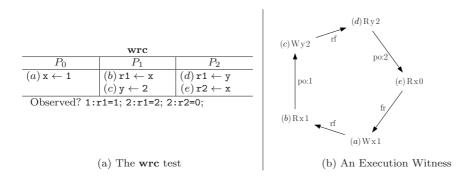

Fig. 13 The rwc Test and a Candidate Execution

Fig. 14 The wrc Test and a Candidate Execution

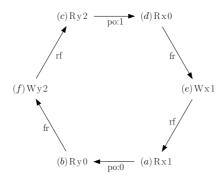

from [14]. The **rwc** test of [14], given in Fig. 13(a) can be obtained from the cycle  $\xrightarrow{\text{Rfe}}$ ;  $\xrightarrow{\text{PodRR}}$ ;  $\xrightarrow{\text{Fre}}$ ;  $\xrightarrow{\text{PodWR}}$ ;  $\xrightarrow{\text{Fre}}$ , as one can deduce from the execution given in Fig. 13(b). The **wrc** test of [14], given in Fig. 14(a) can be obtained from the cycle  $\xrightarrow{\text{Rfe}}$ ;  $\xrightarrow{\text{PodRW}}$ ;  $\xrightarrow{\text{Rfe}}$ ;  $\xrightarrow{\text{PodRR}}$ ;  $\xrightarrow{\text{Fre}}$ , as shown by the execution of Fig. 14(b).

Further, it generates all the variations of such tests with different choices of barriers and dependencies (e.g. 56 variations of **wrc**), and several families of tests that we have not previously seen. There are some interesting classes of tests that it does not generate, *e.g.* tests exhibiting observable register shadowing [3], where we still rely on hand-written tests.

In general, diy will be able to generate any classical litmus test, as soon as this test can be generated from a cycle of candidate relaxations as defined in Sec. 4.2, and is not subject to the restrictions described in Sec. 4.5.

Comparing directly with the tests used within processor vendors is difficult, as those are commercially sensitive. However, the fact that we have found issues in deployed processors (as detailed in Sec. 5) is indicative.

Another sense in which it is demonstrably useful (indeed, indispensable) in practice has been in our model-building work, as illustrated for example in Sec. 6.2. Our initial explorations relied on several hundred hand-written tests, and it was hard to maintain consistency and ensure coverage of these. Using diy, while we still use some hand-written tests, most of our work can be done with automatically

| Relaxation  | Definition                                                                                 | hpcx        | squale    | vargas      |

|-------------|--------------------------------------------------------------------------------------------|-------------|-----------|-------------|

| PosRR       | $r_\ell \stackrel{\mathrm{po}}{\to} r'_\ell$                                               | 2/40M       | 3/2M      | 0/4745M     |

| PodRR       | $r_\ell \stackrel{\text{po}}{\to} r'_{\ell'}$                                              | 2275/320M   | 12/2M     | 0/16725M    |

| PodRW       | $r_\ell \stackrel{\mathrm{po}}{\to} w'_{\ell'}$                                            | 0/6000M     | 0/6000M   | 0/6000M     |

| PodWW       | $w_\ell \stackrel{\mathrm{po}}{\to} w'_{\ell'}$                                            | 2029/4M     | 2299/2M   | 2092501/32M |

| PodWR       | $w_\ell \stackrel{\text{po}}{\to} r'_{\ell'}$                                              | 51085/40M   | 178286/2M | 672001/32M  |

| Rfi         | $\stackrel{\mathrm{rfi}}{\to}$                                                             | 7286/4M     | 1133/2M   | 145/32M     |

| Rfe         | $\stackrel{\mathrm{rfe}}{\rightarrow}$                                                     | 177/400M    | 0/1776M   | 9/32M       |

| LwSyncsWR   | $w_\ell \stackrel{\mathrm{lwsync}}{\to} r'_\ell$                                           | 243423/600M | 2/40M     | 385/32M     |

| LwSyncdWR   | $w_\ell \stackrel{\mathrm{lwsync}}{\to} r'_{\ell'}$                                        | 103814/640M | 11/2M     | 117670/32M  |

| ACLwSyncsRR | $w_\ell \stackrel{\text{rfe}}{\to} r'_\ell \stackrel{\text{lwsync}}{\to} r''_\ell$         | 11/320M     | 0/960M    | 1/21M       |

| ACLwSyncdRR | $w_\ell \stackrel{\mathrm{rfe}}{\to} r'_\ell \stackrel{\mathrm{lwsync}}{\to} r''_{\ell'}$  | 124/400M    | 0/7665M   | 2/21M       |

| BCLwSyncsWW | $w_\ell \stackrel{\text{lwsync}}{\to} w'_\ell \stackrel{\text{rfe}}{\to} r''_\ell$         | 68/400M     | 0/560M    | 2/160M      |

| BCLwSyncdWW | $w_{\ell} \stackrel{\text{lwsync}}{\to} w'_{\ell'} \stackrel{\text{rfe}}{\to} r''_{\ell'}$ | 158/400M    | 0/11715M  | 1/21M       |

Fig. 15 Selected Results of the diy Experiment Matching Our Model

generated tests. In addition, as we explain in our more recent work on modelling the behaviour of Power multiprocessors [27], some key issues of the model were identified with these automatically generated tests.

## 5 Using diy: The Phat Experiment

We ran a case study for the diy tool, the Phat Experiment, from December 2009 to January 2010. We tested three Power machines, and present here a summary of the experimental results. More details can be found online at http://diy.inria.fr/phat.

# 5.1 Relaxations Observed on squale, vargas and hpcx

We used diy to generate 800 Power tests and run them up to  $10^{12}$  times each on three machines: squale, a 4-processor Power G5 running Mac OS X; hpcx, a Power 5 with 16 processors per node and vargas, a Power 6 with 32 processors per node, both of them running AIX.

We ran the tests supposed to exhibit relaxations, *i.e.* the tests targeting any possible relation of Fig. 9 that our CAV 2010 model (see Fig. 22) does not include in  $\stackrel{\mathrm{ghb}}{\rightarrow}$ . We observed all of them at least on one machine, except PodRW. Not observing a given candidate relaxation does not contradict our model, since our model should authorise at least all the behaviours that we observed on hardware. We give in Fig. 15 the number of times the outcome was observed (where M stands for million). For each relaxation observed on a given machine, we write the highest number of outcomes. When a candidate relaxation was not observed, we write the total of outcomes: thus we write  $e.g.~0/16725\mathrm{M}$  for PodRR on vargas.

For a given candidate relaxation, we generated tests with diy by writing a simple configuration file setting its relax list to this candidate relaxation, and some of the candidate relaxations that we considered to be safe.

| Cycle                                     | hpcx   | In [14] |

|-------------------------------------------|--------|---------|

| Rfe SyncdRR Fre Rfe SyncdRR Fre           | 2/320M | iriw    |

| Rfe SyncdRR Fre SyncdWR Fre               | 3/400M | rwc     |

| DpdR Fre Rfe SyncsRR DpdR Fre Rfe SyncsRR | 1/320M |         |

| Wse LwSyncdWW Wse Rfe SyncdRW             | 1/800M |         |

| Wse SyncdWR Fre Rfe LwSyncdRW             | 1/400M |         |

Fig. 16 Anomalies Observed on Power 5

We did not observe the PodRW relaxation; but the documentation does not specify this candidate relaxation to be safe, therefore we still consider it to be relaxed.

#### 5.2 Safe Relaxations

Following our informal model, we assumed that the candidate relaxations corresponding to  $\xrightarrow{\text{ws}}$ ,  $\xrightarrow{\text{fr}}$ , dependencies and barriers were global and tested this assumption by computing *safe* tests in which the input cycles only include candidate relaxations that we supposed global, *e.g.*  $\xrightarrow{\text{SyncdWW}}$ ;  $\xrightarrow{\text{Wse}}$ ;  $\xrightarrow{\text{SyncdWR}}$ ;  $\xrightarrow{\text{Fre}}$ .

For each machine, we observed the number of runs required to exhibit the least frequent relaxation (e.g. 160M for BCLwSyncsWW on vargas), and ran the safe tests at least 20 times this number. The outcomes of the safe tests have not been observed on vargas and squale, which increases our confidence in the safe set we assumed.

However, hpcx does exhibit non-SC behaviours for some A-cumulativity tests (albeit rarely), including classical tests [14] such as **iriw** with **sync** instructions on  $P_0$  and  $P_1$ . These results are in contradiction with our model. We summarise these contradictions in Fig. 16.

We understand that this is due to a rare erratum in the Power 5 implementation. IBM is providing a software workaround, replacing the sync barrier by a short code sequence [Personal Communication], and our testing suggests that this does regain SC behaviour for the examples in question (e.g. with 0/4e10 non-SC results for iriw). We understand also that Power 6 is not subject to the erratum, which is consistent with our testing on vargas, and that it should not affect the correctness of code using conventional lock primitives.

## 6 The CAV 2010 Axiomatic Power Model

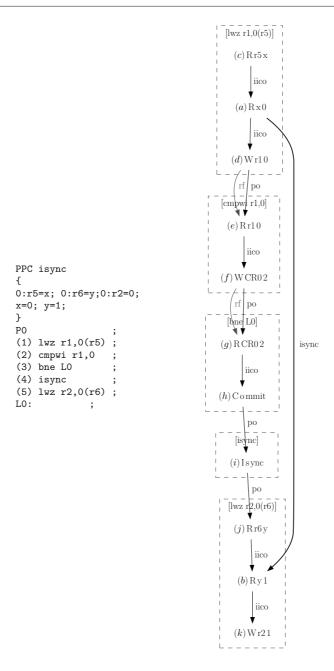

In the light of the black-box experimental testing described in Sec. 5, we have instantiated the formalism of Sec. 2 for Power. The resulting model (which we refer to as the  $CAV\ 2010$  model) captures several important aspects of the processor's behaviour:

it describes the lack of store atomicity on Power, despite being in the simple global-time style of our framework rather than the per-processor- timeline style implied by the architecture text;

| Name                              | Notation                                | Comment                                                                                                                                                                                                                                                                               | Sec.  |

|-----------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| intra instruction causality order | $m_1 \stackrel{\mathrm{lico}}{\to} m_2$ | constraints arising from instruction semantics                                                                                                                                                                                                                                        | 6.1.1 |

| register read-from map            | $w \stackrel{\text{rf-reg}}{\to} r$     | links a register write to a register read reading its value                                                                                                                                                                                                                           | 6.1.1 |

| data dependency                   | $m_1 \stackrel{\mathrm{dd}}{\to} m_2$   | $(m_1, m_2) \in (\overset{\text{rf-reg}}{\to} \cup \overset{\text{iico}}{\to})^+$                                                                                                                                                                                                     | 6.2.1 |

| control dependency                | $r \stackrel{\text{ctrl}}{\to} w$       | read-write pair separated by a branch                                                                                                                                                                                                                                                 | 6.2.1 |

| isync dependency                  | $r \stackrel{\text{isync}}{\to} m$      | read-read or read-write pair separated<br>by a branch+isync sequence                                                                                                                                                                                                                  | 6.2.1 |

| dependency                        | $m_1 \stackrel{\mathrm{dp}}{\to} m_2$   | $(m_1, m_2)$ $\in \stackrel{\operatorname{ctrl}}{\to}$ $\cup$ $\stackrel{\operatorname{isync}}{\to}$                                                                                                                                                                                  | 6.2.1 |

|                                   |                                         | $ \begin{array}{c} \cup \left( \left( \overset{\mathrm{dd}}{\rightarrow} \cup \left( \overset{\mathrm{po-loc}}{\rightarrow} \cap \left( \mathbb{W} \times \mathbb{R} \right) \right) \right)^{+} \cap \left( \mathbb{R} \times \mathbb{R} \right) \\ \mathbb{M} \right) \end{array} $ |       |

| sync                              | $m_1 \stackrel{\text{sync}}{\to} m_2$   | pairs maintained by sync                                                                                                                                                                                                                                                              | 6.2.3 |

| lwsync                            | $m_1 \stackrel{\text{lwsync}}{\to} m_2$ | pairs maintained by lwsync                                                                                                                                                                                                                                                            | 6.2.3 |

Fig. 17 Table of Power specific relations

- it also models the thread-local ordering relaxations we observe; and

- it models A-cumulative barriers [25].