## Predicate-aware, makespan-preserving software pipelining of scheduling tables

Thomas Carle, Dumitru Potop-Butucaru

### ▶ To cite this version:

Thomas Carle, Dumitru Potop-Butucaru. Predicate-aware, makespan-preserving software pipelining of scheduling tables. ACM Transactions on Architecture and Code Optimization, 2014, 11, pp.1 - 26. 10.1145/2579676 . hal-01095123

### HAL Id: hal-01095123 https://inria.hal.science/hal-01095123

Submitted on 18 Dec 2014

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Predicate-aware, makespan-preserving software pipelining of scheduling tables<sup>1</sup>

Thomas Carle, INRIA Paris-Rocquencourt Dumitru Potop-Butucaru, INRIA Paris-Rocquencourt

We propose a software pipelining technique adapted to specific hard real-time scheduling problems. Our technique optimizes both computation throughput and execution cycle makespan, with makespan being prioritary. It also takes advantage of the predicated execution mechanisms of our embedded execution platform. To do so, it uses a reservation table formalism allowing the manipulation of the execution conditions of operations. Our reservation tables allow the double reservation of a resource at the same dates by two different operations, if the operations have exclusive execution conditions. Our analyses can determine when double reservation is possible even for operations belonging to different iterations.

#### 1. INTRODUCTION

In this paper, we take inspiration from a classical compilation technique, namely software pipelining, in order to improve the system-level task scheduling of a specific class of embedded systems.

Software pipelining. Compilers are expected to improve code speed by taking advantage of micro-architectural instruction level parallelism [Hennessy and Patterson 2007]. Pipelining compilers usually rely on reservation tables to represent an efficient (possibly optimal) static allocation of the computing resources (execution units and/or registers) with a timing precision equal to that of the hardware clock. Executable code is then generated that enforces this allocation, possibly with some timing flexibility. But on VLIW architectures, where each instruction word may start several operations, this flexibility is very limited, and generated code is virtually identical to the reservation table. The scheduling burden is mostly supported here by the compilers, which include software pipelining techniques [Rau and Glaeser 1981; Allan et al. 1995] designed to increase the throughput of loops by allowing one loop cycle to start before the completion of the previous one.

Static (offline) real-time scheduling. A very similar picture can be seen in the system-level design of safety-critical real-time embedded control systems with distributed (parallel, multicore) hardware platforms. The timing precision is here coarser, both for starting dates, which are typically given by timers, and for durations, which are characterized with worst-case execution times (WCET). However, safety and efficiency arguments[Fohler et al. 2008] lead to the increasing use of tightly synchronized time-triggered architectures and execution mechanisms, defined in well-established standards such as TTA, FlexRay[Rushby 2001], ARINC653[ARINC653], or AUTOSAR[AUTOSAR]. Systems based on these platforms typically have hard real-time constraints, and their correct functioning must be guaranteed by a schedulability analysis. In this paper, we are interested in statically scheduled systems where resource allocation can be described under the form of a reservation/scheduling table which constitutes, by itself, a proof of schedulability. Such systems include:

- Periodic time-triggered systems [Caspi et al. 2003; Zheng et al. 2005; Monot et al. 2010; Eles et al. 2000; Potop-Butucaru et al. 2010] that are naturally mapped over ARINC653, AUTOSAR, TTA, or FlexRay.

- Systems where the scheduling table describes the reaction to some sporadic input event (meaning that the table must fit inside the period of the sporadic event). Such systems

<sup>&</sup>lt;sup>1</sup>This work was partially funded by the FUI PARSEC project. Preliminary results of this work are also available online as the Chalmers' master thesis of the first author http://publications.lib.chalmers.se/records/fulltext/146444.pdf.

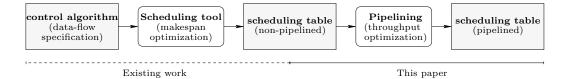

Fig. 1. Proposed pipelined scheduling flow

can be specified in AUTOSAR, allowing, for instance, the modeling of computations synchronized with engine rotation events [André et al. 2007].

- Some systems with a mixed event-driven/time-driven execution model, such as those synthesized by SynDEx[Grandpierre and Sorel 2003].

Synthesis of such systems starts from specifications written in domain-specific formalisms such as Simulink or SCADE[Caspi et al. 2003]. These formalisms allow the description of concurrent data computations and communications that are *conditionally activated* at each cycle of the embedded control algorithm depending on the current *input* and *state* of the system.

The problem. The optimal scheduling of such specifications onto platforms with multiple, heterogenous execution and communication resources (distributed, parallel, multi-core) is NP-hard regardless of the optimality criterion (throughput, makespan, etc.) [Garey and Johnson 1979]. Existing scheduling techniques and tools [Caspi et al. 2003; Zheng et al. 2005; Grandpierre and Sorel 2003; Potop-Butucaru et al. 2010; Eles et al. 2000] heuristically solve the simpler problem of synthesizing a scheduling table of minimal length which implements one generic cycle of the embedded control algorithm. In a hard real-time context, minimizing table length (*i.e.* the makespan, as defined in the glossary of Fig. 2) is often a good idea, because in many applications it bounds the response time after a stimulus.

But optimizing makespan alone relies on an execution model where execution cycles cannot overlap in time (no pipelining is possible), even if resource availability allows it. At the same time, most real-time applications have both makespan and throughput requirements, and in some cases achieving the required throughput is only possible if a new execution cycle is started before the previous one has completed.

This is the case in the electronic control units (ECU) of combustion engines. Starting from the acquisition of data for a cylinder in one engine cycle, an ECU must compute the ignition parameters before the ignition point of the same cylinder in the next engine cycle (a makespan constraint). It must also initiate one such computation for each cylinder in each engine cycle (a throughput constraint). On modern multiprocessor ECUs, meeting both constraints requires the use of pipelining[André et al. 2007]. Another example is that of systems where a faster rate of sensor data acquisition results in better precision and improved control, but optimizing this rate must not lead to the non-respect of requirements on the latency between sensor acquisition and actuation. To allow the scheduling of such systems we consider here the static scheduling problem of optimizing both makespan and throughput, with makespan being prioritary.

*Contribution.* To (heuristically) solve this optimization problem, we use a two-phase scheduling flow that can be seen as a form of *decomposed software pipelining* [Wang and Eisenbeis 1993; Gasperoni and Schwiegelshohn 1994; Calland et al. 1998]. As pictured in Fig. 1, the first phase of this flow consists in applying one of the previously-mentioned makespan-optimizing tools. The result is a scheduling table describing the execution of one generic execution cycle of the embedded control algorithm with no pipelining.

The second phase uses a novel software pipelining algorithm, introduced in this paper, to significantly improve the throughput without changing the makespan and while preserv-

| Concept                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| scheduling table                           | These are essentially modulo reservation tables [Lam 1988], ex-<br>tended to allow the representation of conditional/multiple reser-<br>vations. We use a different name to identify our specific internal<br>formalism where reservations are the complex scheduled opera-<br>tions defined below.                                                                                                                                                                                                                                                                                                                              |

| initiation interval                        | The length of a schedule table is also called its initiation interval (II).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| execution cycle                            | One iteration of either a scheduling table or the control algorithm before scheduling.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| non-pipelined vs.<br>pipelined<br>makespan | In classical software pipelining, reservation tables are used to represent the pipelined schedule. In our case, a reservation table is also used to represent the input of the pipelining algorithm. To avoid ambiguity, uses of "scheduling table", "initiation interval", "throughput", <i>etc.</i> will be qualified with "non-pipelined" or "pipelined" whenever necessary. For instance, the pipelined scheduling table is usually known in software pipelining as the <i>kernel.</i><br>Worst-case duration of one execution cycle of the control algorithm, from the start of its first operation, to the end of its last |

|                                            | operation. In our approach, by construction, it is the same in both<br>the non-pipelined and pipelined scheduling tables. It is equal to<br>the initiation interval of the non-pipelined scheduling table.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| throughput                                 | The number of execution cycles of the control algorithm executed<br>per time unit. It is defined as the inverse of the initiation interval.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| inter-cycle depen-                         | Data dependencies between operations of different execution cy-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| dency<br>scheduled opera-<br>tion          | cles of the non-pipelined scheduling table.<br>Complex data structure defining a resource reservation in a<br>scheduling table (a time interval on one or several resources), but<br>providing at the same time information on the operation (real-<br>time task) to be executed inside this reservation (input and output<br>variables, execution condition).                                                                                                                                                                                                                                                                   |

Fig. 2. Glossary of terms used in this paper. All notions are formally defined later

ing the *periodic* nature of the system. The approach has the advantage of simplicity and generality, allowing the use of existing makespan-optimizing tools.

The proposed software pipelining algorithm is a very specific and constrained form of *modulo scheduling* [Rau 1996]. Like all modulo scheduling algorithms, it determines a shorter *initiation interval* for the execution cycles (iterations) of the control algorithm, subject to resource and inter-cycle data dependency constraints. Unlike previous modulo scheduling algorithms, however, it starts from an already scheduled code (the non-pipelined scheduling table), and preserves all the intra-cycle scheduling decisions made at phase 1, in order to preserve the makespan unchanged. In other words, our algorithm computes the best *initiation interval* for the non-pipelined scheduling table and re-organizes resource reservations into a *pipelined scheduling table*, whose length is equal to the new initiation interval, and which accounts for the changes in memory allocation.

We have implemented our algorithm into a pipelining tool that is used, as we desired, in conjunction with an existing makespan-optimizing scheduling tool. The resulting two-phase flow gives good results on architectures without temporal partitioning [ARINC653], like the previously-mentioned AUTOSAR or SynDEx-generated applications and, to a certain extent, applications using the FlexRay dynamic segment.

For applications mapped onto partitioned architectures (ARINC 653, TTA, or FlexRay, the static segment) or where the non-functional specification includes multiple release date, end-to-end latency, or periodicity constraints, separating the implementation process in two phases (scheduling followed by pipelining) is not a good idea. We therefore developed a single-phase pipelined scheduling technique documented elsewhere [Carle et al. 2012], but which uses (with good results) the same internal representation based on scheduling tables to allow a simple mapping of applications with execution modes onto heterogenous architectures with multiple processors and buses.

#### Outline

The remainder of the paper is structured as follows. Section 2 reviews related work. Section 3 formally defines scheduling tables. Sections 4 and 5 present the pipelining technique and provide and provide a complex example. Section 5 deals with data dependency analysis. Section 6 gives experimental results, and Section 7 concludes.

#### 2. RELATED WORK AND ORIGINALITY

This section reviews related work and details the originality points of our paper. Performing this comparison required us to relate concepts and techniques belonging to two fields: software pipelining and real-time scheduling. To avoid ambiguities when the same notion has different names depending on the field, we define in Fig. 2 a glossary of terms that will be used throughout the paper.

#### 2.1. Decomposed software pipelining.

Closest to our work are previous results on *decomposed software pipelining* [Wang and Eisenbeis 1993; Gasperoni and Schwiegelshohn 1994; Calland et al. 1998]. In these papers, the software pipelining of a sequential loop is realized using two-phase heuristic approaches with good practical results. Two main approaches are proposed in these papers.

In the first approach, used in all 3 cited papers, the first phase consists in solving the loop scheduling problem while ignoring resource constraints. As noted in [Calland et al. 1998], existing decomposed software pipelining approaches solve this loop scheduling problem by using *retiming* algorithms. Retiming [Leiserson and Saxe 1991] can therefore be seen as a very specialized form of pipelining targeted at cyclic (synchronous) systems where each operation has its own execution unit. Retiming has significant restrictions when compared with full-fledged software pipelining:

- It is oblivious of resource allocation. As a side-effect, it cannot take into account execution conditions to improve allocation, being defined in a purely data-flow context.

- It requires that the execution cycles of the system do not overlap in time, so that one operation must be completely executed inside the cycle where it was started.

Retiming can only change the execution order of the operations inside an execution cycle. A typical retiming transformation is to move one operation from the end to the beginning of the execution cycle in order to shorten the duration (critical path) of the execution cycle, and thus improve system throughput. The transformation cannot decrease the makespan but may increase it.

Once retiming is done, the second transformation phase takes into account resource constraints. To do so, it considers the acyclic code of one generic execution cycle (after retiming). A list scheduling technique ignoring inter-cycle dependences is used to map this acyclic code (which is actually represented with a *directed acyclic graph*, or DAG) over the available resources.

The second technique for decomposed software pipelining, presented in [Wang and Eisenbeis 1993], basically switches the two phases presented above. Resource constraints are considered here in the first phase, through the same technique used above: list scheduling of

DAGs. The DAG used as input is obtained from the cyclic loop specification by preserving only some of the data dependences. This scheduling phase decides the resource allocation and the operation order inside an execution cycle. The second phase takes into account the data dependences that were discarded in the first phase. It basically determines the fastest way a specification-level execution cycle can be executed by several successive pipelined execution cycles without changing the operation scheduling determined in phase 1 (preserving the throughput unchanged). Minimizing the makespan is important here because it results in a minimization of the memory/register use.

#### 2.2. Originality.

In this paper, we propose a third decomposed software pipelining technique with two significant originality points, detailed below.

2.2.1. Optimization of both makespan and throughput. Existing software pipelining techniques are tailored for optimizing only one real-time performance metric: the processing throughput of loops [Yun et al. 2003] (sometimes besides other criteria such as register usage [Govindarajan et al. 1994; Zalamea et al. 2004; Huff 1993] or code size [Zhuge et al. 2002]). In addition to throughput, we also seek to optimize makespan, with makespan being prioritary. Recall that throughput and latency (makespan) are antagonistic optimization objectives during scheduling [Benoît et al. 2007], meaning that resulting schedules can be quite different (an example will be provided in Section 4.1.2).

To optimize makespan we employ in the first phase of our approach existing scheduling techniques that were specifically designed for this purpose [Caspi et al. 2003; Zheng et al. 2005; Grandpierre and Sorel 2003; Potop-Butucaru et al. 2010; Eles et al. 2000]. But the main contribution of this paper concerns the second phase of our flow, which takes the scheduling table computed in phase 1 and optimizes its throughput while keeping its makespan unchanged. This is done using a new algorithm that conserves all the allocation and intra-cycle scheduling choices made in phase 1 (thus conserving makespan guarantees), but allowing the optimization of the throughput by increasing (if possible) the frequency with which execution cycles are started.

Like retiming, this transformation is a very restricted form of modulo scheduling software pipelining. In our case, it can only change the initiation interval (changes in memory allocation and in the scheduling table are only consequences). By comparison, classical software pipelining algorithms, such as the iterative modulo scheduling of [Rau 1996], perform a full mapping of the code involving both execution unit allocation and scheduling. Our choice of transformation is motivated by three factors:

- It preserves makespan guarantees.

- It gives good practical results for throughput optimization.

- It has low complexity.

It is important to note that our transformation is not a form of retiming. Indeed, it allows for a given operation to span over several cycles of the pipelined implementation, and it can take advantage of conditional execution to improve pipelining, whereas retiming techniques work in a pure data-flow context, without predication (an example will be provided in Section 4.1.2).

2.2.2. Predication. For an efficient mapping of our conditional specifications, it is important to allow an independent, predicated (conditional) control of the various computing resources. However, most existing techniques for software pipelining [Allan et al. 1995; Warter et al. 1993; Yun et al. 2003] use hardware models that significantly constrain or simply prohibit predicated resource control. This is due to limitations in the target hardware itself. One common problem is that two different operations cannot be scheduled at the same date on a given resource (functional unit), even if they have exclusive predicates (like the branches

of a test). The only exception we know to this rule is *predicate-aware scheduling (PAS)* [Smelyanskyi et al. 2003].

By comparison, the computing resources of our target architectures are not a mere functional units of a CPU (as in classical predicated pipelining), but full-fledged processors such as PowerPC, ARM, *etc.* The operations executed by these computing resources are large sequential functions, and not simple CPU instructions. Thus, each computing resource allows unrestricted predication control by means of conditional instructions, and the timing overhead of predicated control is negligible with respect to the duration of the operations. This means that our architectures satisfy the PAS requirements. The drawback of PAS is that sharing the same resource at the same date is only possible for operations of the same cycle, due to limitations in the dependency analysis phase. Our technique removes this limitation (an example will be provided in Section 4.1.3).

To exploit the full predicated control of our platform we rely on a new intermediate representation, namely *predicated and pipelined scheduling tables*. By comparison to the modulo reservation tables of [Lam 1988; Rau 1996], our scheduling tables allow the explicit representation of the execution conditions (predicates) of the operations. In turn, this allows the double reservation of a given resource by two operations with exclusive predicates.

#### 2.3. Other aspects

A significant amount of work exists on applying software pipelining or retiming techniques for the efficient scheduling of tasks onto coarser-grain architectures, such as multi-processors [Kim et al. 2012; Yang and Ha 2009; Chatha and Vemuri 2002; Chiu et al. 2011; Caspi et al. 2003; Morel 2005]. To our best knowledge, these results share the two fundamental limitations of other software pipelining algorithms: Optimizing for only one real-time metric (throughput) and not fully taking advantage of conditional execution to allow double allocation of resources.

Minor originality points of our technique, concerning code generation and dependency analysis will be discussed and compared with previous work in Sections 4.4 and 5.

#### 3. SCHEDULING TABLES

This section defines the formalism used to represent the non-pipelined static schedules produced by phase 1 of our scheduling flow and taken as input by phase 2. Inspired from [Potop-Butucaru et al. 2010; Grandpierre and Sorel 2003], our scheduling table formalism remains at a significantly lower abstraction level. The models of [Potop-Butucaru et al. 2010; Grandpierre and Sorel 2003] are fully synchronous: Each variable has at most one value at each execution cycle, and moving one value from a cycle to the next can only be done through explicit *delay* constructs. In our model, each variable (called a memory cell) can be assigned several times during a cycle, and values are by default passed from one execution cycle to the next.

The lower abstraction level means that time-triggered executable code generated by *any* of the previously-mentioned scheduling tools can directly be used as input for the pipelining phase. Integration between the scheduling tools and the pipelining algorithm defined next is thus facilitated. The downside is that the pipelining technique is more complex, as detailed in Section 4.4.2.

#### 3.1. Architecture model

We model our multi-processor (distributed, parallel) execution architectures using a very simple language defining sequential execution resources, memory blocks, and their interconnections. Formally, an architecture model is a bipartite undirected graph  $\mathcal{A} = \langle \mathcal{P}, \mathcal{M}, \mathcal{C} \rangle$ , with  $\mathcal{C} \subseteq \mathcal{P} \times \mathcal{M}$ . The elements of  $\mathcal{P}$  are called *processors*, but they model all the computation and communication devices capable of independent execution (CPU cores, accelerators, DMA and bus controllers, etc.). We assume that each processor can execute only one oper-

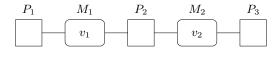

Fig. 3. Simple architecture

ation at a time. We also assume that each processor has its own sequential or time-triggered program. This last assumption is natural on actual CPU cores. On devices such as DMAs and accelerators, it models the assumption that the cost of control by some other processor is negligible.<sup>2</sup>

The elements of  $\mathcal{M}$  are RAM blocks. We assume each RAM block is structured as a set of disjoint *cells*. We denote with *Cells* the set of all memory cells in the system, and with *Cells*<sub>M</sub> the set of cells on RAM block  $\mathcal{M}$ . Our model does not explicitly specify memory size limits. To limit memory usage in the pipelined code we rely instead on the mechanism detailed in Section 4.4.3.

The elements of  $\mathcal{C}$  are the interconnections. Processor P has direct access to memory block M whenever  $(P, M) \in \mathcal{C}$ . All processors directly connected to a memory block M can access M at the same time. Therefore, care must be taken to prohibit concurrent read-write or write-write access by two or more processors to a single memory cell, in order to preserve functional determinism (we will assume this is ensured by the input scheduling table, and will be preserved by the pipelined one).

The simple architecture of Fig. 3 has 3 processors  $(P_1, P_2, \text{ and } P_3)$  and 2 memory blocks  $(M_1 \text{ and } M_2)$ . Each of the  $M_i$  blocks has only one memory cell  $v_i$ .

#### 3.2. Scheduling tables

On such architectures, Phase 1 scheduling algorithms perform static (offline) allocation and scheduling of embedded control applications under a *periodic* execution model. The result is represented with scheduling tables, which are finite time-triggered activation patterns. This pattern defines the computation of one period (also called execution cycle) of the control algorithm. The infinite execution of the embedded system is the infinite succession of periodically-triggered execution cycles. Execution cycles do not overlap in time (there is no pipelining).

Formally, a scheduling table is a triple  $S = \langle p, O, Init \rangle$ , where p is the activation period of execution cycles, O is the set of scheduled operations, and Init is the initial state of the memory.

The activation period gives the (fixed) duration of the execution cycles. All the operations of one execution cycle must be completed before the following execution cycle starts. The activation period thus sets the *length* of the scheduling table, and is denoted by len(S).

The set  $\mathcal{O}$  defines the operations of the scheduling table. Each scheduled operation  $o \in \mathcal{O}$  is a tuple defining:

- $-In(o) \subseteq Cells$  is the set of memory cells read by o.

- $-Out(o) \subseteq Cells$  is the set of cells written by o.

- Guard(o) is the execution condition of o, defined as a predicate over the values of memory cells.

- We denote with GuardIn(o) the set of memory cells used in the computation of Guard(o). There is no relation between GuardIn(o) and In(o).

- $-Res(o) \subseteq \mathcal{P}$  is the set of processors used during the execution of o.

- -t(o) is the start date of o.

$<sup>^2\</sup>mathrm{This}$  assumption is common for coarse-grain real-time applications.

ACM Journal Name, Vol. V, No. N, Article A, Publication date: January YYYY.

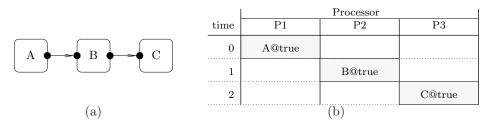

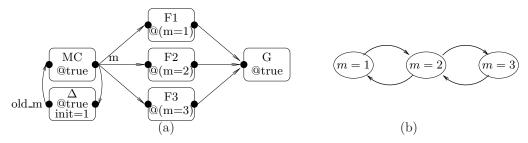

Fig. 4. Simple dataflow specification (a) and (non-pipelined) scheduling table for this specification (b)

-d(o) is the duration of o. The duration is viewed here as a time budget the operation must not exceed. This can be statically ensured through a worst-case execution time analysis.

All the resources of Res(o) are exclusively used by o after t(o) and for a duration of d(o) in cycles where Guard(o) is true. The sets In(o) and Out(o) are not necessarily disjoint, to model variables that are both read and updated by an operation. For lifetime analysis purposes, we assume that input and output cells are used for all the duration of the operation. The cells of GuardIn(o) are all read at the beginning of the operation, but we assume the duration of the computation of the guard is negligible (zero time).<sup>3</sup>

To cover cases where a memory cell is used by one operation before being updated by another, each memory cell can have an *initial value*. For a memory cell m, Init(m) is either *nil*, or some constant.

3.2.1. A simple example. To exemplify, we consider the simple data-flow synchronous specification of Fig. 4(a), which we map onto the architecture of Fig. 3. Depending on the non-functional requirements given as input to the scheduling tool of Phase 1 (allocation constraints, WCETs, *etc.*) one possible result is the scheduling table pictured in Fig. 4. We assumed here that A is must be mapped onto  $P_1$  (*e.g.* because it uses a sensor peripheral connected to  $P_1$ ), that B must be mapped onto  $P_2$ , that C must be mapped onto  $P_3$  and that A, B, and C have all duration 1.

This table has a length of 3 and contains the 3 operations of the data-flow specification (A, B, and C). Operation A reads no memory cell, but writes  $v_1$ , so that  $In(A) = \emptyset$  and  $Out(A) = \{v_1\}$ . Similarly,  $In(B) = \{v_1\}$ ,  $Out(B) = In(C) = \{v_2\}$ , and  $Out(C) = \emptyset$ . All 3 operations are executed at every cycle, so their guard is *true* (guards are graphically represented with "@true"). The 3 operations are each allocated on one processor:  $Res(A) = \{P_1\}$ ,  $Res(B) = \{P_2\}$ ,  $Res(C) = \{P_3\}$ . Finally, t(A) = 0, t(B) = 1, t(C) = 2, and d(A) = d(B) = d(C) = 1. No initialization of the memory cells is needed (the initial values are all *nil*).

#### 3.3. Well-formed properties

The formalism above provides the syntax of scheduling tables, and allows the definition of operational semantics. However, not all syntactically correct tables represent correct implementations. Some of them are non-deterministic due to data races or due to operations exceeding their time budgets. Others are simply un-implementable, for instance because an operation is scheduled on processor P, but accesses memory cells on a RAM block not connected to P. A set of correctness properties is therefore necessary to define the wellformed scheduling tables.

However, some of these properties are not important in this paper, because we assume that the input of our pipelining technique, synthesized by a scheduling tool, is already correct. For instance, we assume that all schedules are implementable, with data used by a

$<sup>^{3}</sup>$ The memory access model where an operation reads its inputs at start time, writes its outputs upon completion, and where guard computations take time can be represented on top of our model.

| $\operatorname{time}$ | P1                    | P2                    | P3                    |          |

|-----------------------|-----------------------|-----------------------|-----------------------|----------|

| 0                     | A@true<br>iteration 1 |                       |                       | Dualamua |

| 1                     | A@true<br>iteration 2 | B@true<br>iteration 1 |                       | Prologue |

| 2                     | A@true<br>iteration 3 | B@true<br>iteration 2 | C@true<br>iteration 1 | Steady   |

| 3                     | A@true<br>iteration 4 | B@true<br>iteration 3 | C@true<br>iteration 2 | state    |

|                       |                       |                       |                       |          |

Fig. 5. Pipelined execution trace for the example of Fig. 4

| time | P1                                                   | P2                                                           | P3                                                 |

|------|------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|

| 0    | $ \begin{array}{c} A@true\\ fst(A) = 0 \end{array} $ | $ \begin{array}{c} \text{B@true} \\ fst(B) = 1 \end{array} $ | $\begin{array}{c} C@true\\ fst(C) = 2 \end{array}$ |

Fig. 6. Pipelined scheduling table (kernel) for the example of Fig. 4

processor being allocated in adjacent memory banks. This is why we only formalize here two correctness properties that will need attention in the following sections because pipelining transformations can affect them.

We say that two operations  $o_1$  and  $o_2$  are *non-concurrent*, denoted  $o_1 \perp o_2$ , if either their executions do not overlap in time  $(t(o_1) + d(o_1) \leq t(o_2)$  or  $t(o_2) + d(o_2) \leq t(o_1)$ ), or if they have exclusive guards  $(Guard(o_1) \land Guard(o_2) = false)$ . With this notation, the following correctness properties are assumed respected by input (non-pipelined) scheduling tables, and must be respected by the output (pipelined) ones:

Sequential processors. No two operations can use a processor at the same time. Formally, for all  $o_1, o_2 \in \mathcal{O}$ , if  $Res(o_1) \cap Res(o_2) \neq \emptyset$  then  $o_1 \perp o_2$ .

No data races. If some memory cell m is written by  $o_1$  ( $m \in Out(o_1)$ ) and is used by  $o_2$  ( $m \in In(o_2) \cup Out(o_2)$ ), then  $o_1 \perp o_2$ .

#### 4. PIPELINING TECHNIQUE OVERVIEW

#### 4.1. Pipelined scheduling tables

4.1.1. A simple example. For the example in Fig. 4, an execution where successive cycles do not overlap in time is clearly sub-optimal. Our objective is to allow the pipelined execution of Fig. 5, which ensures a maximal use of the computing resources.

In the pipelined execution, a new instance of operation A starts as soon as the previous one has completed, and the same is true for B and C. The first two time units of the execution are the *prologue* which fills the pipeline. In the *steady state* the pipeline is full and has a throughput of one computation cycle (of the non-pipelined system) per time unit. If the system is allowed to terminate, then completion is realized by the *epilogue*, not pictured in our example, which empties the pipeline.

We represent the pipelined system schedule using the *pipelined scheduling table* pictured in Fig. 6. Its length is 1, corresponding to the throughput of the pipelined system. The operation set contains the same operations A, B, and C, but there are significant changes. The start dates of B and C are now 0, as the 3 operations are started at the same time in each pipelined execution cycle. A non-pipelined execution cycle spans over several pipelined cycles, and each pipelined cycle starts one non-pipelined cycle.

To account for the prologue phase, where operations progressively start to execute, each operation is assigned a *start index fst*(o). If an operation o has fst(o) = n, it will first be executed in the pipelined cycle of index n (indices start at 0). Due to pipelining, the instance

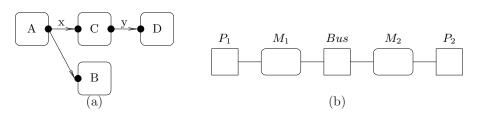

Fig. 7. Example 2: Dataflow specification (a) and a bus-based implementation architecture (b)

| $\operatorname{time}$ | P1     | Bus    | P2     | ] |      |                                                    |                   |                                                    |

|-----------------------|--------|--------|--------|---|------|----------------------------------------------------|-------------------|----------------------------------------------------|

| 0                     | A@true |        |        |   | time | P1                                                 | Bus               | P2                                                 |

| 1                     | B@true | x@true |        |   | 0    | $\begin{array}{c} A@true\\ fst(A) = 0 \end{array}$ |                   | $\begin{array}{c} C@true\\ fst(C) = 1 \end{array}$ |

| 2                     | D@true |        |        |   | 1    | $\begin{array}{c} B@true\\ fst(B) = 0 \end{array}$ | x@true fst(SND)=0 | $\begin{array}{c} D@true\\ fst(D) = 1 \end{array}$ |

| 3                     |        |        | C@true |   | 2    | fst(B) = 0                                         |                   | <b>G</b> (2)                                       |

| 4                     |        |        | Cetrue |   | 3    |                                                    |                   | $\begin{array}{c} C@true\\ fst(C) = 0 \end{array}$ |

| 5                     |        |        |        |   | 4    |                                                    |                   |                                                    |

| 6                     |        |        | D@true |   |      |                                                    |                   |                                                    |

|                       |        | (a)    |        |   |      |                                                    | (b)               |                                                    |

Fig. 8. Example 2: Non-pipelined scheduling table produced by phase 1 of our technique (a) and pipelined table produced by phase 2 (b) for the example of Fig. 7

of *o* executed in the pipelined cycle *m* belongs to the non-pipelined cycle of index m - fst(o). For instance, operation *C* with fst(C) = 2 is first executed in the 3<sup>rd</sup> pipelined cycle (of index 2), but belongs to the first non-pipelined cycle (of index 0).

4.1.2. Example 2: makespan vs. throughput optimization. The example of Fig. 7 showcases how the different optimization objectives of our technique lead to different scheduling results, when compared with existing software pipelining techniques.

The architecture is here more complex, involving a *communication bus* that connects the two identical processors. Communications over the bus are synthesized during the scheduling process, as needed. Note that the bus is modeled as a processor performing communication operations. This level of description, defined in Section 3.1, is accurate enough to support our pipelining algorithms. The makespan-optimizing scheduling algorithms used in phase 1 use more detailed architecture descriptions (outside the scope of this paper).

The functional specification is also more complex, involving parallelism and different durations for the computation and communication operations. The durations of A, B, C, and D on the two processors are respectively 1, 2, 4, and 1, and transmitting over the bus any of the data produced by A or C takes 1 time unit.

Fig. 8(a) provides the non-pipelined scheduling table produced for this example by the makespan-optimizing heuristics of [Potop-Butucaru et al. 2009]. Operations A and B have been allocated on processor P1 and operations C and D have been allocated on P2. One communication is needed to transmit data x from P1 to P2. The makespan is here equal to the table length, which is 7. The throughput is the inverse of the makespan (1/7).

When this scheduling table is given to our pipelining algorithm, the output is the pipelined scheduling table of Fig. 8(b). The makespan remains unchanged (7), but the table length is now 5, so the throughput is 1/5. Note that the execution of operation C starts in one

| $\operatorname{time}$ | P1                                                 | Bus               | P2                                                 | ]    |                                                    |                 |            |

|-----------------------|----------------------------------------------------|-------------------|----------------------------------------------------|------|----------------------------------------------------|-----------------|------------|

| 0                     | $\begin{array}{c} A@true\\ fst(A) = 0 \end{array}$ |                   | $\begin{array}{c} D@true\\ fst(D) = 1 \end{array}$ | time | P1                                                 | Bus             | P2         |

| 1                     | B@true                                             | x@true fst(SND)=0 |                                                    | 0    | $\begin{array}{c} A@true\\ fst(A) = 0 \end{array}$ |                 | C@true     |

| 2                     | fst(B) = 0                                         |                   |                                                    | 1    | B@true                                             | x@true fst(x)=0 | fst(C) = 1 |

| 3                     |                                                    |                   | $\begin{array}{c} C@true\\ fst(C) = 0 \end{array}$ | 2    | fst(B) = 0                                         | y@true fst(y)=1 | C@true     |

| 4                     |                                                    |                   |                                                    | 3    | $\begin{array}{c} D@true\\ fst(D) = 1 \end{array}$ |                 | fst(C) = 0 |

| 5                     |                                                    |                   |                                                    |      |                                                    |                 |            |

|                       |                                                    | (a)               |                                                    | _    |                                                    | (b)             |            |

Fig. 9. Example 2: At left, the result of retiming the scheduling table of Fig. 8(a). At right, the result of directly applying throughput-optimizing modulo scheduling onto the specification of Fig. 7.

Fig. 10. Example 3: Dataflow specification with conditional execution (a) and possible mode transitions (b)

pipelined execution cycle (at date 2), but ends in the next, at date 1. Thus, operation C has two reservations, one with fst(C) = 0, and one with fst(C) = 1.

Operations spanning over multiple execution cycles are not allowed in retiming-based techniques. Thus, if we apply retiming to the scheduling table of Fig. 8(a), we obtain the pipelined scheduling table of Fig. 9(a). For this example, the makespan is not changed, but the throughput is worse than the one produced by our technique (1/6).

But the most interesting comparison is between the output of our pipelining technique and the result of throughput-only optimization. Fig. 9(b) provides a pipelined scheduling table that has optimal throughput. In this table, operation D is executed by processor P1, so that the bus must perform 2 communications. The throughput is better than in our case (1/4 vs. 1/5), but the makespan is worse (8 vs. 7), even though we chose a schedule with the best makespan among those with optimal throughput.

4.1.3. Example 3: Predication handling. To explain how predication is handled in our approach, consider the example of Fig. 10. We only picture here the functional specification. As architecture, we consider two processors P1 and P2 connected to a shared memory M1 (a 2-processor version of the architecture in Fig. 3(b)).

Example 3 introduces new constructs. First of all, it features a *delay*, labeled  $\Delta$ . Delays are used in our data-flow formalism to represent the system state, and are a source of *inter-iteration dependences*. Each delay has an initial value, which is given as output in the first execution cycle, and then outputs at each cycle the value received as input at the previous cycle. The data-flow formalism, including delays, is formally defined in [Potop-Butucaru et al. 2009].

The functional specification also makes use of conditional (predicated) execution. Operations F1, F2, and F3 (of length 3, 2, and 1, respectively) are executed in those execution

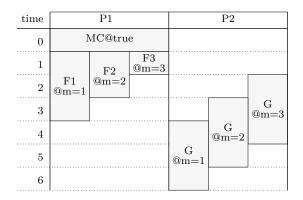

Fig. 11. Example 3: non-pipelined scheduling table

cycles where the output m of operation MC equals respectively 1, 2, or 3. Operations MC and G are executed in all cycles.

The output m of operation MC (for mode computation) is used here to represent the execution mode of our application. This mode is recomputed in the beginning of each execution cycle by MC, based on the previous mode and on unspecified inputs directly acquired by MC. We assume that the application has only 3 possible modes (1, 2, and 3), and that transition between these modes is only possible as specified by the transitions of Fig. 10(b). This constraint is specified with a predicate over the inputs and outputs of operation MC. All data-flow operations can be associated such predicates, which will be used in the analyses of the next sections. Assuming that the input port of operation MC is called  $old_m$ and that the output port is called m, the predicate associated to MC is:

$$(old\_m=m)$$

or  $(old\_m=1 \text{ and } m=2)$  or  $(old\_m=2)$  or  $(old\_m=3 \text{ and } m=2)$

This predicate states that either there is no state change  $(old_m = m)$ , or there is a transition from state 1 to state 2  $(old_m = 1 \text{ and } m = 2)$ , or that the old state is 2, so the new state can be any of the 3  $(old_m = 2)$ , or that there is a transition from state 3 to state 2  $(old_m = 3 \text{ and } m = 2)$ .

We assume that operations MC, F1, F2, and F3 are executed on processor P1, and that G is executed on P2. Under these conditions, one possible non-pipelined schedule produced by Phase 1 is the one pictured in Fig. 11. Note that this table features 3 conditional reservations for operation G, even if G does not have an execution condition in the data-flow graph. This allows G to start as early as possible in every given mode.

This table clearly features the reservation of the same resource, at the same time, by multiple operations. For instance, operations F1, F2, and F3 share P1 at date 1. Of course, each time this happens the operations must have exclusive predicates, meaning that there is no conflict at runtime.

Pipelining this table using the algorithms of the following sections produces the scheduling table of Fig. 12. The most interesting aspect of this table is that the reservations G@m=1,fst=1 and G@m=3,fst=0, which belong to different execution cycles of the nonpipelined table, are allowed to overlap in time. This is possible because the dependency analysis of Section 5 determined that the two operations have exclusive execution conditions. In our case, this is due to the fact that m cannot change its value directly from 1 to 3 when moving from one non-pipelined cycle to the next.

When relations between execution conditions of operations belonging to different execution cycles are not taken into account, the resulting pipelining is that of Fig. 13. Here, reservations for G cannot overlap in time if they have different *fst* values.

| time | P1             |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P2            |                                                                 |                                                                 |

|------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| 0    | 1              | MC@tru     | е                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | G             | G                                                               | $\operatorname{Gm=3}_{\operatorname{fst=1}}^{\operatorname{G}}$ |

| 1    | F1             | F2<br>@m=2 | ${{\mathbb{G}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{\mathbb{F}}{$ | @m=1<br>fst=1 | $_{fst=1}^{@m=2}$                                               |                                                                 |

| 2    | m=1<br>fst = 0 | fst = 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                                                 | G                                                               |

| 3    |                |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | $\operatorname{Gm=2}_{\operatorname{fst}=0}^{\operatorname{G}}$ | $@m=3 \\ fst = 0$                                               |

| $\operatorname{time}$ |                     | P1                  |                     |                                     | P2                                                              |                    |

|-----------------------|---------------------|---------------------|---------------------|-------------------------------------|-----------------------------------------------------------------|--------------------|

| 0                     | MC@true             |                     |                     | G                                   | $\operatorname{Gm=2}_{\operatorname{fst=1}}^{\operatorname{G}}$ |                    |

| 1<br>2<br>3<br>4      | F1<br>@m=1<br>fst=0 | F2<br>@m=2<br>fst=0 | F3<br>@m=3<br>fst=0 | @m=1<br>fst=1<br>G<br>@m=1<br>fst=0 | G<br>@m=2<br>fst=0                                              | G<br>@m=3<br>fst=0 |

Fig. 12. Example 3: Pipelined scheduling table pro- Fig. 13. Example 3: Pipelined scheduling table duced by our technique

where inter-cycle execution condition analysis has not been used to improve sharing.

The current implementation of our algorithms can only analyze predicates with Boolean arguments. Thus, our 3-valued mode variable m needs re-encoding with 2 Boolean variables. In other words, in the version of Example 3 that can be processed by our tool, the operation MC actually has 2 Boolean inputs and 2 Boolean outputs, and the predicate above is defined using these 4 variables.

#### 4.2. Construction of the pipelined scheduling table

The prologues of our pipelined executions are obtained by incremental activation of the steady state operations, as specified by the *fst* indices (this is a classical feature of modulo scheduling pipelining approaches). Then, the pipelined scheduling table can be fully built using Algorithm 1 starting from the non-pipelined table and from the pipelined initiation interval. The algorithm first determines the start index and new start date of each operation by folding the non-pipelined table onto the new period. Algorithm AssembleSchedule then determines which memory cells need to be replicated due to pipelining, using the technique provided in Section 4.4.

$\mathcal{S}$ : non-pipelined scheduling table Input:  $\hat{p}$ : pipelined initiation interval **Output:**  $\widehat{\mathcal{S}}$  : pipelined schedule table for all o in  $\mathcal{O}$  do  $fst(o) := \lfloor \frac{t(o)}{\widehat{p}} \rfloor$   $\widehat{t}(o) := t(o) - fst(o) * \widehat{p}$ end for  $\mathcal{S} := AssembleSchedule(\mathcal{S}, \hat{p}, fst, \hat{t})$ Algorithm 1: BuildSchedule