Diogo Sampaio, Rafael Martins de Souza, Caroline Collange, Fernando Magno Quintão Pereira

## ► To cite this version:

Diogo Sampaio, Rafael Martins de Souza, Caroline Collange, Fernando Magno Quintão Pereira. Divergence Analysis. ACM Transactions on Programming Languages and Systems (TOPLAS), 2013, 35 (4), pp.13:1-13:36. 10.1145/2523815 . hal-00909072

# HAL Id: hal-00909072 https://inria.hal.science/hal-00909072

Submitted on 8 Oct 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

Diogo Sampaio, Universidade Federal de Minas Gerais Rafael Martins de Souza, Universidade Federal de Minas Gerais Caroline Collange, INRIA Fernando Magno Quintão Pereira, Universidade Federal de Minas Gerais

The growing interest in graphics processing units has brought renewed attention to the Single Instruction Multiple Data (SIMD) execution model. SIMD machines give application developers tremendous computational power; however, programming them is still challenging. In particular, developers must deal with memory and control flow divergences. These phenomena stem from a condition that we call data divergence, which occurs whenever two processing elements (PEs) see the same variable name holding different values. This paper introduces divergence analysis, a static analysis that discovers data divergences. This analysis, currently deployed in an industrial quality compiler, is useful in several ways: it improves the translation of SIMD code to non-SIMD CPUs, it helps developers to manually improve their SIMD applications, and it also guides the automatic optimization of SIMD programs. We demonstrate this last point by introducing the notion of a divergence aware register allocator. This allocator uses information from our analysis to either rematerialize or share common data between PEs. As a testimony of its effectiveness, we have tested it on a suite of 395 CUDA kernels from well-known benchmarks. The divergence aware allocator produces GPU code that is 26.21% faster than the code produced by the allocator used in the baseline compiler.

Categories and Subject Descriptors: D.3.4 [Software]: Programming Languages

General Terms: Languages, Design, Algorithms, Performance

Additional Key Words and Phrases: Static program analysis, divergence analysis, SIMD, graphics processing units, high performance

#### **ACM Reference Format:**

Sampaio, D., Sousa, R., Collange, S., Pereira, F. 201X. Divergence Analysis. ACM Trans. Program. Lang. Syst. 35, 4, Article 13 (January 2014), 37 pages.

$DOI = 10.1145/2523815 \ http://doi.acm.org/10.1145/2523815$

#### 1. INTRODUCTION

Increasing programmability and low hardware cost are boosting the use of graphical processing units (GPU) as a tool to run general purpose applications. Illustrative examples of this new trend are the rising popularity of CUDA<sup>1</sup>, AMD APP <sup>2</sup> and OpenCL<sup>3</sup>. Running general purpose programs in GPUs is attractive because these processors are massively parallel. As an example, the GeForce GTX 580 GPU series has 512 processing units that can be simultaneously used by up to 24,576 threads. Similar hardware has allowed the development of high performance algorithms to solve problems as diverse as sorting [Cederman and Tsigas 2009], gene sequencing [Sandes and de Melo 2010], IP routing [Mu et al. 2010] and program analysis [Prabhu et al. 2011]. In many cases, these applications outperform the equivalent CPU program by factors of over 100x [Ryoo et al. 2008]. This trend is likely to continue, as upcoming hardware more

This work is supported by FAPEMIG grant 2010/2.

Author's addresses: D. Sampaio and F. Pereira, Computer Science Department, The Federal University of Minas Gerais, Antônio Carlos Avenue, 6613, Belo Horizonte, Brazil. S. Collange, INRIA Centre Rennes - Bretagne Atlantique, Campus de Beaulieu, 35042 Rennes Cedex, France Copyright held by the owner/author(s).

DOI 10.1145/2523815 http://doi.acm.org/10.1145/2523815

$<sup>^{1}\</sup>mathrm{See}\ The\ CUDA\ Programming\ Guide,\ 1.1.1$

<sup>&</sup>lt;sup>2</sup>See AMD APP Guide

<sup>&</sup>lt;sup>3</sup>See The OpenCL Specification, 1.0

13:2 Sampaio et al.

closely integrates GPUs and CPUs [Boudier and Sellers 2011], and new models of heterogeneous hardware are introduced [Lee et al. 2011; Saha et al. 2009].

GPUs are highly parallel; however, due to their restrictive programming model, not every application can benefit from this parallelism. These processors organize threads in groups that execute in lock-step. Such groups are called *warps* in NVIDIA's jargon, or *wavefronts* in AMD's. To understand the rules that govern threads in the same warp, we can imagine that each warp has simultaneous access to many processing units, but uses only one instruction fetcher. As an example, the GeForce GTX 590 has 32 Streaming Multiprocessors, and each of them can run 48 warps of 32 threads. Thus, each warp might execute 32 instances of the same instruction simultaneously. Regular applications, such as scalar vector multiplication, fare very well in GPUs, as we have the same operation being independently performed on different chunks of data. However, divergences may happen in less regular applications.

Data divergence occurs if the same variable name is mapped to different values in the environments of distinct processing elements. In this case we say that the variable is divergent, otherwise we call it uniform. A thread identifier, for instance, is inherently divergent. Data divergence is responsible for two phenomena that can compromise performance: memory and control flow divergences. Control flow divergences happen when threads in a warp follow different paths after processing the same branch. If the branching condition is data divergent, then it might be true to some threads, and false to others. Given that each warp has access to only one instruction at a time some threads have to wait idly, while others execute. Memory divergences, a term coined by Meng et al. [2010] happen whenever a load or store instruction targeting data divergent addresses causes threads to access memory positions with bad locality. Such events have been shown to have even more performance impact than control flow divergences [Lashgar and Baniasadi 2011]. Optimizing an application to avoid divergences is problematic for two reasons. First, some parallel algorithms are intrinsically divergent; thus, threads will naturally disagree on the outcome of branches. Second, identifying divergences burdens the application developer with a tedious task, which requires a deep understanding of code that might be large and complex.

The main goal of this paper is to provide compilers with techniques that help them to understand and to improve divergent code. To meet such objective, in Section 3.3 we present a static program analysis that identifies data divergences. We then expand this analysis, discussing, in Section 3.4 a more advanced algorithm that distinguishes divergent and affine variables, e.g., variables that are affine expressions of thread identifiers. The two analyses that we discuss in this paper rely on the classic notion of Gated Static Single Assignment form [Ottenstein et al. 1990; Tu and Padua 1995], which we revisit in Section 3.2. We formalize our algorithms by proving their correctness with regard to  $\mu$ -SIMD, a core language that we describe in Section 3.1.

The divergence analysis is important in different ways. Firstly, it helps the compiler to optimize the translation of "SIMD" languages to ordinary CPUs. We call SIMD languages those programming languages, such as C for CUDA and OpenCL, that are equipped with abstractions to handle divergences. Currently there exist many proposals to compile such languages to ordinary CPUs [Diamos et al. 2010; Karrenberg and Hack 2011; Stratton et al. 2010], and they all face similar difficulties. Vectorial operations found in traditional architectures, such as the x86's SSE extension, do not support divergences natively. Thus, compilers need to produce very inefficient code to handle this phenomenon at the software level. This burden can be safely removed from the uniform, e.g., non-divergent, branches that we identify. Furthermore, the divergence analysis provides insights about memory access patterns [Byunghyun Jang and Kaeli AHPC]. In particular, a uniform address means that threads access the same location in memory, whereas an affine address means that consecutive threads access

adjacent or regularly-spaced memory locations. This information is critical to generate efficient code for vectorial instruction sets that do not support fast memory gather and scatter [Diamos et al. 2010].

Secondly, in order to more precisely identify divergences, a common strategy is to use instrumentation based profilers. However, this approach may slowdown the target program by factors of over 1500x [Coutinho et al. 2013]! Our divergence analysis reduces the amount of branches that the profiler must instrument; hence, decreasing its overhead. Thirdly, the divergence analysis improves the static performance prediction techniques used in SIMD architectures [Baghsorkhi et al. 2010; Zhang and Owens 2011]. Such methods are used, for instance, by adaptive compilers that target GPUs [Samadi et al. 2012]. Finally, our analysis also helps the compiler to produce more efficient code to SIMD hardware. There exists a recent number of divergence aware code optimizations, such as Coutinho et al.'s [2011] branch fusion, and Zhang et al.'s [2011] thread reallocation strategy. In this paper, we augment this family of techniques with a divergence aware register allocator. As we will show in Section 4, we use divergence information to decide the best location of variables that have been spilled during register allocation. Our affine analysis is specially useful to this end, because it enables us to perform a form of rematerialization [Briggs et al. 1992] of values among SIMD processing elements.

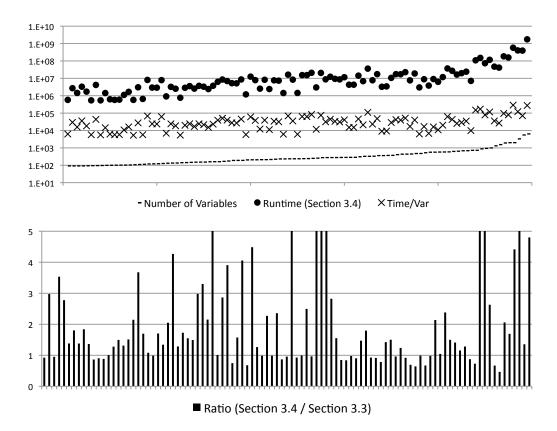

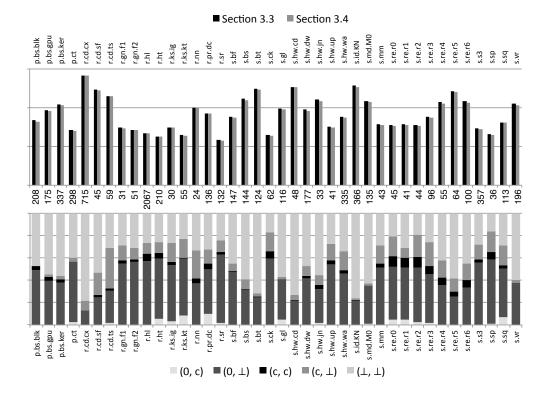

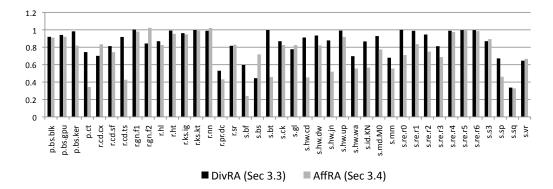

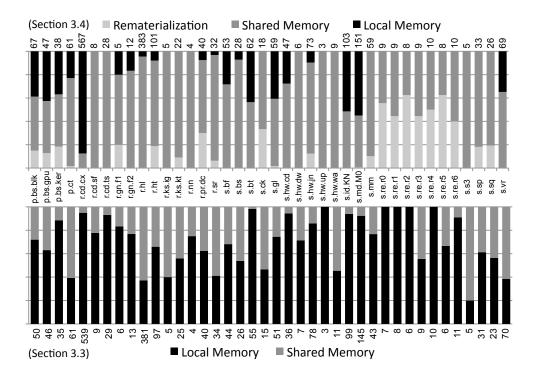

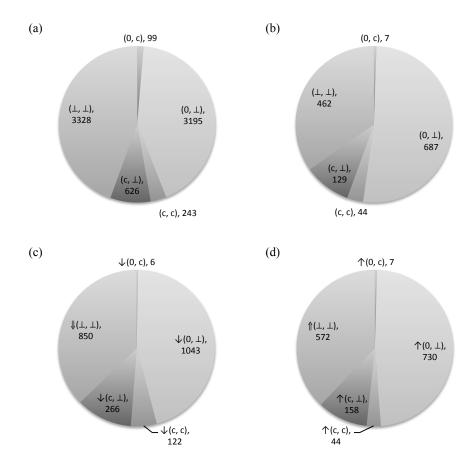

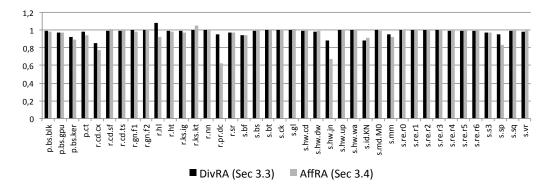

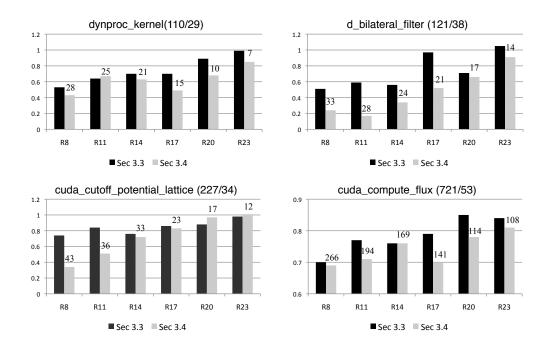

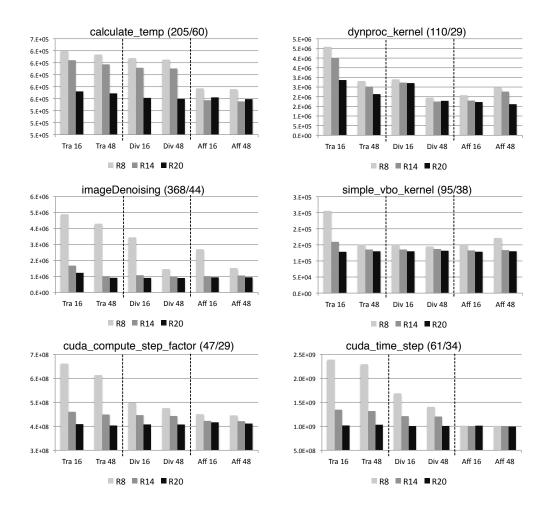

All the algorithms that we describe in this paper are publicly available in the Ocelot compiler [Diamos et al. 2010]. This implementation consists of over 10,000 lines of open source code. Ocelot optimizes PTX, the intermediate program representation used by NVIDIA'S GPUs. We have compiled all the 177 CUDA kernels from 46 applications taken from the Rodinia [Che et al. 2009] and the NVIDIA SDK benchmarks. The experimental results given in Section 5 show that our implementation of the divergence analysis runs in linear time on the number of variables in the source program. The basic divergence analysis proves that 36.2% of the variables we have found in our benchmarks are uniform. The affine constraints from Section 3.4 increase this number by 4%, and – more important – they indicate that about one fourth, i.e., 24.84%, of the divergent variables are affine functions of some thread identifier. Finally, our divergence aware register allocator is effective: by rematerializing affine values, or moving uniform values to the GPU's shared memory, we have been able to speedup the code produced by Ocelot's original allocator by almost 30%.

This article closes our three years of work in divergence analysis for SIMD architectures. Our first publication in this field [Coutinho et al. 2011] introduced the divergence analysis that we discuss in Section 3.3. At that time, we chose to describe this static analysis as an instance of the more general graph reachability problem, following an earlier approach adopted by Scholz et al. [2008] to detect tainted flow vulnerabilities in programs. Presently, we have opted to depart from the graph reachability framework, in favor of a constraint oriented notation, because, as we see in Section 3.3, this new notation simplifies our correctness proofs. The extended divergence analysis from Section 3.4 was presented in late 2012 [Sampaio et al. 2012b]. In that work we mentioned our divergence aware register allocator; however, in this paper we explain it in much deeper details, following a previous description given in the Brazilian Workshop of Programming Languages [Sampaio et al. 2012a].

#### 2. BACKGROUND

A modern graphics processing unit usually provides to developers a large number of threads arranged in small groups called warps. Different warps execute independently of each other, following Darema's *Single Program Multiple Data* (SPMD) execution model [Darema et al. 1988]. On the other hand, the threads inside the same warp execute in lock-step, fitting Flynn's *Single Instruction Multiple Data* (SIMD) ma-

13:4 Sampaio et al.

chines [Flynn 1972]. This combination of SPMD and SIMD semantics is one of the characteristics of the so called *Single Instruction Multiple Threads* (SIMT) execution model [Garland and Kirk 2010; Nickolls and Kirk 2009; Nickolls and Dally 2010]. In this paper we will focus on the SIMD characteristics of a typical GPU, because divergences are relevant only at this level.

We will use the two artificial programs in Figure 1 to explain the notion of divergences. These functions, normally called kernels, are written in C for CUDA and run on graphics processing units. We will assume that these programs are executed by a number of threads, or processing elements, according to the SIMD semantics. All the processing elements see the same set of variable names; however, each one maps this environment onto a different address space. Furthermore, each processing element has a particular set of identifiers. In C for CUDA this set includes the index of the thread in three different dimensions, e.g., threadIdx.x, threadIdx.y and threadIdx.z. At the hardware level, a processing element has access to more identifiers, such as its position inside the warp (laneid), for instance. For this discussion, just the understanding that a thread has a unique identifier is enough. In the rest of this paper we will denote this unique thread identifier by laneid.

Each processing element uses its unique identifier to find the data that it must process. Thus, in the kernel avgSquare each thread  $T_{id}$  is in charge of summing up the elements of the  $T_{id}$ -th column of m. Once leaving the loop, this PE will store the average of the sum in  $v[T_{id}]$ . This is a divergent memory access: different addresses will be simultaneously accessed by many threads. However, modern GPUs can perform these accesses very efficiently, because they have good locality. In this example addresses used by successive threads are contiguous [Ryoo et al. 2008; Yang et al. 2010]. Control flow divergences will not happen in avgSquare. That is, each thread will loop the same number of times. Consequently, upon leaving the loop every thread sees the same value at its image of variable d. Thus, we call this variable uniform.

Kernel sumTriangle presents a very different behavior. This rather contrived function sums up the columns in the superior triangle of matrix m; however, only the odd indices of a column contribute to the sum. In this case, the threads perform different amounts of work: the PE that has  $T_{id}=n$  will visit n+1 cells of m. After a thread leaves the loop, it must wait for the others. Processing resumes once all of them synchronize at line 12. At this point, each thread sees a different value stored at its image of variable d, which has been incremented  $T_{id}+1$  times. Hence, we say that d is a divergent variable outside the loop. Inside the loop, d is uniform, because every active thread sees the same value stored at that location. Thus, all the threads active inside the loop take the same path at the branch in line 7. Therefore, a precise divergence analysis must split the live range of d into a divergent and a uniform part.

Divergence Optimizations. We call divergence optimizations the code transformation techniques that use the results of divergence analysis to generate better programs. Some of these optimizations deal with memory divergences; however, methods dealing exclusively with control flow divergences are the most common in the literature. As an example, the PTX programmer's manual <sup>4</sup> recommends replacing ordinary branch instructions (bra) proved to be non-divergent by special instructions (bra.uni), which are supposed to divert control to the same place for every active thread. Other examples of control flow divergence optimizations include branch distribution, branch fusion, branch splitting, loop collapsing, iteration delaying and thread reallocation.

**Optimizing divergent control flow.** Branch distribution [Han and Abdelrahman 2011] is a form of code hoisting that works both at the prolog and at the epilogue of

<sup>&</sup>lt;sup>4</sup>PTX programmer's manual, 2008-10-17, SP-03483-001\_v1.3, ISA 1.3

```

1 global void avgSquare(float* m, float* v, int c) {

2 if (T_{id} < c) {

T_{id} = 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10

int d = 0;

4

float sum = 0.0F;

5

int N = T_{id} + c * c;

for (int i = T_{id}; i < N; i += c) {

6

7

sum += m[i];

d += 1;

9

10

v[tid] = sum / d;

11 }

\forall T_{id}, d = 10

12}

1 __global__ void sumTriangle(float* m, float* v, int c) {

if (T_{id} < c) {

int d = 0;

3

T_{id} = 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10

float sum = 0.0F;

4

5

int L = (T_{id} + 1) * c;

6

for (int i = T_{id}; i < L; i += c) {

7

if (d % 2) {

sum += m[i];

10

d += 1;

11

d-1 = 0 \ 1 \ 2 \ 3 \ 4 \ 5 \ 6 \ 7 \ 8 \ 9 \ 10

12

v[d-1] = sum;

13 }

14}

```

Fig. 1. Two kernels written in C for CUDA. The gray lines in the right show the parts of matrix m processed by each thread. Following usual coding practices we represent the matrix in a linear format. Dots mark the cells that add up to the sum in line 8 of sumTriangle.

a branch. This optimization merges code inside potentially divergent program paths. Branch fusion [Coutinho et al. 2011], a generalization of branch distribution, joins chains of common instructions present in two divergent paths. A number of compiler optimizations try to rearrange loops in order to mitigate the impact of divergences. Carrillo et al. [2009] have proposed branch splitting, a way to divide a parallelizable loop enclosing a multi-path branch into multiple loops, each containing only one branch. Lee et al. [2009] have designed loop collapsing, a compiler technique that they use to reduce divergences inside loops when compiling OpenMP programs into C for CUDA. Later, Han and Abdelrahman [2011] have generalized Lee's approach proposing iteration delaying, a method that regroups loop iterations, executing those that take the same branch direction together.

13:6 Sampaio et al.

Thread reallocation is a technique that applies on settings that combine the SIMD and the SPMD semantics, like the modern GPUs. This optimization consists in regrouping divergent threads among warps, so that only one or just a few warps will contain divergent threads. It has been implemented at the software level by Zhang et al. [2010, 2011], and simulated at the hardware level by Fung et al. [2007]. This optimization must be used with moderation, because Lashgar and Baniasadi [2011, Sec 4.A] have shown that unrestrained thread regrouping could lead to memory divergences.

Optimizing divergent memory accesses. The compiler related literature describes optimizations that try to change memory access patterns is such a way to improve address locality. Recently, some of these techniques have been adapted to mitigate the impact of memory divergences in modern GPUs. Yang et al. [2010] and Pharr and Mark [2012] describe a suite of loop transformations to *coalesce* data accesses. Memory coalescing consists in the dynamic aggregation of contiguous locations into a single data access. Leißa et al. [2012] discuss several data layouts that improve memory locality in the SIMD execution model.

**Reducing redundant SIMD work.** The literature describes a few optimizations that use data divergence information to reduce the amount of work that the SIMD processing elements do. For instance, Collange et al. [2009] have introduced *work unification*. This compiler technique leaves to only one thread the task of computing uniform values; hence, reducing memory accesses and hardware occupancy. Some computer architectures, such as Intel MIC <sup>5</sup> and AMD GCN <sup>6</sup>, combine scalar and vector processing units. Capitalizing on this observation, a recent work, by Lee et al. [2013], uses divergence analysis to assign computations to either scalar or vector processing units.

A Comparison between Previous Divergence Analyses and our approaches. Several algorithms have been proposed in the literature to find uniform variables. It is also generally assumed that industrial compilers, like AMD's or Nvidia's, implement some sort of divergence analysis, such as Grover's algorithm [Grover et al. 2009]. As an example, the AMD GCN compiler is able to target scalar units with uniform instructions. Furthermore, these uniform instructions can use scalar registers instead of shared memory, a capacity that would require techniques similar to those we describe in Section 4. Nevertheless, such industrial solutions are not open to the public. The first technique that we are aware of is the barrier inference of Aiken and Gay [1998]. This method, designed for SPMD machines, finds a conservative set of uniform 7 variables via static analysis. However, because it is tied to the SPMD model, Aiken and Gay's algorithm can only report uniform variables at global synchronization points.

The recent interest on graphics processing units has given a renewed impulse to this type of analysis, in particular with a focus on SIMD machines. The first description of a divergence analysis targeting the execution model of a GPU that we are aware of is due to Stratton et al. [2010], who called it variance analysis. The description of Stratton's *et al.*'s work is too brief to allows us to compare it with our techniques, but an extended version of variance analysis appears in a patent application by Grover et al. [2009]. From the patent description, we infer that variance analysis is similar to our divergence analysis from Section 3.3, except that it does not distinguish different abstract states of variables inside and outside loops. We obtain this distinction from our intermediate representation, the gated static single assignment form, which splits live

<sup>&</sup>lt;sup>5</sup>See Intel pushes for HPC space with Knights Corner, at www.thinq.co.uk. Last visit: June'12

<sup>&</sup>lt;sup>6</sup>See Understanding AMD's Roadmap at http://www.anandtech.com/. Last visit: June 12

<sup>&</sup>lt;sup>7</sup>Aiken and Gay would call these variables *single-valued*

ranges of variables that escape loops. The variance analysis has been further expanded by Lee et al. [2013], who proposed to use it to separate scalar and vector operations in a SIMD program. Lee *et al.* mention the possibility of combining their variance analysis with Collange's affine analysis [Collange et al. 2009] to optimize memory accesses. However, the single paragraph description of their approach [Lee et al. 2013, Sec 3.5] does not give us enough subsidies to compare it with our algorithm from Section 3.4.

Another variation of divergence analysis has been recently proposed by researchers from Saarland University: the vectorization analysis, due to Karrenberg and Hack [2011]. The vectorization analysis can track some affine relations between variables in the SIMD execution model. In particular, it can identify which variables hold values that are consecutively spaced between successive threads. Yet, contrary to our approach, the vectorization analysis does not take control flow dependences into consideration when determining the abstract state of variables. This omission is not a problem in their scenario, because the vectorization analysis is a technique used in the compilation of SPMD programs to CPUs with explicit SIMD instructions. Its host compiler generates specific instructions to manage divergences at runtime. However, a naïve application of Karrenberg's analyses in our static context may wrongly report that a divergent variable is uniform due to control dependences. As an example of this behavior, Karrenberg's select and loop-blending functions are similar to the  $\gamma$  and  $\eta$  functions that we discuss in Section 3.2. Nevertheless, select and blend are concrete instructions emitted during code generation, whereas our GSA functions are abstractions used statically. Karrenberg and Hack have, recently, proposed their version of divergence analysis [Karrenberg and Hack 2012], which they invented independently from us. Their technique is equivalent to our first design of divergence analysis [Coutinho et al. 2011], and, like it, it does not consider affine relations between variables. It is able, for instance, to assign different states to variables inside and outside loops, like our approach does. The main difference between our first method, discussed in Section 3.3, and theirs, is in terms of implementation. We use the GSA form to obtain a sparse analysis, whereas Karrenberg and Hack have opted for a dense style, that binds information to pairs of variables and program points.

Figure 2 summarizes this discussion comparing the results produced by these different variations of the divergence analysis when applied on the kernels in Figure 1. We call  $Data\ Dep$ . a divergence analysis that takes data dependences into consideration, but not control dependences. In this case, a variable is uniform if it is initialized with constants or broadcasted values, or, recursively, if it is a function of only uniform variables. This analysis would, incorrectly, flag variable d in sumTriangle, as uniform. Notice that, because this paper's analyses use the GSA intermediate representation, they distinguish the live ranges of variable d before  $(d_{bf})$ , inside  $(d_{lp})$  and after  $(d_{af})$  the loops. The analysis that we present in Section 3.4 improves on the analysis that we discuss in Section 3.3 because it considers affine relations between variables. Thus, it can report that the loop in avgSquare is non-divergent, by noticing that the comparison i < N has always the same value for every thread. This fact happens because both variables are functions of two affine expressions of  $T_{id}$ , whose combination cancel the  $T_{id}$  factor out, e.g.:  $N = T_{id} + c_1$  and  $i = T_{id} + c_2$ ; thus,  $N - i = (1-1)T_{id} + c_1 - c_2$ .

#### 3. DIVERGENCE ANALYSES

In this section we describe two divergence analyses. The first, which we present in Section 3.3, has a very simple and fast implementation. This initial analysis helps us to formalize the second algorithm, slower, yet more precise, which we present in Section 3.4. This formalization uses a simple SIMD language, introduced in Section 3.1, which we call  $\mu$ -SIMD. Our divergence analyses work on a preprocessed version of  $\mu$ -SIMD programs. Preprocessing, in our case, consists in converting the  $\mu$ -SIMD pro-

13:8 Sampaio et al.

|                   | Data Dep. | Aiken | Karr. | Grover | Sec. 3.3 | Sec. 3.4                                       |

|-------------------|-----------|-------|-------|--------|----------|------------------------------------------------|

| С                 | U         | U     | U     | U      | U        | $0T_{id}^2 + 0T_{id} + \bot$                   |

| m                 | U         | U     | U     | U      | U        | $0\mathbf{T}_{id}^2 + 0\mathbf{T}_{id} + \bot$ |

| v                 | U         | U     | U     | U      | U        | $0\mathbf{T}_{id}^2 + 0\mathbf{T}_{id} + \bot$ |

| i                 | D         | D     | ca    | D      | D        | $0\mathtt{T}_{id}^2+\mathtt{T}_{id}+ot$        |

| avgS              | quare     |       |       |        |          |                                                |

| N                 | D         | D     | С     | D      | D        | $0\mathtt{T}_{id}^2+\mathtt{T}_{id}+\bot$      |

| $d_{bf}$          | U         | D     | U     | U      | U        | $0T_{id}^2 + 0T_{id} + 0$                      |

| $\mathtt{d}_{lp}$ | U         | D     | D     | D      | U        | $0\mathbf{T}_{id}^2 + 0\mathbf{T}_{id} + \bot$ |

| $d_{af}$          | U         | D     | D     | D      | D        | $0\mathbf{T}_{id}^2+0\mathbf{T}_{id}+\bot$     |

| sumT              | riangle   |       |       |        |          |                                                |

| L                 | D         | D     | D     | D      | D        | $0T_{id}^2 + \bot T_{id} + \bot$               |

| $d_{bf}$          | U         | D     | U     | U      | U        | $0T_{id}^2 + 0T_{id} + 0$                      |

| $\mathtt{d}_{lp}$ | U         | D     | D     | D      | U        | $0\mathbf{T}_{id}^2 + 0\mathbf{T}_{id} + \bot$ |

| $\mathtt{d}_{af}$ | U         | D     | D     | D      | D        | $\perp T_{id}^2 + \perp T_{id} + \perp$        |

Fig. 2. A comparison between different versions of divergence analyses. We use U for uniform and D for Divergent variables. Karrenberg's analysis can mark variables in the format  $1 \times T_{id} + c$ ,  $c \in \mathbb{N}$  as consecutive (c) or consecutive aligned (ca). As we explain in Section 3.4, the symbol  $\bot$  denotes unknown values.

grams to an intermediate representation called Gated Static Single Assignment (GSA) form, that we describe in Section 3.2.

#### 3.1. The Core Language

In order to formalize the theory that we develop in this paper, we adopt the same model of SIMD execution independently described by Bougé and Levaire [1992] and Farrell and Kieronska [1996]. We have a number of processing elements (PEs) executing instructions in lock-step, yet subject to partial execution. In the words of Farrel et al., "All PEs execute the same statement at the same time with the internal state of each PE being either active or inactive." [Farrell and Kieronska 1996, p.40]. The archetype of a SIMD machine is the ILLIAC IV Computer [Bouknight et al. 1972], and there exist many old programming languages that target this model [Abel et al. 1969; Bouknight et al. 1972; Brockmann and Wanka 1997; Keryell et al. 1991; Kung et al. 1982; Lawrie et al. 1975; Perrot 1979]. The recent developments in graphics cards have brought new members to this family. The Single Instruction Multiple Threads (SIMT) [Garland and Kirk 2010; Nickolls and Kirk 2009; Nickolls and Dally 2010] execution model, a term made popular by Nvidia's GPUs, is currently implemented as a multi-core SIMD machine – CUDA being a programming language that coordinates many SIMD processors. We formalize the SIMD execution model via a core language that we call  $\mu$ -SIMD, and whose syntax is given in Figure 3. We do not reuse the formal semantics of Bougé et al. or Farrell et al. because they assume high-level languages, whereas our techniques are better described at the assembly level. Notice that our model will not fit vector instructions, popularly called SIMD, such as Intel's SSE extensions, because they do not support partial execution, rather following the semantics of Carnegie Mellon's Vcode [Blelloch and Chatterjee 1990]. An interpreter for  $\mu$ -SIMD, written in Prolog, plus many example programs, are available in our webpage[Pereira 2011].

We define an abstract machine to evaluate  $\mu$ -SIMD programs. The state M of this machine is determined by a tuple with five elements:  $(\Theta, \Sigma, \Pi, P, pc)$ , which we define in Figure 4. A processing element is a pair  $(t, \sigma)$ , uniquely identified by the natural t, referred by the special variable  $T_{id}$ . The symbol  $\sigma$  represents the PE's local mem-

```

Labels

l \subset \mathbb{N}

Constants (C)

c \subset \mathbb{N}

Variables (V)

\mathtt{T}_{id} \cup \{v_1, v_2, \ldots\}

Operands (V \cup C)

\{o_1, o_2, \ldots\}

Instructions

- (jump if zero/not zero)

bz/bnz v, l

- (unconditional jump)

jump l

- (store into shared memory)

\uparrow v_x = v

- (load from shared memory)

v = \downarrow v_x

v \xleftarrow{a} v_x + 1

- (atomic increment)

- (binary addition)

v_1 = o_1 + o_2

- (binary multiplication)

v_1 = o_1 \times o_2

- (other binary operations)

v_1 = o_1 \oplus o_2

- (simple copy)

v = o

- (synchronization barrier)

sync

- (halt execution)

stop

```

Fig. 3. The syntax of  $\mu$ -SIMD instructions.

```

\begin{array}{ll} \text{(Local memory)} & \sigma \subset \mathit{Var} \mapsto \mathbb{Z} \\ \text{(Shared vector)} & \Sigma \subset \mathbb{N} \mapsto \mathbb{Z} \\ \text{(Active PEs)} & \Theta \subset (\mathbb{N} \times \sigma) \\ \text{(Program)} & P \subset \mathit{Lbl} \mapsto \mathit{Inst} \\ \text{(Sync stack)} & \Pi \subset \mathit{Lbl} \times \Theta \times \mathit{Lbl} \times \Theta \times \Pi \\ \end{array}

```

Fig. 4. Elements that constitute the state of a  $\mu$ -SIMD program.

```

\begin{split} & \mathbf{split}(\Theta, v) = (\Theta_0, \Theta_n) \ \mathbf{where} \\ & \Theta_0 = \{(t, \sigma) \mid (t, \sigma) \in \Theta \ \mathbf{and} \ \sigma[v] = 0\} \\ & \Theta_n = \{(t, \sigma) \mid (t, \sigma) \in \Theta \ \mathbf{and} \ \sigma[v] \neq 0\} \end{split} & \mathbf{push}([], \Theta_n, pc, l) = [(pc, [], l, \Theta_n)] & \mathbf{push}((pc', [], l', \Theta_n') : \Pi, \Theta_n, pc, l) = \Pi' \ \mathbf{if} \ pc \neq pc' \\ & \mathbf{where} \ \Pi' = (pc, [], l, \Theta_n) : (pc', [], l', \Theta_n') : \Pi \end{split} & \mathbf{push}((pc, [], l, \Theta_n') : \Pi, \Theta_n, pc, l) = (pc, [], l, \Theta_n \cup \Theta_n') : \Pi \end{split}

```

Fig. 5. The auxiliary functions used in the definition of  $\mu$ -SIMD.

ory, a function that maps variables to integers. The local memory is individual to each PE; however, these functions have the same domain. Thus,  $v \in \sigma$  denotes a vector of variables, each of them private to a PE. PEs can communicate through a shared array  $\Sigma$ . We use  $\Theta$  to designate the set of active PEs. A program P is a map of labels to instructions. The result of executing a  $\mu$ -SIMD abstract machine is a pair  $(\Theta, \Sigma)$ . The program counter (pc) is the label of the next instruction to be executed. The machine contains a synchronization stack  $\Pi$ . Each node of  $\Pi$  is a tuple  $(l_{id}, \Theta_{done}, l_{next}, \Theta_{todo})$  that denotes a point where divergent PEs must synchronize. These nodes are pushed into the stack when the PEs diverge in the control flow. The label  $l_{id}$  denotes the conditional branch that caused the divergence,  $\Theta_{done}$  are the PEs that have reached the synchronization point, whereas  $\Theta_{todo}$  are the PEs waiting to execute. The label  $l_{next}$  indicates the instruction where  $\Theta_{todo}$  will resume execution.

Figures 5, 6 and 7 describe the big-step semantics of  $\mu$ -SIMD. We use the auxiliary functions in Figure 5, plus the rules in Figure 6, to determine the semantics of instructions that change the program's control flow. According to Rule SP, a program termi-

13:10 Sampaio et al.

(SP)

$$\frac{P[pc] = \mathsf{stop}}{(\Theta, \Sigma, \emptyset, P, pc) \to (\Theta, \Sigma)}$$

$$(BT) \qquad \frac{P[pc] = \text{bz } v, l}{\text{\textbf{push}}(\Pi, \emptyset, pc, l) = \Pi'} \qquad (\Theta, \Sigma, \Pi', P, l) \rightarrow (\Theta', \Sigma') \\ (\Theta, \Sigma, \Pi, P, pc) \rightarrow (\Theta', \Sigma')$$

$$(\mathrm{BF}) \qquad \frac{P[\mathit{pc}] = \mathsf{bz} \; v, l}{\mathbf{push}(\Pi, \emptyset, \mathit{pc}, l) = \Pi' \qquad (\Theta, \Sigma, \Pi', P, \mathit{pc} + 1) \to (\Theta', \Sigma')}{(\Theta, \Sigma, \Pi, P, \mathit{pc}) \to (\Theta', \Sigma')}$$

$$(BD) \quad \frac{\mathbf{split}(\Theta,v) = (\Theta_0,\Theta_n)}{\mathbf{split}(\Theta,v) = (\Theta_0,\Theta_n)} \quad \frac{P[pc] = \mathbf{bz} \ v,l}{\mathbf{push}(\Pi,\Theta_n,pc,l) = \Pi'} \quad (\Theta_0,\Sigma,\Pi',P,pc+1) \to (\Theta',\Sigma')}{(\Theta,\Sigma,\Pi,P,pc) \to (\Theta',\Sigma')}$$

$$(Ss) \qquad \frac{P[pc] = \mathsf{sync} \quad \Theta_n \neq \emptyset \quad (\Theta_n, \Sigma, (pc', \Theta_0, l, \emptyset) : \Pi, P, l) \rightarrow (\Theta', \Sigma')}{(\Theta, \Sigma, (pc', \emptyset, l, \Theta_n) : \Pi, P, pc) \rightarrow (\Theta', \Sigma')}$$

(SP)

$$\frac{P[pc] = \mathsf{sync} \qquad (\Theta_n, \Sigma, (\neg, \emptyset, \neg, \Theta_0) : \Pi, P, pc + 1) \to (\Theta', \Sigma')}{(\Theta_0 \cup \Theta_n, \Sigma, \Pi, P, pc) \to (\Theta', \Sigma')}$$

$$\frac{P[\mathit{pc}] = \mathtt{jump}\; l \qquad (\Theta, \Sigma, \Pi, P, l) \to (\Theta', \Sigma')}{(\Theta, \Sigma, \Pi, P, \mathit{pc}) \to (\Theta', \Sigma')}$$

$$(\text{IT}) \qquad \frac{P[\mathit{pc}] = \iota}{\iota \notin \{ \texttt{stop}, \texttt{bnz}, \texttt{bz}, \texttt{sync}, \texttt{jump} \}} \qquad \frac{(\Theta, \Sigma, \iota) \to (\Theta', \Sigma')}{(\Theta, \Sigma, \Pi, P, \mathit{pc}) \to (\Theta'', \Sigma'')} \qquad \frac{(\Theta', \Sigma', \Pi, \mathit{pc} + 1, \Theta'', \Sigma'')}{(\Theta, \Sigma, \Pi, P, \mathit{pc}) \to (\Theta'', \Sigma'')}$$

Fig. 6. The semantics of  $\mu$ -SIMD: control flow operations. For conciseness, when two hypotheses hold we use the topmost one. We do not give evaluation rules for bnz, because they are similar to those given for bz.

nates if P[pc] = stop. The semantics of conditionals is more elaborate. Upon reaching bz v, l we evaluate v in the local memory of each active PE. If  $\sigma(v) \neq 0$  for every PE, then Rule BF moves the flow to the next instruction, i.e., pc+1. Similarly, if  $\sigma(v)=0$ for every PE, then in Rule BT we jump to the instruction at P[l]. However, if we get distinct values for different PEs, then the branch is divergent. In this case, in Rule BD we execute the PEs in the "else" side of the branch, keeping the other PEs in the synchronization stack to execute them later. The **push** function in Figure 5 updates this stack. Even the non-divergent branch rules update the synchronization stack, so that, upon reaching a barrier, i.e, a sync instruction, we do not get stuck trying to pop a node. In Rule SS, if we arrive at the barrier with a group  $\Theta_n$  of PEs waiting to execute, then we resume their execution at the "then" branch, keeping the previously active PEs into hold. Finally, if we reach the barrier without any PE waiting to execute, in Rule SP we synchronize the "done" PEs with the current set of active PEs, and resume execution at the next instruction after the barrier. Notice that, in order to avoid deadlocks, we must assume that a branch and its corresponding synchronization barrier determine a single-entry-single-exit region in the program's CFG [Ferrante et al. 1987, p.329].

Figure 7 shows the semantics of the rest of  $\mu$ -SIMD's instructions. A tuple  $(t, \sigma, \Sigma, \iota)$  denotes the execution of an instruction  $\iota$  by a PE  $(t, \sigma)$ . All the active PEs execute the same instruction at the same time. We model this behavior by showing, in Rule TL, that the order in which different PEs process  $\iota$  is immaterial. Thus, an instruction

$$(\text{MM}) \quad \frac{\Sigma(v) = c}{\Sigma \vdash v = c} \qquad (\text{MT}) \quad t, \sigma \vdash \mathsf{T}_{id} = t \qquad (\text{MV}) \quad \frac{v \neq \mathsf{T}_{id} \quad \sigma(v) = c}{t, \sigma \vdash v = c}$$

$$(\text{TL}) \quad \frac{(t, \sigma, \Sigma, \iota) \to (\sigma', \Sigma') \quad (\Theta, \Sigma', \iota) \to (\Theta', \Sigma'')}{(\{(t, \sigma)\} \cup \Theta, \Sigma, \iota) \to (\{(t, \sigma')\} \cup \Theta', \Sigma'')}$$

$$(\text{CT}) \quad (t, \sigma, \Sigma, v = c) \to (\sigma \setminus [v \mapsto c], \Sigma)$$

$$(\text{AS}) \quad \frac{t, \sigma \vdash v' = c}{(t, \sigma, \Sigma, v = v') \to (\sigma \setminus [v \mapsto c], \Sigma)}$$

$$(\text{LD}) \quad \frac{t, \sigma \vdash v_x = c_x \quad \Sigma \vdash c_x = c}{(t, \sigma, \Sigma, v = \downarrow v_x) \to (\sigma \setminus [v \mapsto c], \Sigma)}$$

$$(\text{ST}) \quad \frac{t, \sigma \vdash v_x = c_x \quad t, \sigma \vdash v = c}{(t, \sigma, \Sigma, \uparrow v_x = v) \to (\sigma, \Sigma \setminus [c_x \mapsto c])}$$

$$(\text{AT}) \quad \frac{t, \sigma \vdash v_x = c_x \quad \Sigma \vdash c_x = c \quad c' = c + 1}{(t, \sigma, \Sigma, v \xleftarrow{a} v_x + 1) \to (\sigma \setminus [v \mapsto c'], \Sigma \setminus [c_x \mapsto c'])}$$

$$(\text{BP}) \quad \frac{t, \sigma \vdash v_2 = c_2 \quad t, \sigma \vdash v_3 = c_3 \quad c_1 = c_2 \otimes c_3}{(t, \sigma, \Sigma, v_1 = v_2 \oplus v_3) \to (\sigma \setminus [v_1 \mapsto c_1], \Sigma)}$$

Fig. 7. The operational semantics of  $\mu$ -SIMD: data and arithmetic operations.

such as v = c causes every active PE to assign the integer c to its local variable v. The rest of the rules in Figure 7 are oblivious to the multi-threaded nature of  $\mu$ -SIMD. In other words, they determine the semantics of each instruction executed by a single PE. We use the notation  $f[a \mapsto b]$  to denote the updating of function f; that is,  $\lambda x.x = b$ a?b:f(x). Rule CT describes the assignment of a constant to a variable. Similarly, Rule AS describes the copy of data from a variable v' to a variable v. Rule LD shows the loading of data from the common memory  $\Sigma$  into a PE's local variable v. In this rule, the contents of variable  $v_x$  are used to index  $\Sigma$ . Stores are defined by Rule ST. An instruction such as  $\uparrow v_x = v$  copies the contents of v into the cell of  $\Sigma$  indexed by the contents of  $v_x$ . The store instruction might lead to a data-race, i.e., two PEs trying to write different data on the same location in the shared vector. In this case, the result is undefined due to Rule TL. We guarantee atomic updates via  $v \stackrel{a}{\leftarrow} v_x + 1$ , which reads the value at  $\Sigma(\sigma(v_x))$ , increments it by one, and stores it back. This result is also copied to  $\sigma(v)$ , as we see in Rule AT. Rule BP defines the execution of typical binary operations, such as addition and multiplication. The symbol  $\otimes$  denotes different operators, which we interpret according to the semantics usually seen in arithmetics.

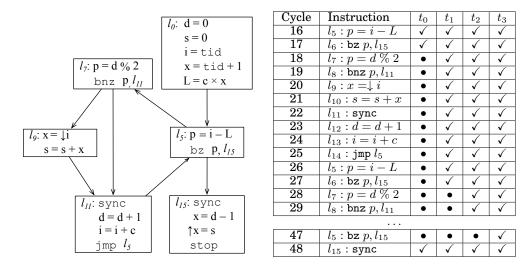

Figure 8 (left) shows the kernel sumTriangle from Figure 1 written in  $\mu$ -SIMD. To keep the figure clean, we only show the label of the first instruction present in each basic block. This program will be executed by many threads, in lock-step; however, in this case, threads perform different amounts of work: the PE that has  $T_{id}=n$  will visit n+1 cells of the matrix. After a thread leaves the loop, it must wait for the others. Processing resumes once all of them synchronize at label  $l_{15}$ . At this point, each thread sees a different value stored at  $\sigma(d)$ , which has been incremented  $T_{id}+1$  times. Figure 8 (Right) illustrates divergences via a snapshot of the execution of the program seen on the left. We assume that our running program contains four threads:  $t_0,\ldots,t_3$ . When visiting the branch at label  $l_6$  for the second time, in cycle 17, the predicate p is 0 for

13:12 Sampaio et al.

Fig. 8. (Left) Example of a  $\mu$ -SIMD program. (Right) Snapshot of the execution trace of the  $\mu$ -SIMD program on the left. If a thread t executes an instruction at a cycle j, we mark the entry (t,j) with the symbol  $\checkmark$ . Otherwise, we mark it with the symbol  $\bullet$ .

thread  $t_0$ , and 1 for the other PEs. In face of this divergence,  $t_0$  is pushed onto  $\Pi$ , the stack of waiting threads, while the other threads continue executing the loop. When the branch is visited a third time, a new divergence takes place in cycle 27, this time causing  $t_1$  to be stacked for later execution. This pattern will happen again with thread  $t_2$ , although we do not show it in Figure 8. Once  $t_3$  leaves the loop, all the threads synchronize via the sync instruction at label  $t_{15}$ , and resume lock-step execution.

#### 3.2. Gated Static Single Assignment Form

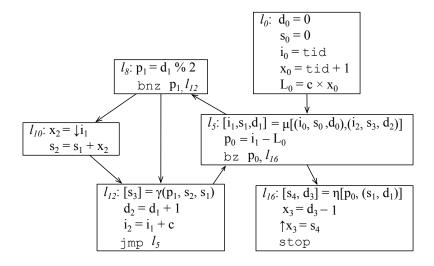

To better handle control dependences between program variables, we work with  $\mu$ -SIMD programs in *Gated Static Single Assignment* form [Ottenstein et al. 1990; Tu and Padua 1995] (GSA). Figure 9 shows the program in Figure 8 converted to GSA form. This intermediate program representation differs from the well-known *Static Single Assignment* [Cytron et al. 1991] form because it augments  $\phi$ -functions with the predicates that control them. The GSA form uses three special instructions:  $\mu$ ,  $\gamma$  and  $\eta$  functions, defined as follows [Ottenstein et al. 1990]:

- — $\gamma$  functions represent the joining point of different paths created by an "if-then-else" branch in the source program. The instruction  $v = \gamma(p, o_1, o_2)$  denotes  $v = o_1$  if p, and  $v = o_2$  if  $\neg p$ ;

- $\mu$  functions, which only exist at loop headers, merge initial and loop-carried values. The instruction  $v=\mu(o_1,o_2)$  represents the assignment  $v=o_1$  in the first iteration of the loop, and  $v=o_2$  in the others.

- $\eta$  functions represent values that leave a loop. The instruction  $v = \eta(p, o)$  denotes the value of o assigned in the last iteration of the loop controlled by predicate p.

We use Tu and Padua's [1995] almost linear time algorithm to convert a program into GSA form. According to this algorithm,  $\gamma$  and  $\eta$  functions exist at the post-dominator of the branch that controls them. A label  $l_p$  post-dominates another label l if, and only if, every path from l to the end of the program goes through  $l_p$ . Fung et al. [2007] have shown that re-converging divergent PEs at the immediate post-dominator of the divergent branch is nearly optimal with respect to maximizing hardware

Fig. 9. The program from Figure 8 converted into GSA form.

utilization. Although Fung *et al.* have discovered situations in which it is better to do this re-convergence past  $l_p$ , they are very rare. Thus, we assume that each  $\gamma$  or  $\eta$  function encodes an implicit synchronization barrier, and omit the sync instruction from labels where any of these functions is present. These special functions are placed at the beginning of basic blocks. We use Appel's parallel copy semantics [Appel 1998] to evaluate these functions, and we denote these parallel copies using Hack's matrix notation [Hack and Goos 2006]. For instance, the  $\mu$  assignment at  $l_5$ , in Figure 9 denotes two parallel copies: either we perform  $[i_1, s_1, d_1] = (i_0, s_0, d_0)$ , in case we are entering the loop for the first time, or we do  $[i_1, s_1, d_1] = (i_2, s_3, d_2)$  otherwise.

We work on GSA-form programs because this intermediate representation allows us to transform control dependences into data dependences when calculating uniform variables. Given a program P, a variable  $v \in P$  is data dependent on a variable  $u \in P$  if either P contains some assignment instruction P[l] that defines v and uses u, or v is data dependent on some variable w that is data dependent on u. For instance, the instruction  $p_0 = i_1 - L_0$  in Figure 9 causes  $p_0$  to be data dependent on  $i_1$  and  $i_2$ . On the other hand, a variable v is control dependent on  $i_2$  if  $i_3$  if, and only if, the branch at  $i_3$  is taken. This last event depends on the predicate  $i_4$  hence, we say that  $i_4$  is control dependent on  $i_4$  in the GSA-form program of Figure 9, we have that variable  $i_4$  has been replaced by several new variables  $i_4$  if  $i_4$  in the instruction  $i_4$  is assignment at  $i_4$  in the predicate control dependence from  $i_4$  to  $i_4$  in the predicate controlling the branch at  $i_4$  in the predicate controlling the branch at  $i_4$  in the predicate controlling the branch at  $i_4$  in the calculation  $i_4$  in the predicate controlling the branch at  $i_4$  in the properties  $i_4$  in the predicate controlling the branch at  $i_4$  in the properties  $i_4$  in the predicate controlling the branch at  $i_4$  in the properties  $i_4$  in

#### 3.3. The Simple Divergence Analysis

The simple divergence analysis reports if a variable v is *uniform* or *divergent*. We say that a variable is uniform if it meets the condition in Definition 3.1. Otherwise it is divergent. In order to find statically a conservative approximation of the set of uniform variables in a program we solve the constraint system in Figure 10. In Figure 10 we

13:14 Sampaio et al.

$$v = c \times \mathsf{T}_{id} \qquad [\mathsf{TIDD}] \qquad [v] = D \qquad v = \oplus o \qquad [\mathsf{ASGD}] \qquad [v] = [o]$$

$$v \overset{a}{\leftarrow} v_x + c \qquad [\mathsf{ATMD}] \qquad [v] = D \qquad v = c \qquad [\mathsf{CNTD}] \qquad [v] = U$$

$$v = \gamma[p, o_1, o_2] \qquad [\mathsf{GAMD}] \qquad \frac{\llbracket p \rrbracket = U}{\llbracket v \rrbracket = \llbracket o_1 \rrbracket \wedge \llbracket o_2 \rrbracket} \qquad v = \eta[p, o] \qquad [\mathsf{ETAD}] \qquad \frac{\llbracket p \rrbracket = U}{\llbracket v \rrbracket = \llbracket o_1 \rrbracket} \qquad \frac{\llbracket p \rrbracket = U}{\llbracket v \rrbracket = \llbracket o_1 \rrbracket}$$

$$v = o_1 \oplus o_2 \qquad [\mathsf{GBZD}] \qquad \llbracket v \rrbracket = \llbracket o_1 \rrbracket \wedge \llbracket o_2 \rrbracket$$

$$v = \gamma[p, o_1, o_2] \text{ or } v = \eta[p, o] \qquad [\mathsf{PDVD}] \qquad \frac{\llbracket p \rrbracket = D}{\llbracket v \rrbracket = D}$$

$$v = \mu[o_1, \dots, o_n] \qquad [\mathsf{RMUD}] \qquad \llbracket v \rrbracket = \llbracket o_1 \rrbracket \wedge \llbracket o_2 \rrbracket \wedge \dots \wedge \llbracket o_n \rrbracket$$

Fig. 10. Constraint system used to solve the simple divergence analysis.

let  $\llbracket v \rrbracket$  denote the abstract state associated with variable v. This abstract state is an element of the lattice U > D. This lattice is equipped with a meet operator  $\wedge$ , such that  $a \wedge a = a$ , and  $U \wedge D = D \wedge U = D$ . We optimistically initialize the abstract state of every variable with U. In Figure 10 we use  $o_1 \oplus o_2$  for any binary operator, including addition and multiplication. Similarly, we use  $\oplus o$  for any unary operator, including loads.

*Definition* 3.1 (*Uniform Variables*). A variable  $v \in P$  is uniform if, and only if, for any state  $(\Theta, \Sigma, \Pi, P, pc)$ , and any  $\sigma_i, \sigma_j \in \Theta$ , we have that  $i, \sigma_i \vdash v = c$  and  $j, \sigma_j \vdash v = c$ .

**Sparse Implementation.** If we see the inference rules in Figure 10 as transfer functions, then we can bind them directly to the nodes of the source program's dependence graph. Furthermore, none of these transfer functions is an identity function, as a quick inspection of the rules in Figure 10 reveals. Therefore, our analysis admits a sparse implementation, as defined by Choi et al. [1991]. In the words of Choi et al., sparse dataflow analyses are convenient in terms of space and time because (i) useless information is not represented, and (ii) information is forwarded directly to where it is needed. Because the lattice used in Figure 10 has height two, that constraint system can be solved in two iterations of a unification-based algorithm. Moreover, if we initialize every variable's abstract state to U, then the analysis admits a straightforward solution based on graph reachability. As we see from the constraints, a variable v is divergent if either it (i) is assigned a factor of  $T_{id}$ , as in Rule TIDD; or (ii) it is defined by an atomic instruction, as in Rule ATMD; or (iii) it is the left-hand side of an instruction that uses a divergent variable. From this observation, we let a data dependence graph G that represents a program P be defined as follows: for each variable  $v \in P$ , let  $n_v$  be a vertex of G, and if P contains an instruction that defines variable v, and uses variable u, then we add an edge from  $n_u$  to  $n_v$ . To find the divergent variables of P, we start from  $n_{tid}$ , plus the nodes that represent variables defined by atomic instructions, and mark every variable that is reachable from this set of nodes.

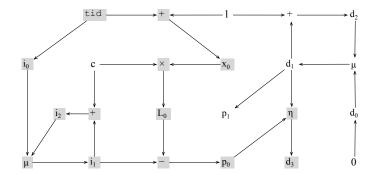

Moving on with our example, Figure 11 shows the data dependence graph created for the program in Figure 9. Surprisingly, we notice that the instruction  $\operatorname{bnz} p_1, l_{12}$  cannot cause a divergence, even though the predicate  $p_1$  is data dependent on variable  $d_1$ , which is created inside a divergent loop. Indeed, variable  $d_1$  is not divergent, although the variable  $p_0$  that controls the loop is. We prove the non-divergence of  $d_1$  by induction on the number of loop iterations. In the first iteration, every thread sees  $d_1 = d_0 = 0$ . In subsequent iterations we have that  $d_1 = d_2$ . Assuming that at the n-th iteration every thread still in the loop sees the same value of  $d_1$ , then, the assignment  $d_2 = d_1 + 1$

Fig. 11. The dependence graph created for the program in Figure 9. We only show the *program slice* [Weiser 1981] that creates variables  $p_1$  and  $d_3$ . Divergent variables are colored gray.

concludes the induction step. Nevertheless, variable d is divergent outside the loop. In this case, we have that d is renamed to  $d_3$  by the  $\eta$ -function at  $l_{16}$ . This  $\eta$ -function is data-dependent on  $p_0$ , which is divergent. That is, once the PEs synchronize at  $l_{16}$ , they might have re-defined  $d_1$  a different number of times. Although this fact cannot cause a divergence inside the loop, divergences might still happen outside it.

THEOREM 3.2. Let P be a  $\mu$ -SIMD program, and  $v \in P$ . If ||v|| = U, then v is uniform.

PROOF. The proof is a structural induction on the constraint rules used to derive ||v|| = U:

- —Rule CNTD: by Rule CT, in Figure 7, we have that  $\sigma_i(v) = c$  for every i.

- —Rule ASGD: if  $[\![o]\!] = U$ , then by induction we have that  $\sigma_i(o) = c$  for every i. By Rule AS in Figure 7 we have that  $\sigma_i(v) = \sigma_i(o)$  for every i.

- Rule GBZD: if  $\llbracket o_1 \rrbracket = U$  and  $\llbracket o_2 \rrbracket = U$ , by induction we have  $\sigma_i(o_1) = c_1$  and  $\sigma_i(o_2) = c_2$  for every i. By Rule BP in Figure 7 we have that  $\sigma_i(v) = c_1 \oplus c_2$  for every i.

- —Rule GAMD: if  $[\![p]\!] = U$ , then by induction we have that  $\sigma_i(p) = c$  for every i. By Rules BT or BF in Figure 7 we have that all the PEs branch to the same direction. Thus, by the definition of  $\gamma$ -function, v will be assigned the same value  $o_i$  for every thread. We then apply the induction hypothesis on  $o_i$ .

- Rule ETAD: similar to the proof for Rule GAMD.

####

#### 3.4. Divergence Analysis with Affine Constraints

The previous analysis is not precise enough to point that the loop in the kernel avgSquare (Figure 1) is non-divergent. In this section we fix that omission by equipping the simple divergence analysis with the capacity to associate affine constraints with variables. Let C be the lattice formed by the set of integers  $\mathbb Z$  augmented with a top element  $\top$  and a bottom element  $\bot$ , plus a meet operator  $\land$ . Given  $\{c_1,c_2\}\subset \mathbb Z$ , Figure 12 defines the meet operator, and the abstract semantics of  $\mu$ -SIMD's multiplication and addition. Notice that in Figure 12 we do not consider  $\top \times a$  or  $\top + a$ , for any  $a \in C$ . This is safe because (i) we are working only with strict programs, i.e., programs in SSA form in which every variable is defined before being used, (ii) we process the instructions in a pre-order traversal of the program's dominance tree, (iii) in a SSA form program, the definition of a variable always dominates every use of it [Budimlic

13:16 Sampaio et al.

Fig. 12. Abstract semantics of the meet, multiplication and addition operators used in the divergence analysis with affine constraints. We let  $c_i \in \mathbb{Z}$ .

et al. 2002]. (iv) upon definition, as we shall see in Figure 13, every variable receives an abstract value different from  $\top$ .

We let  $c_1 \wedge c_2 = \bot$  if  $c_1 \neq c_2$ , and  $c \wedge c = c$  otherwise. Similarly, we let  $c \wedge \bot = \bot \wedge c = \bot$ . Notice that C is the lattice normally used in constant propagation; hence, for a proof of monotonicity, see Aho et al. [2006, p.633-635]. We define A as the product lattice  $C \times C$ . If  $(a_1, a_2)$  are elements of A, we represent them using the notation  $a_1 T_{id} + a_2$ . We define the meet operator of A as follows:

$$(a_1\mathsf{T}_{id} + a_2) \wedge (a_1'\mathsf{T}_{id} + a_2') = (a_1 \wedge a_1')\mathsf{T}_{id} + (a_2 \wedge a_2')$$

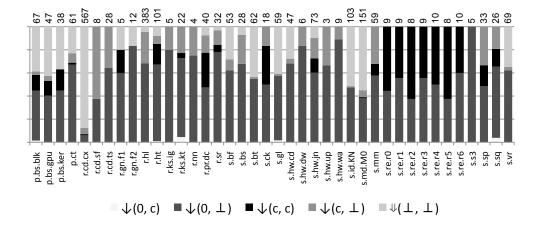

We let the constraint variable  $[\![v]\!] = a_1\mathsf{T}_{id} + a_2$  denote the abstract state associated with variable v. We determine the set of divergent variables in a  $\mu$ -SIMD program P via the constraint system seen in Figure 13. Initially we let  $[\![v]\!] = (\top, \top)$  for every v defined in the text of P, and  $[\![c]\!] = (0,c)$  for each  $c \in \mathbb{Z}$ .

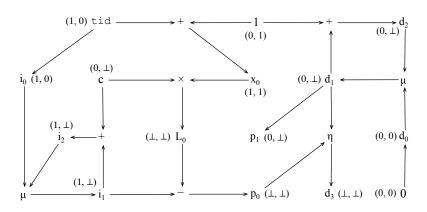

Because our underlying lattice has height two, and we are using a product lattice with two sets, the propagation of control flow information is guaranteed to terminate in at most five iterations [Nielson et al. 2005]. Each iteration is linear on the size of the dependence graph, which might be quadratic on the number of program variables, if we allow  $\gamma$  and  $\mu$  functions to have any number of parameters. Nevertheless, we show in Section 5 that our analysis is linear in practice. As an example, Figure 14 illustrates the application of the new analysis on the dependence graph first seen in Figure 11. Each node has been augmented with its abstract state, i.e., the results of the divergence analysis with affine constraints. This abstract state tells if the variable is uniform or not, as we prove in Theorem 3.3. Furthermore, if the processing elements see v as the same affine function of their thread identifiers, e.g.,  $v = c_1 T_{id} + c_2$ ,  $c_1$ ,  $c_2 \in \mathbb{Z}$ , then we say that v is affine.

THEOREM 3.3. If  $\llbracket v \rrbracket = 0$   $T_{id} + a, a \in C$ , then v is uniform. If  $\llbracket v \rrbracket = c$   $T_{id} + a, a \in C, c \in \mathbb{Z}, c \neq 0$ , then v is affine.

PROOF. The proof is by structural induction on the rules in Figure 13. We will show a few cases:

- CNTA: a variable initialized with a constant is uniform, given Rule CT in Figure 7. Rule CNTA assigns the coefficient zero to the abstract state of this variable.

- SUMA: if the hypothesis holds by induction, then we have four cases to consider. (i) If  $v_1$  and  $v_2$  are uniform, then  $\llbracket v_1 \rrbracket = 0\mathsf{T}_{id} + a_1$ , and  $\llbracket v_2 \rrbracket = 0\mathsf{T}_{id} + a_2$ , where  $a_1, a_2 \in C$ . Thus,  $\llbracket v \rrbracket = (0+0)\mathsf{T}_{id} + (a_1+a_2)$ . By hypothesis,  $a_1$  and  $a_2$  have the same value for every processing element, and so do  $a_1+a_2$ . (ii) If  $v_1$  and  $v_2$  are affine, then we have  $\llbracket v_1 \rrbracket = c_1\mathsf{T}_{id} + a_1$ , and  $\llbracket v_2 \rrbracket = c_2\mathsf{T}_{id} + a_2$ , where  $c_1, c_2 \in \mathbb{Z}$  and  $a_1, a_2 \in C$ . Thus,  $\llbracket v \rrbracket = (c_1+c_2)\mathsf{T}_{id} + (a_1+a_2)$ , and the result holds for the same reasons as in (i). (iii) It is possible that  $c_1=-c_2$ ; thus,  $c_1+c_2=0$ . Because  $v_1$  and  $v_2$  are affine, each variable is made off a factor of  $\mathsf{T}_{id}$  plus a constant parcel a for every PE. The sum of these constant parcels, e.g.,  $a_1+a_2$  is still constant for every PE; hence, v is uniform. (iv) Finally, if one of the operands of the sum is divergent, then v will be divergent,

$$v = c \times \mathsf{T}_{id} \quad [\mathsf{TIDA}] \qquad [v] = c\mathsf{T}_{id} + 0 \qquad v = v' \quad [\mathsf{ASGA}] \qquad [v] = [v']$$

$$v \xleftarrow{a} v_x + c \quad [\mathsf{ATMA}] \qquad [v] = \Delta \mathsf{T}_{id} + \Delta \qquad v = c \quad [\mathsf{CNTA}] \qquad [v] = 0 \mathsf{T}_{id} + c$$

$$v = \oplus o \quad [\mathsf{GUZA}] \qquad [v] = 0 \mathsf{T}_{id} + a \qquad v = \oplus o \quad [\mathsf{GUNA}] \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad a_1 \neq 0 \\ \boxed{v} = \Delta \mathsf{T}_{id} + \Delta \qquad v = \oplus o \quad [\mathsf{GUNA}] \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad a_1 \neq 0 \\ \boxed{v} = \Delta \mathsf{T}_{id} + \Delta \qquad v = \phi \quad [\mathsf{CDNA}] \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad a_1 \neq 0 \\ \boxed{v} = \Delta \mathsf{T}_{id} + \Delta \qquad v = \phi \quad [\mathsf{CDNA}] \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad a_1 \neq 0 \\ \boxed{v} = \Delta \mathsf{T}_{id} + \Delta \qquad v = \phi \quad [\mathsf{CDNA}] \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad a_1 \neq 0 \\ \boxed{v} = \Delta \mathsf{T}_{id} + \Delta \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad [v] = a_2 \mathsf{T}_{id} + a_2 \qquad [v] = a_1 \mathsf{T}_{id} + a_1 \qquad [v] = a_1 \mathsf{T}_{id} + a_1 \qquad [v] = a_1 \mathsf{T}_{id} + a_1 \qquad [v] = a_2 \mathsf{T}_{id} + a_2 \qquad a_1 \times a_2 \neq 0 \qquad [v] = a_1 \mathsf{T}_{id} + a_1 \qquad [v] = a_1 \mathsf{T}_{id} + a_1 \qquad [v] = a_1 \mathsf{T}_{id} + a_2 \qquad [v] = a_2 \mathsf{T}_{id} + a_2 \qquad [v] =$$

Fig. 13. Constraint system used to solve the divergence analysis with affine constraints of degree one.

Fig. 14. Results of the divergence analysis with affine constraints for the program slice seen in Figure 11.

given our abstract sum operator defined in Figure 12. These four cases abide by the semantics of addition, if we replace  $\oplus$  by + in Rule BP of Figure 7.

— ETAA: we know that p is uniform; hence, by either Rule BT or BF in Figure 7, PEs reach the end of the loop at the same time. If o is uniform, it has the same value for

ACM Transactions on Programming Languages and Systems, Vol. 35, No. 4, Article 13, Publication date: January 2014.

13:18 Sampaio et al.

every PE at the end of the loop. If it is affine, it has the same  $T_{id}$  coefficient at that moment. Thus, v is either uniform or affine, by Rule AS from Figure 7.

— GAMA: by hypothesis we know that  $\llbracket v \rrbracket = 0\mathsf{T}_{id} + a$ . Thus, by induction we know that p is uniform. A branch on a uniform variable leads all the threads on the same path, due to either Rule BT or BF in Figure 7. There are then three cases to consider, depending on  $\llbracket o_1 \rrbracket$  and  $\llbracket o_2 \rrbracket$ . (i) If  $\llbracket o_1 \rrbracket = 0\mathsf{T}_{id} + c_1$  and  $\llbracket o_2 \rrbracket = 0\mathsf{T}_{id} + c_2$ , then by induction these two variables are uniform, and their meet is also uniform. (ii) If  $\llbracket o_1 \rrbracket = c\mathsf{T}_{id} + c_1$  and  $\llbracket o_2 \rrbracket = c\mathsf{T}_{id} + c_1$ , then by induction these two variables are affine, with the same coefficient of  $\mathsf{T}_{id}$ . Their meet is also affine with a  $\mathsf{T}_{id}$  coefficient equal to c. (iii) Otherwise, we conservatively assign  $\llbracket v \rrbracket$  the  $\bot$  coefficient as defined by the  $\land$  operator.

The other rules are similar.  $\Box$

The divergence analysis with affine constraints subsumes the simple divergence analysis of Section 3.3, as Corollary 3.4 shows.

COROLLARY 3.4. If the simple divergence analysis says that variable v is uniform, then the divergence analysis with affine constraints says that v is uniform.

PROOF. Because both analyses use the same intermediate representation, they work on the same program dependence graph. In Section 3.3's analysis, v is uniform if it is a function of only uniform variables, e.g.,  $v = f(v_1, \ldots, v_n)$ , and every  $v_i, 1 \le i \le n$  is uniform. From Theorem 3.2, we know that if  $[v_i] = 0$ T $_{id} + c_i$  for every  $i, 1 \le i \le n$ , then v is uniform.  $\square$

Is there a case for higher-degree polynomials? Our analysis, as well as constant propagation, are a specialization of a framework that we call the divergence analysis with polynomial constraints. In the general case, we let  $[v_i] = a_n T_{id}^n + a_{n-1} T_{id}^{n-1} + \dots + a_1 T_{id} + a_0$ , where  $a_i \in C, 1 \le i \le n$ . Addition and multiplication of polynomials follow the usual algebraic rules. The rules in Figure 13 use polynomials of degree one. Constant propagation uses polynomials of degree zero. Our polynomials of degree one are a special instance of Miné's octagons [Miné 2006]. The main different between our abstract domain, and Miné's, is that while octagons can relate any two variables, we only relate variables with the thread identifier, hence obtaining a more efficient implementation. Similarly, higher degree polynomials are a special case of Cousot and Halbwachs polyhedrons [Cousot and Halbwachs 1978], an abstract domain that can track algebraic relations between any group of program variables.

There are situations in which polynomials of degree two let us find more affine variables. The extra precision comes out of Theorem 3.5. Consider, for instance, the program in Figure 15, which assigns to each processing element the task of initializing the rows of a matrix  $\mathbf{m}$  with one's. The degree-one divergence analysis would conclude that variables  $i_0, i_1$  and  $i_2$  are divergent. However, the degree-two analysis finds that the highest coefficient of any of these variables is zero; thus flagging them as affine functions of  $\mathbf{T}_{id}$ . In our benchmarks the degree-2 analysis marked 39 more variables, out of almost 10,000, as affine, when compared to the degree-1 analysis. We could not gain more precision from polynomials of degree three or higher.

THEOREM 3.5. If  $\llbracket v \rrbracket = 0$   $T_{id}^2 + a_1 T_{id} + a_0, a_1, a_0 \in C$ , then v is affine function of  $T_{id}$ .

PROOF. This proof is also a structural induction on the extended constraint rules for polynomials of degree two. We omit it, because it is very similar to the proof of Theorem 3.3.  $\Box$

```

(a_1, a_0) | (a_2, a_1, a_0)

void s(int* m, int n) {

(0, 0, \bot)

(0, \perp)

int i_0 = n * tid, k = (tid + 1) * n;

while (i_1 = \gamma(i_0, i_2); i_1 < k) {

(\perp,0)

i_0

(0, \perp, 0)

m[i_1] = 1;

(\bot, \bot)

(0, \perp, \perp)

i_2 = i_1 + 1;

(\bot, \bot)

(0, \perp, \perp)

i_2

(0, \perp, \perp)

```

Fig. 15. An example where a higher degree polynomial improves the precision of the simple affine analysis. We let  $a_2\mathsf{T}_{id}^2+a_1\mathsf{T}_{id}+a_0=(a_2,a_1,a_0)$ .

#### 4. DIVERGENCE AWARE REGISTER ALLOCATION

Similar to traditional register allocation, we are interested in finding storage area to the values produced during program execution. However, in the context of graphics processing units, we have different types of memory to consider:

- **Registers:** these are the fastest storage regions. A traditional GPU might have a very large number of registers, for instance, one streaming multiprocessor (SM) of a GTX 580 GPU has 32,768 registers. However, running 1,536 threads at the same time, this SM can afford at most 20 registers to each thread in order to achieve maximum hardware occupancy.

- **Shared memory:** this fast memory is addressable by each thread in flight, and usually is used as a scratchpad memory. It must be used carefully, to avoid common parallel hazards, such as data races. Henceforth we will assume that accessing data in the shared memory is less than 3 times slower than in registers.

- —**Local memory:** this off-chip memory is private to each thread. Modern GPUs provide a cache to the local memory, which is as fast as the shared memory. We will assume that a cache miss is 100 times more expensive than a hit.

- Global memory: this memory is shared among all the threads in execution, and is located in the same chip area as the local memory. The global memory is also cached. We shall assume that it has the same access times as the local memory.

As we have seen, the local and the global memories might benefit from a cache, which uses the same access machinery as the shared memory. Usually this cache is small: the GTX 570 has 64KB of fast memory, out of which 48KB are given to the shared memory by default, and only 16KB are used as a cache. This cache area must be further divided between global and local memories.

Given this hardware configuration, we see that the register allocator has the opportunity to keep a single image per warp of any spilled value that is uniform. This optimization is very beneficial in terms of time. According to Ryoo et al. [2008], the shared memory has approximately the same latency as an on-chip register access, whereas a non-cached access to the local memory is 200-300 times slower. A divergence aware register allocator has a second advantage: it tends to improve memory locality. The GPU's cache space is severely limited, as it has to be partitioned among the massive number of threads running concurrently. In fact, the capacity of the cache might be much lower than the capacity of the register file itself [Nickolls and Dally 2010]. When moving non-divergent variables to the shared memory, we only need to store one instance per warp, rather than one instance per thread. Thus, the divergence aware register allocator may provide up to a 32-fold improvement in cache locality.

13:20 Sampaio et al.

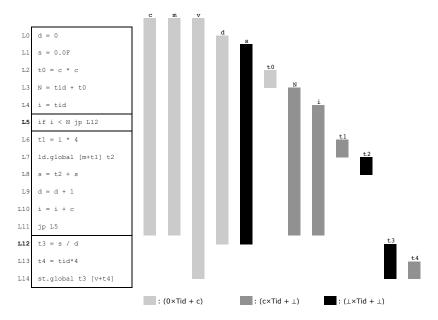

Fig. 16. The register allocation problem for the kernel avgSquare in Figure 1.

Figure 16 shows the instance of the register allocation problem that we obtain from the kernel avgSquare in Figure 1. There are many ways to model register allocation. In this paper we use an approach called  $linear\ scan$  [Poletto and Sarkar 1999]. Thus, we linearize the control flow graph of the program, finding an arbitrary ordering of basic blocks, in such a way that each  $live\ range$  is seen as an interval. We use bars to represent the live ranges of the variables. The live range of a variable is the collection of program points where that variable is alive. A variable v is alive at a program point p if v is used at a program point p that is reachable from p on the control flow graph, and v is not redefined along this path. The colors of the bars represent the abstract state of the variables, as determined by the divergence analysis.

If the register pressure exceeds the number of available registers at a given program point p, then our linear scan chooses one of the live variables and maps it into memory, a process called *spilling*. We spill the variable that has the farthest use from p, following Belady's heuristics [Belady 1966]. Current register allocators for graphics processing units place spilled values in the local memory. Figure 17 illustrates this approach. In this example, we assume a warp with two processing elements, each one having access to three registers. Given this configuration, variables s, d and N had to be spilled. Thus, each of these variables receive a slot in local memory. The spilled data must be replicated once for each processing element, as each of them has a private local memory area. Accessing data from the local memory is an expensive operation, because this region is off-chip. To mitigate this problem, modern GPUs provide a cache to the local and to the global memories. However, because the number of threads using the cache is large – in the order of thousands – and the cache itself is small, e.g., 16KBs, cache misses are common. In the next section we show that it is possible to improve this situation considerably, by taking the results of the divergence analysis into consideration.

|     | Program             | register file |     |    |    | local |    |   |     |   |   |     | global |   |    |   |   |   |

|-----|---------------------|---------------|-----|----|----|-------|----|---|-----|---|---|-----|--------|---|----|---|---|---|

|     |                     |               | PE0 |    |    | PE1   |    |   | PE0 |   |   | PE1 |        |   | 'n |   |   |   |

|     |                     | r0            | r1  | r2 | r0 | r1    | r2 |   | 0   | 1 | 2 | 0   | 1      | 2 |    | 0 | 1 | 2 |

| L0  | d = 0               |               |     |    |    |       |    |   |     |   |   |     |        |   |    | С | m | v |

| L1  | st.local d [1]      | d             |     |    | d  |       |    |   |     |   |   |     |        |   |    | С | m | v |

| L2  | s = 0.0F            | d             |     |    | d  |       |    |   |     | d |   |     | d      |   |    | С | m | v |

| L3  | st.local s [0]      | d             | s   |    | d  | s     |    |   |     | d |   |     | d      |   |    | С | m | v |

| L4  | ld.global [0] c     | d             | s   |    | d  | s     |    |   | s   | d |   | s   | d      |   |    | С | m | v |

| L5  | t0 = c * c          | d             | s   | С  | d  | s     | С  |   | s   | d |   | s   | d      |   |    | С | m | v |

| L6  | N = tid + t0        | t0            | s   | С  | t0 | s     | С  |   | s   | d |   | s   | d      |   |    | С | m | v |

| L7  | st.local N [2]      | t0            | s   | N  | t0 | s     | N  |   | s   | d |   | s   | d      |   |    | С | m | v |

| L8  | i = tid             | t0            | s   | N  | t0 | s     | N  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L9  | ld.local [2] N      | i             | s   | N  | i  | s     | N  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L10 | if i < N jp L24     | i             | s   | N  | i  | s     | N  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L11 | t1 = i * 4          | i             | s   | N  | i  | s     | N  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L12 | ld.global [1] m     | i             | s   | t1 | i  | s     | t1 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L13 | ld.global [m+t1] t2 | i             | m   | t1 | i  | m     | t1 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L14 | ld.local [0] s      | i             | m   | t2 | i  | m     | t2 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L15 | s = t2 + s          | i             | s   | t2 | i  | s     | t2 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L16 | st.local s [0]      | i             | s   | t2 | i  | s     | t2 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L17 | ld.local [1] d      | i             | s   | t2 | i  | s     | t2 |   | s   | d | N | s   | d      | N |    | С | m | V |

| L18 | d = d + 1           | i             | s   | d  | i  | S     | d  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L19 | st.local d [1]      | i             | s   | d  | i  | S     | d  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L20 | ld.global [0] c     | i             | s   | d  | i  | S     | d  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L21 | i = i + c           | i             | s   | С  | i  | S     | С  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L22 | jp L9               | i             | s   | С  | i  | s     | С  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L23 | ld.local [1] d      | i             | s   | С  | i  | s     | С  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L24 | t3 = s / d          | i             | s   | d  | i  | s     | d  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L25 | t4 = tid*4          | t3            | s   | d  | t3 | s     | d  |   | s   | d | N | s   | d      | N |    | С | m | V |

| L26 | ld.global [2] v     | t3            | t4  | d  | t3 | t4    | d  |   | S   | d | N | s   | d      | N |    | С | m | V |

| L27 | st.global t3 [v+t4] | t3            | t4  | V  | t3 | t4    | V  | ] | s   | d | N | S   | d      | N |    | С | m | V |

Fig. 17. Traditional register allocation, with spilled values placed in local memory.

#### 4.1. Adapting a Traditional Register Allocator to be Divergence Aware

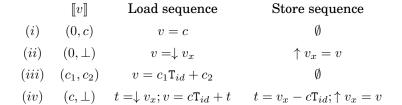

To accommodate the notion of local memory in  $\mu$ -SIMD, we augment its syntax with two instructions to manipulate this memory. An instruction such as  $v=\Downarrow v_x$  denotes a load of the value stored at local memory address  $v_x$  into v. The instruction  $\uparrow v_x=v$  represents a store of v into the local memory address  $v_x$ . The table in Figure 18 shows how we replace loads and stores to the local memory by more efficient instructions. The figure describes a re-writing system: we replace loads-to and stores-from local memory by the sequences in the table, whenever the variable has the abstract state in the second column. In addition to moving uniform values to shared memory, in this paper we propose a form of Briggs's style rematerialization [Briggs et al. 1992] that suits SIMD machines. The lattice that we use in Figure 13 is equivalent to the lattice used by Briggs  $et\ al$ . in their rematerialization algorithm. Thus, we can naturally perform rematerialization for an uniform variable which has statically known-values, i.e.,  $[v_x] = (0\mathsf{T}_{id},c)$ , as in line (i) of Figure 18 or  $[v_x] = (c_1\mathsf{T}_{id},c_2)$ , as in line (ii). For the other uniform or affine variables we can move the location of values from the local memory to the shared memory, as we show in lines (ii) and (iv).

Figure 19 shows the code that we generate for the program in Figure 16. The most apparent departure from the allocation given in Figure 17 is the fact that we have moved to shared memory some information that was originally placed in local memory. Variable d has been shared among different threads. Notice how the stores at labels L1 and L19 in Figure 17 have been replaced by stores to shared memory in labels L1 and L20 of Figure 19. Similar changes happened to the instructions that load d from

13:22 Sampaio et al.