## Precise Modelling of Instruction Cache Behaviour

Sidharta Andalam, Roopak Sinha, Partha S. Roop, Alain Girault, Jan Reineke

#### ▶ To cite this version:

Sidharta Andalam, Roopak Sinha, Partha S. Roop, Alain Girault, Jan Reineke. Precise Modelling of Instruction Cache Behaviour. [Research Report] RR-8214, INRIA. 2013, 62 p. hal-00781566

## HAL Id: hal-00781566 https://inria.hal.science/hal-00781566

Submitted on 27 Jan 2013

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Precise Modelling of Instruction Cache Behaviour

Sidharta Andalam, Roopak Sinha, Partha S. Roop, Alain Girault, Jan Reineke

RESEARCH REPORT

N° 8214

January 2013

Project-Teams SPADES

## Precise Modelling of Instruction Cache Behaviour

Sidharta Andalam, Roopak Sinha, Partha S. Roop, Alain Girault, Jan Reineke

Project-Teams SPADES

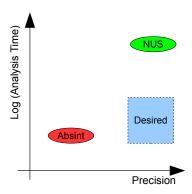

Abstract: Safety critical real-time applications in aviation, automotive and industrial automation have to guarantee not only the functionality, but also the timeliness of the results. Here, a deadline is associated with the software tasks, and a failure to complete prior to this deadline could lead to a catastrophic consequences. Hence, for the correctness of real-time systems, it is essential to be able to compute the worst case execution time (WCET) of the tasks in order to guarantee their deadlines. However, the problem of WCET analysing is difficult, because of processors use cache-based memory systems that vary memory access time significantly. Any pessimistic estimation of the number of cache hits/misses will result in loose precision of the WCET analyses, which could lead to over use of hardware resources. In this paper, we present a new approach for statically analysing the behaviour of instructions on a direct mapped cache. The proposed approach combines binary representation and a new abstraction that reduces the analysis time without sacrificing the precision. This is unlike the existing cache analysing approaches where either precision or scalability (analysis time) is sacrificed. Experimental results are presented that demonstrate the practical applicability of this analysis.

**Key-words:** Instruction Cache Analysis, WCET, worst case execution analysis, direct mapped cache.

This project is partially funded by the SPADES project

RESEARCH CENTRE

GRENOBLE – RHÔNE-ALPES

inovallee 655 avenue de l'Europe Montbonnot 38334 Saint Ismier Cedex

## Modélisation précise du comportement du cache d'instructions

Les applications temps-réel critiques en avionique, automobile, et informatique industrielle doivent garantir non seulement leur fonctionnalité mais aussi le respect des contraintes temporelles. Dans ce domaine, une date limite est associée à chaque tâche logicielle, et un échec dans le respect d'une telle date limite peut conduire à des conséquences catastrophiques. Aussi, pour la correction des applications temps-réel, il est essentiel d'être capables de calculer le temps d'exécution au pire cas (WCET) des tâches logicielles, de façon à garantir le respect des dates limites. Toutefois, l'analyse du WCET est difficile, parce que les processeurs utilisent des mémoires cache (antémémoire) qui font varier significativement les temps d'accès à la mémoire. Toute estimation pessimiste du nombre de succès et d'échecs des accès au cache va entraîner une perte de précision de l'analyse de WCET, et donc une utilisation non-optimale des ressources matérielles. Dans cet article, nous présentons une nouvelle approche pour analyser statiquement le comportement des instructions avec une mémoire cache à correspondance préétablie (« direct-mapped cache »). Notre approche combine une représentation binaire et une nouvelle abstraction qui réduit le temps d'analyse sans perdre de précision. Ceci diffère des approches existante dans lesquelles on doit faire le choix entre la précision et le passage à l'échelle. Les résultats expérimentaux que nous présentons démontrent l'utilité de notre nouvelle analyse de caches.

Mots-clés : Analyse du cache instructions, WCET, analyse du temps d'exécution au pire cas, cache à correspondance préétablie.

## Contents

| 1        | Intr | roduction                                                                    | 4          |

|----------|------|------------------------------------------------------------------------------|------------|

| <b>2</b> | Cac  | che Analysis                                                                 | 6          |

|          | 2.1  | Cache model                                                                  | 6          |

|          | 2.2  | Cache states                                                                 | 8          |

|          | 2.3  | Analysing the cache states                                                   | 10         |

|          |      | 2.3.1 Illustration                                                           | 10         |

|          | 2.4  | Cache analysis problem                                                       | 11         |

| 3        | The  | e NUS approach                                                               | 13         |

|          | 3.1  | The NUS join function                                                        | 13         |

|          | 3.2  | The NUS transfer function                                                    | 14         |

|          | 3.3  | Fixed point computation                                                      | 15         |

| 4        | The  | e Absint approach                                                            | 19         |

|          | 4.1  | Abstract cache states                                                        | 19         |

|          | 4.2  | The Absint join function                                                     | 20         |

|          | 4.3  | The Absint transfer function                                                 | 21         |

|          | 4.4  | Fixed-point computation                                                      | 22         |

|          |      | 4.4.1 Illustration of the fixed-point algorithm                              | 23         |

|          |      | 4.4.2 Mapping an abstract cache state to cache states                        | 25         |

|          | 4.5  | Calculating cache misses                                                     | 26         |

| 5        | Cor  | nparison between NUS and Absint approaches                                   | 28         |

| 6        | Pro  | posed approach                                                               | 30         |

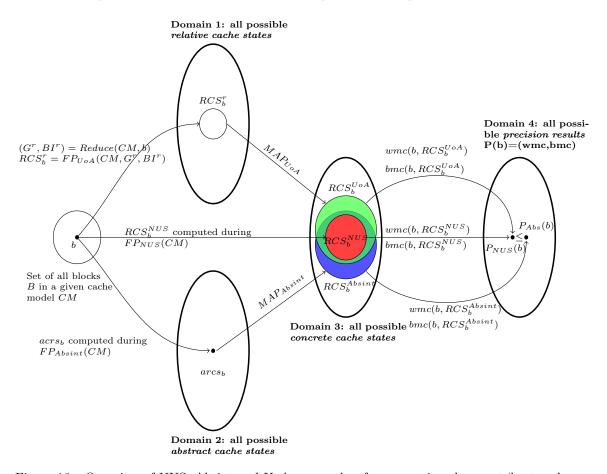

|          | 6.1  | Overview                                                                     | 30         |

|          | 6.2  | Reducing the CFG and abstracting the instructions                            | 31         |

|          | 6.3  | Relative cache states                                                        | 35         |

|          | 6.4  | UoA transfer function                                                        | 37         |

|          | 6.5  | Computing all possible reaching relative cache states of the reference block | 39         |

|          | 6.6  | Calculating cache misses for the reference block                             | 43         |

|          | 6.7  | Reducing the analysis time                                                   | 44         |

| 7        | Cor  | nparisons between the NUS, Absint and UoA approaches                         | 49         |

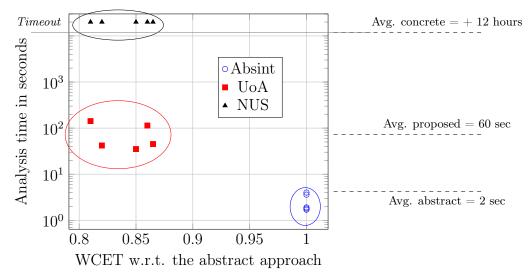

|          | 7.1  | Mapping relative cache states of $b_{ref}$ to concrete cache states          | 49         |

|          | 7.2  | Comparison between the approaches                                            | 53         |

| 8        | Disc | cussion                                                                      | <b>5</b> 6 |

| 9        | Ben  | schmarking and Experimental Results                                          | 57         |

|          | 9.1  | Benchmarking                                                                 | 57         |

| 10       | Cor  | nelusions                                                                    | 58         |

#### 1 Introduction

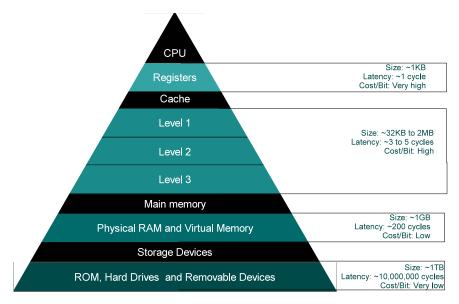

Most applications can benefit significantly from a fast, cheap and large memory. However in reality, as the memory gets faster, the cost increases and the size decreases. For example, caches are fast and small, but expensive compared to hard disks which are slow, cheap and large. This restriction has forced the computer architects to physically place the fast and smaller memories close to the processor. In contrast, slower and larger memories are placed further away from the processor. Hence, we have a hierarchy of memories as presented in Figure 1. Memory hierarchies are effective because, during an execution of a program, the frequency of accessing storage units at any particular level is more than the frequency of accessing storage at the next lower level. Hence, the next level storage units can be slower. The overall effect is a large memory unit that is very cost effective.

Figure 1: Memory hierarchy

In embedded systems, as the application complexity is growing continuously, the complexity of the underlying memory hierarchy is also increasing. For example, for a simple automatic door control, the computation is very simple and hence a memory architecture with only registers and main memory could meet the requirements. In contrast, applications in automotive industry (such as engine control unit) are much more complicated and would require a complex memory hierarchy [22].

After registers, caches are the next nearest memory to the processor. They are used for temporary storage of instructions, such that future requests can be processed much faster. They act as a bridge between the fast processors and the slower main memory. Caches are effective, because of the following two principles:

- 1. Temporal locality: Memory locations that are accessed recently are likely to be accessed again, e.g., cycle through instructions of a loop.

- 2. Spatial locality: Memory locations that are close to the locations that are currently accessed are likely to be accessed soon, e.g., reference to instructions in sequence.

When a processor requests the cache for data at a location in the main memory, the cache first checks it's memory contents. If the requested data is in the cache (cache hit), the data is sent to the processor. Otherwise, if the data is not in the cache (cache miss), it is copied from the main memory into the cache and then forwarded to the processor. However, during this copy, if the cache is already full, a replacement policy will decide which location of the cache memory is to be replaced by the new data. The performance of a cache is measured by the number of cache misses (or cache hits). Thus, the goal of the replacement policy is to reduce the number of cache misses. There are several policies and some are architecture specific. The cache architectures are either classified as set-associative or direct mapped caches [5]. For a set associative cache, each location of the main memory is mapped to more than one location in the cache memory. In general the following three policies are used during replacement [21]:

- Least recently used (LRU): replaces the least recently accessed memory location.

- First in first out (FIFO): replaces the memory that has been in the cache for the longest amount of time.

- Pseudo-LRU (PLRU): is a binary tree based approximation of the LRU policy. The history of the access define the structure of the tree and the leaves represent the cache lines. For more details refer to [15].

In contrast, for a direct mapped caches, the replacement policy is very simple. Each location of the main memory is mapped to exactly only one location in the cache memory. This policy does not require any history bits and updating, unlike the replacement policies mentioned above. Most embedded applications use Direct Mapped Caches because of their simple design, low complexity (requires small hardware), and low power consumption. It also simplifies the static analysis that is required for hard real time systems.

Alternatively, to achieve timing predictability and to simplify static timing analysis, there has been a shift towards predictable memory hierarchy for hard real-time systems. One such approach is to use a cache locking mechanism [14]. In this approach, the contents of the cache are decided at compile time and are loaded prior to the execution of the program. This simplifies the analysis and provides a predictable platform. However, this significantly reduces the throughput. This simple approach has been further extended to dynamically reload and lock the cache at statically determined control points [13]. This increases the throughput at the expense of the analysis time.

Recently, scratchpad memories (SPMs) have been introduced as an alternative to caches for predictable systems. In SPMs, the allocation and replacement decisions are made by software, guided by the decisions made at compile time. In contrast, the allocation and replacement of traditional caches are done dynamically, guided by the history of the cache states. Recent work on SPMs focuses on developing software allocation algorithms [16], [19], [3] and/or designing tailored architectures with SPMs [16], [10], [11].

In this paper, we focus only on single core processors with direct mapped caches. We present two prominent related works in analysing direct mapped caches. In the NUS approach [12], the problem of computing all possible cache states is mapped to a problem of computing the least fixed point. This approach performs very precise analysis. However, as the program size increases, this approach experiences state-space explosion and the analysis time grows exponentially. To address this issue, the same research group has formulated a new probabilistic approach for modelling cache behaviour [9]. It is used for design space explorations and reduces overall analysis time by exploiting the structural similarities among related cache configurations. Experimental results indicate that their new probabilistic based analysis is 24 to 3855 times faster than simulation. Also, they have employed the idea of cache conflict graphs (CCF) in [7]. This

work analyses one cache line at a time and presents a more scalable approach. However, it abstracts the relation between cache lines, thus, sacrificing precision. Also, it would be interesting to quantitatively compare the precision and the analysis time with other existing techniques, like the Absint approach [4], [15]. The Absint approach performs an abstraction based WCET analysis by sacrificing precision for scalability. As a result, it is the preferred approach for analysing cache based architectures for industrial applications [18], [2], [17].

The organisation of this paper is as follows. In Section 2, we formalise the cache analysis problem. In Sections 3 and 4 we present two prominent related works in analysing direct mapped caches. First, the NUS approach [12] is presented in Section 3. Second, the Absint approach [4] is presented in Section 4. We compare both approaches in Section 5. In Section 6, we present the proposed cache analysis approach (UoA approach), along with some optimisations. In Section 7 we present a comparisons between all three (NUS, Absint and UoA) approaches. Finally, in Section 8 we conclude the chapter with some discussions.

## 2 Cache Analysis

#### 2.1 Cache model

The first step in the cache analysis is the creation of a suitable cache model. Before we formally define the cache model, we provide an illustrative description. Cache analysis requires the following information:

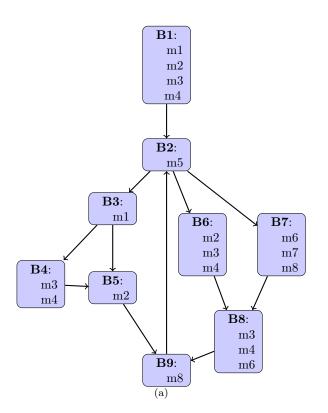

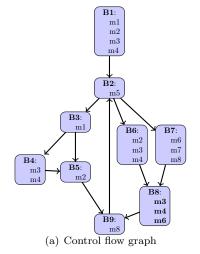

- 1. A control flow graph (CFG). This is extracted from the binaries of an embedded program [20]. The CFG contains basic blocks which are annotated with instructions that are executed in this block. An example CFG is presented in Figure 2(a). It contains nine basic blocks, B1 to B9. The basic block B1 is annotated with four instructions m1, m2, m3 and m4 that are executed in this basic block. The entire program (CFG) has eight different instructions m1 to m8.

- 2. A mapping of all instructions to cache lines. Since, the number of instructions in a program is usually greater than the number of cache lines, more than one instruction is mapped to the same cache line. For the example CFG (presented in Figure 2(a)), we present the instructions to cache lines mapping using Figure 2(b). The cache has four cache lines  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$ . Instructions  $m_1$  and  $m_5$  are both mapped to the cache line  $c_0$ . This means that during program execution, cache line  $c_0$  can contains either  $m_1$  or  $m_2$  or nothing (when empty).

The above information can be used to map the instructions in each basic block to the cache lines. E.g., for block B1, instructions m1, m2, m3, m4 are mapped to cache lines  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$  respectively (as presented in Figure 2(b)). If we enforce  $C = \{c_0, c_1, c_2, c_3\}$ , the set of cache lines, to be an ordered set, then the instructions of B1 can be described using a vector [m1, m2, m3, m4] where the index of the  $i^{th}$  element corresponds to the  $i^{th}$  cache line. E.g., the  $2^{nd}$  element m2 corresponds to the  $2^{nd}$  cache line  $c_1$ . Similarly, the basic block B2 has only one instruction m5 that is mapped to cache line  $c_0$  and the rest of the cache lines have no instructions (represented using the symbol  $\mp$ ). Hence, the instructions of B2 can be described using the vector  $[m5, \mp, \mp, \mp]$ .

For the rest of this section, we formalise the cache model, the behaviour of the cache, and the cache analysis problem.

**Definition 1** (Cache model). The cache model for a given program is defined as a tuple  $CM = \langle I, C, CI, G, BI \rangle$ , where:

| Cache | Instructions |

|-------|--------------|

| line  |              |

| $c_0$ | m1,m5        |

| $c_1$ | m2,m6        |

| $c_2$ | m3,m7        |

| $c_3$ | m4,m8        |

| (b    | )            |

Figure 2: (a) A simple control flow graph consisting of nine basic blocks (B1 to B9) and the instructions that are accessed during execution of the basic block. (b) Mapping of instructions on to four cache lines ( $c_0$  to  $c_3$ ).

- I is a finite set of instructions and |I| is the total number of instructions in the program.

- $C = \{c_0, c_1, \dots, c_{N-1}\}$  is an ordered set of cache lines. N = |C| is the total number of cache lines.

- $CI: C \to 2^I$  is the cache line to instructions mapping function. For a cache line  $c \in C$ , CI(c) is a subset of I representing the set of instructions that are mapped to cache line c. We restrict CI such that for any two cache lines  $c_k$  and  $c_l$ ,  $CI(c_k) \cap CI(c_l) = \emptyset$  and further  $\bigcup_{k=0}^{N-1} CI(c_k) = I$  i.e., CI partitions I into N partitions, where each partition represents the instructions mapped to a given cache line.

Also, we define the instruction to cache line mapping function  $IC: I \to C$ . For an instruction  $i \in C$ , IC(i) = c, where  $i \in CI(c)$ .

- G is a directed graph  $G = \langle B, b_{init}, E \rangle$  where:

- B is a finite set of basic blocks.

- $-b_{init} \in B$  is the initial basic block.

- $-E \subseteq B \times B$  is the set of edges. For short hand,  $(b_0, b_1) \in E$  is represented using  $b_0 \to b_1$ .

•  $BI: B \to (I \cup \{\mp\})^N$  is the block to instruction mapping function. For any given basic block  $b \in B$ ,  $BI(b) = [inst_0, inst_1, ..., inst_{N-1}]$ . For any  $i \in [0, N-1]$ , BI(b)[i] is the instruction mapped to the  $i^{th}$  cache line  $c_i \in C$ . Thus,  $BI(b)[i] \in CI(c_i) \cup \{\mp\}$ .

#### Illustration of the cache model

Using Figure 2, we illustrate the cache model  $CM = \langle I, C, CI, G, BI \rangle$  as follows:

- $I = \{m1, m2, m3, m4, m5, m6, m7, m8\}$  and |I| = 8.

- $C = \{c_0, c_1, c_2, c_3\}$  is an ordered set and N = |C| = 4.

- $CI(c_0) = \{m1, m5\}$  and  $IC(m1) = c_0$ .

- $G = (B, b_0, E)$  where  $B = \{B1, B2, \dots, B9\}, b_0 = B1$  and  $E = \{(B1, B2), (B2, B3), \dots\}.$

- BI(B1) = [m1, m2, m3, m4] and BI(B1)[1] = m2. Similarly,  $BI(B8) = [\mp, m6, m3, m4]$  and  $BI(B8)[0] = \mp$ , which represents that block B9 does not contain any instruction that is mapped to the cache line  $c_0$ . The order of the instructions in the vector are based on the mapping of the instructions to the cache lines. It is not based on the order of the instructions specified by the programmer, i.e.,  $BI(B8) \neq [\mp, m3, m4, m6]$ .

#### 2.2 Cache states

We describe the behaviour of the cache by first describing cache states. A cache state describes the instructions in the cache at some instance in time. It is described as a vector  $[inst_0, inst_1, \ldots, inst_{N-1}]$  where each  $inst_i$  represents the instructions contained in cache line  $c_i \in C$ .

For the example CFG shown in Figure 2(a), when the program starts executing, we assume the cache is empty. This is represented as the cache state  $cs_{\top} = [\top, \top, \top, \top]$ . Instructions are loaded into the cache as the basic blocks are executed (starting from the initial block). E.g., after executing the basic block B1 the cache state is cs = [m1, m2, m3, m4].

Generally, the status of the cache may be unknown when a block is being analysed. We used the symbol  $\bot$  to represent an unknown instruction in a cache line. E.g.,  $cs = [\bot, \bot, \bot, \bot]$  represents the status of every cache line is unknown. This notion of unknown cache state is used during the cache analysis and is explained later in Section 3.

Note that a cache state has identical structure to the block to instructions mapping function BI(b) for any block  $b \in B$ . E.g., The cache state after executing B1 is cs = [m1, m2, m3, m4] and also, BI(B1) = [m1, m2, m3, m4]. The cache state represents the instructions in the cache, while the function BI represents the instructions that are executed by the basic block. This identical structure simplifies the cache analysis as simple comparison between vectors allows us to analyse the cache misses. This is later explained in later part of this section.

We now define the cache states.

**Definition 2** (Cache state). A Cache state  $cs \in (I \cup \{\top, \bot\})^N$ , can be described as a vector  $[inst_0, inst_1, \ldots, inst_{N-1}]$  where each element cs[i] represents an instruction in cache line  $c_i$ . Further, we restrict cache states such that, for any  $i \in [0, N-1]$ ,  $cs[i] \in CI(c_i) \cup \{\top, \bot\}$ . We denote  $cs_{\top} = [\top, \ldots, \top]$  as a empty cache state where all the elements of the vector are  $\top$ . Similarly, we denote  $cs_{\bot} = [\bot, \ldots, \bot]$  as a unknown cache state where all the elements of the vector are  $\bot$ . Also, the set of all cache states is defined as CS.

Before we illustrate cache states, we introduce two key terms essential to cache analysis. For any basic block b, the Reaching cache states (RCS) represent the set of cache states prior to the

execution of a basic block and the Leaving cache states (LCS) represent the set of cache states after the execution of the basic block. We denote the RCS of a basic block b as  $RCS_b$  and the LCS of a basic block b as  $LCS_b$ .

#### Illustration of cache states

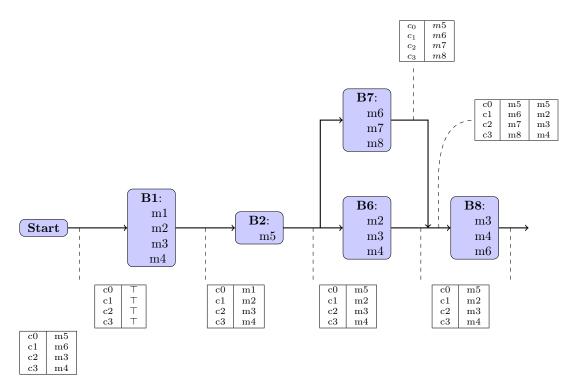

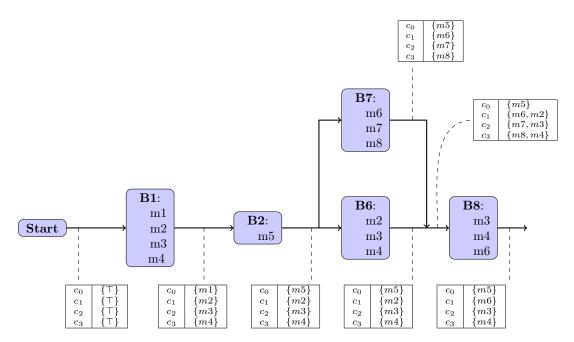

Figure 3: Illustration of the cache states.

Using Figure 3, we illustrate reaching/leaving cache states of a block. Initially the cache is empty. The state of the cache is  $cs_{\top} = [\top, \top, \top, \top]$ . After the execution of block B1, cache lines  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$  will contain instructions m1, m2, m3, m4 respectively, resulting in the state [m1, m2, m3, m4]. The cache state  $[\top, \top, \top, \top]$  is the state of the cache prior to the execution of the basic block B1. Thus,  $RCS_{B1} = \{ [\top, \top, \top, \top, \top] \}$  is the set of reaching cache states of block B1. Similarly,  $LCS_{B1} = \{ [m1, m2, m3, m4] \}$  is the set of leaving cache states of block B1.

The leaving cache state of B1 is also the reaching cache state of B2,  $RCS_{B2} = LCS_{B1}$ . Block B2 has only one instruction m5, and is mapped to cache line  $c_0$ . Thus, the previous instruction in line  $c_0$  will be replaced by m5. Since the  $RCS_{B2} = \{[m1, m2, m3, m4]\}$ , after executing the instructions in B2, the resulting leaving cache state is  $LCS_{B2} = \{[m5, m2, m3, m4]\}$ .

Now, the control reaches a branch due to which, it is possible to execute either block B6 or block B7. In this case,  $RCS_{B6} = LCS_{B2} = RCS_{B7}$ . After executing blocks B6 or B7, the state of the cache is either [m5, m2, m3, m4] or [m5, m6, m7, m8].

Block B8 has two incoming edges: from blocks B6 and B7. In this case, in order to compute  $RCS_{B8}$ , we need to join  $LCS_{B6}$  and  $LCS_{B7}$ . There are various approaches to describe this join function [12], [4]. This join function is the key difference between existing approaches and could dictate the precision and the scalability of the cache analysis. Later in this chapter, we formally present several join functions. See the summary in Section 7

For now, we assume the join function is a union over the set of cache states. Thus,  $RCS_{B8} = LCS_{B7} \cup LCS_{B6}$ , resulting in  $RCS_{B8} = \{[m5, m2, m3, m4], [m5, m6, m7, m8]\}$ . After execution of block B8, for both reaching cache states the resulting leaving cache state is [m5, m6, m3, m4]. Thus, the  $LCS_{B8} = \{[m5, m6, m3, m4]\}$ .

#### 2.3 Analysing the cache states

The purpose of cache analysis is to compute the number of cache misses experienced during the execution of every basic block. For example, for block B8 consider the cache state cs = [m5, m2, m3, m4] before executing the block. Since cs[1] = m2, the cache contains the instruction m2 on the cache line  $c_1$ , before executing B8. Now,  $BI(B8) = [\mp, m6, m3, m4]$  and BI(B8)[1] = m6 for cache line  $c_1$ . This means, for cache line  $c_1$ , the cache contains the instruction m2, whereas the block needs to execute m6. Since, we have a mismatch  $(BI(B8)[1] \neq cs[1])$ , B8 has a cache miss during the execution of instruction m6 on the cache line  $c_1$ .

Similarly, since BI(B8)[2] = m3 = cs[2], we have a cache hit. Also,  $BI(B8)[0] = \mp$ , which represents that block B8 does not execute an instruction from cache line  $c_0$ . Therefore, B8 can not have a miss for cache line  $c_0$ , regardless of the content of a reaching cache state. Thus, a cache miss on a cache line  $c_i$  can only occur when the block b has an instruction that can be mapped to a cache line  $c_i$  (i.e.,  $BI(b)[i] \neq \mp$ ) and further the instruction does not match with the instruction in the reaching cache state (i.e.,  $BI(b)[i] \neq cs[i]$ ). Using Definition 20, we define a function that computes the number of cache misses.

**Definition 3** (Miss count). The cache miss function,  $mc : B \times CS \times C \to \{0,1\}$ , where for any block  $b \in B$ , cache state cs and a cache line  $c_i \in C$  with  $i \in [0, N-1]$  is defined as follows:

$$mc(b,cs,c_i) = \left\{ \begin{array}{ll} 1 & :if \ BI(b)[i] \neq \mp \ \land BI(b)[i] \neq cs[i] \\ 0 & :otherwise \end{array} \right.$$

We extend the function mc to return the total number of misses for a block b and a cache state cs as,  $mc: B \times CS \to \mathbb{N}^0$  where,

$$mc(b,cs) = \sum_{i=0}^{N-1} mc(b,cs,c_i)$$

#### 2.3.1 Illustration

Figure 4: Illustration of the function mc

Given a cs = [m5, m2, m3, m4] and  $BI(B8) = [\mp, m6, m3, m4]$ , we now illustrate the mc function using Figure 4. For all cache lines  $c_i \in C$ , the figure shows that there is only one cache miss and it occurs on cache line  $c_1$ , because instruction m2 is present in the reaching cache state cs while the block needs instruction m8. Thus,  $mc(B8, cs, c_1) = 1$ . Similarly,  $mc(B8, cs, c_0) = 0$ ,  $mc(B8, cs, c_2) = 0$  and  $mc(B8, cs, c_3) = 0$ . Hence, mc(B8, cs) = 0 + 1 + 0 + 0 = 1. Thus, only one cache miss occurs during the execution of block B8 for reaching cache state of [m5, m2, m3, m4].

The *mc* function computes the number of cache misses for a given reaching cache state and a basic block. However, if a block has more than one reaching cache states, the number of cache misses can vary. For cache analysis, we are interested in finding the best case and the worst case number of cache misses that may be experienced by a basic block.

**Definition 4** (Worst miss count). We define the function  $wmc: B \times 2^{CS} \to \mathbb{N}^0$  where, for a given block  $b \in B$  and a set  $RCS' \subseteq CS$  such that  $RCS' = \{rcs_1, rcs_2, \dots, rcs_m\}$  and m = |RCS'|,

$$wmc(b, RCS') = MAX(mc(b, rcs_1), \dots, mc(b, rcs_m))$$

**Definition 5** (Best miss count). We define the function  $bmc : B \times 2^{CS} \to \mathbb{N}^0$  where, for a given block  $b \in B$  and a set  $RCS' \subseteq CS$  such that  $RCS' = \{rcs_1, rcs_2, \dots, rcs_m\}$ ,

$$bmc(b, RCS') = MIN(mc(b, rcs_1), \dots, mc(b, rcs_m))$$

#### Illustration of wmc and bmc

Using the reaching caches states for B8 ( $RCS_{B8}$ ), we now illustrate the functions wmc and bmc. Since,  $RCS_{B8}$  contains two cache states of {[m5, m2, m3, m4], [m5, m6, m7, m8]}, using the mc(B8, [m5, m2, m3, m4]) = 1 or mc(B8, [m5, m6, m7, m8]) = 2. Since, the maximum number of misses is 2, thus,  $wmc(B8, RCS_{B8}) = 2$ . Similarly, the function  $bmc(B8, RCS_{B8}) = 1$ .

#### 2.4 Cache analysis problem

The cache analysis problem consists of two sub problems. The first sub problem is to compute all the possible reaching cache states for every basic block in the given cache model. The second sub problem is to compute the number of cache misses in the best case and the worst case, using the reaching cache states computed in sub problem one.

**Definition 6** (Cache Analysis Problem). Given CM, the cache analysis problem can be stated as the computation of:

- 1. All possible  $RCS_b$  for every block  $b \in B$ . We refer to this first problem as sub problem one.

- 2.  $P: B \to \mathbb{N}^0 \times \mathbb{N}^0$ , where for every block  $b \in B$ ,  $P(b) = (wmc(b, RCS_b), bmc(b, RCS_b))$  for all  $b \in B$ . We refer to this second problem as sub problem two.

Different cache analysis approaches differ in how they compute sub problem one (presented in Definition 6). We present two existing approaches, the NUS approach [12] and the Absint approach [4] to solve the cache analysis problem. In Table 1 we present a summary of the symbols and the definitions that are presented so far.

| Symbol/Definition                            | Description                           | Example                                         |

|----------------------------------------------|---------------------------------------|-------------------------------------------------|

| CM                                           | Cache model of a given                | see Section 2.1                                 |

|                                              | program                               |                                                 |

| В                                            | Set of basic blocks                   | $\{B1, B2, \ldots, B9\}$ in Figure 2            |

| I                                            | Set of instruction                    | $\{m1, m2, \ldots, m8\}$ in Figure 2            |

| C                                            | Ordered set of cache                  | $\{c_0, c_1, c_2, c_3\}$ in Figure 2            |

|                                              | lines                                 |                                                 |

| $CI:C \to 2^I$                               | Maps cache line to a set              | $CI(c_0) = \{m1, m5\}$                          |

|                                              | of instructions                       |                                                 |

| $IC:I\to C$                                  | Maps instruction to a                 | $IC(m1) = c_0$                                  |

|                                              | cache line                            |                                                 |

| $BI: B \to (I \cup \{\mp\})^N$               | Maps instructions exe-                | BI(B1) = [m1, m2, m3, m4] then                  |

|                                              | cuted by the block to                 | BI(B1)[0] = m1                                  |

|                                              | cache lines                           |                                                 |

| $BI(b)[i] = \mp$                             | Block $b$ has no instruc-             | $BI(B1) = [\mp, m2, m3, m4]$ then               |

|                                              | tion on cache line $c_i$              | $BI(B1)[0] = \mp$                               |

| cs                                           | Cache state                           | cs = [m1, m2, m3, m4]  and  cs[0] =             |

|                                              |                                       | <u>m1</u>                                       |

| $cs[i] = \top$                               | Cache state has no in-                | $cs[0] = \top$                                  |

|                                              | struction on cache line $c_i$         |                                                 |

| $cs[i] = \bot$                               | Cache state has an un-                | $cs[0] = \bot$                                  |

|                                              | known instruction on                  |                                                 |

|                                              | cache line $c_i$                      |                                                 |

| $cs_{\top}$                                  | Empty cache state                     | $cs = [\top, \top, \top, \top]$                 |

| cs <sub>⊥</sub>                              | Unknown cache state                   | $cs = [\bot, \bot, \bot, \bot]$                 |

| $RCS_b$                                      | Set of reaching cache                 | $RCS_{B8} = \{[m5, m2, m3, m4],$                |

| 7.00                                         | states of block b                     | [m5, m6, m7, m8]                                |

| $LCS_b$                                      | Set of leaving cache                  | $LCS_{B8} = \{[m5, m6, m3, m4]\}$               |

| 7.70                                         | states of block b                     | 770                                             |

| $\mathbb{N}_0$                               | Natural numbers that                  | $\mathbb{N}^0 = \{0, 1, 2, 3, \ldots\}$         |

| $D \sim CC \sim NO$                          | includes zero                         | DI(D0) [- c 2 4] 1                              |

| $mc: B \times CS \to \mathbb{N}^0$           | Computes the number                   | $BI(B8) = [\mp, m6, m3, m4] \text{ and } cs = $ |

|                                              | of cache misses experi-               | [m5, m2, m3, m4] then $mc(B8, cs) =$            |

|                                              | enced by the block for a              | 1                                               |

| $wmc: B \times 2^{CS} \to \mathbb{N}^0$      | given cache state  Computes the maxi- | $wmc(B8, RCS_{B8}) = 2$                         |

| $winc: D \times Z^{-1} \to \mathbb{N}^*$     | mum number of cache                   | $winc(Do, RCS_{B8}) = 2$                        |

|                                              | misses misses                         |                                                 |

| $bmc: B \times 2^{CS} \to \mathbb{N}^0$      | Computes the minimum                  | $bmc(B8, RCS_{B8}) = 1$                         |

| once $D \times Z \longrightarrow \mathbb{N}$ | number of cache misses                | Omc(D0, RCSB8) = 1                              |

|                                              | number of cache illisses              |                                                 |

Table 1: Some of the symbols and the definitions (Illustrated using Figures 3)

## 3 The NUS approach

We first present two functions, *join* and *transfer*, that compute the of reaching/leaving cache states of basic blocks. These two functions are used in the cache analysis algorithm, employed by this approach, to compute all possible reaching cache states of every basic block of a cache model (sub problem 1, Definition 6).

#### 3.1 The NUS join function

The NUS join function describes how to compute the reaching cache states of a basic block when the block has more than one incoming edges. E.g., in Figure 3, the basic block B8 has two incoming edges: from blocks B6 and B7. To compute  $RCS_{B8}$  we need to join  $LCS_{B6}$  and  $LCS_{B7}$ . A simple join function could be described as an union over the sets of reaching cache states, i.e.,  $RCS_{B8} = LCS_{B6} \cup LCS_{B6}$ . However, in the NUS approach, during the computation of the reaching cache states unknown cache states  $(cs_{\perp})$  are introduced as part of the analysis (later explained in Algorithm 1). This introduces spurious cache states that must be removed as described in the NUS approach [12]. Given two cache states  $cs_1$  and  $cs_2$ ,  $cs_1$  is subsumed by  $cs_2$ , if for all cache lines  $c_i$ , the instruction in  $cs_2$  is equal to the instruction in  $cs_1$  ( $cs_2[i] = cs_1[i]$ ) or the instruction in  $cs_1$  at cache line  $c_i$  is unknown  $\perp (\forall i, cs_2[i] = cs_1[i]$  or  $cs_1[i] = \perp$ ). In this case, we can remove  $cs_1$ , as it does not contain any extra information compared to  $cs_2$ .

For example, let  $RCS_b = LCS_1 \cup LCS_2$ , it contains two cache states  $cs_1 = [m1, \bot, \bot, \bot]$  and  $cs_2 = [m1, \bot, m2, \bot]$ . Since  $cs_1$  is subsumed by  $cs_2$ , we can reduce the reaching cache states of b to  $RCS_b = \{[m1, \bot, m2, \bot]\}$ . Also, a cache state  $cs_{\bot} = [\bot, \bot, ..., \bot]$  will always we subsumed by any other cache state. This idea of subsumed cache states is further explained during the fixed point computation (see Section 3.3).

This join function for the NUS approach is defined in Definition 7.

**Definition 7** (NUS join function). The NUS join function is  $J_{NUS}: 2^{CS} \times 2^{CS} \rightarrow 2^{CS}$  where, for any two sets of cache states  $CS_1 \subseteq 2^{CS}$  and  $CS_2 \subseteq 2^{CS}$ ,

$$J_{NUS}(CS_1, CS_2) = CS_1 \cup CS_2 \setminus \{cs_1 \in (CS_1 \cup CS_2) | \exists cs_2 \in (CS_1 \cup CS_2) \land S_{NUS}(cs_1, cs_2)\}$$

$$where, S_{NUS} : CS \times CS \rightarrow \{true, false\} \text{ where, for any } cs_1, cs_2 \in CS,$$

$$S_{NUS}(cs_1, cs_2) = \begin{cases} true & : if \ \forall i \in [0, N-1], cs_2[i] = cs_1[i] \text{ or } cs_1[i] = \bot \\ false & : otherwise \end{cases}$$

| $cs_1$                   | $cs_2$                   | $S_{NUS}(cs_1,cs_2)$ |

|--------------------------|--------------------------|----------------------|

| $[\perp, m2, \perp, m4]$ | $[m5, m2, \bot, m4]$     | true                 |

| $[m5, m2, \perp, m4]$    | $[\perp, m2, \perp, m4]$ | false                |

Table 2: Illustrate the subsumed function  $S_{NUS}$

Using Table 2 we first illustrate the NUS subsumed function  $(S_{NUS})$ . In the first row, given two cache states  $cs_1 = [\bot, m2, \bot, m4]$  and  $cs_2 = [m5, m2, \bot, m4]$ ,  $S_{NUS}(cs_1, cs_2) = true$ . This shows the case when  $cs_1$  is subsumed by a  $cs_2$ . In the second row, given two cache states

| $CS_1$                      | $CS_2$                | $CS_1 \cup CS_2$            | $J_{NUS}(CS_1,CS_2)$        |

|-----------------------------|-----------------------|-----------------------------|-----------------------------|

| $\{[\perp, m2, \perp, m4],$ | $[m5, m2, \bot, m4],$ | $\{[\perp, m2, \perp, m4],$ | $\{[\perp, m2, \perp, m4],$ |

| [m5, m6, m7, m8]            | [m5, m6, m7, m8]      | $[m5, m2, \bot, m4],$       | [m5, m6, m7, m8]            |

|                             |                       | [m5, m6, m7, m8]            |                             |

Table 3: Illustrate the join function  $J_{NUS}$

$cs_1 = [m5, m2, \bot, m4]$  and  $cs_2 = [\bot, m2, \bot, m4]$ ,  $S_{NUS}(cs_1, cs_2) = false$ . This shows the case when  $cs_1$  is not subsumed by  $cs_2$ .

Using Table 3, we illustrate the NUS join function. Given two sets of cache states  $CS_1 = \{[\bot, m2, \bot, m4], [m5, m6, m7, m8]\}$  and  $CS_2 = \{[m5, m2, \bot, m4], [m5, m6, m7, m8]\}$ ,  $CS_1 \cup CS_2 = \{[\bot, m2, \bot, m4], [m5, m2, \bot, m4], [m5, m6, m7, m8]\}$ . As illustrated in first row of Table 2, cache state  $[\bot, m2, \bot, m4]$  is subsumed by  $[m5, m2, \bot, m4]$ . Thus,  $J_{NUS}(CS_1, CS_2) = \{[m5, m2, \bot, m4], [m5, m6, m7, m8]\}$ .

#### 3.2 The NUS transfer function

A transfer function described how a reaching cache state of a basic block is transformed into a leaving cache state, after executing the instructions in the basic block. E.g., in Figure 3, the reaching cache state of block B2 is cs = [m1, m2, m3, m4] and after execution, where the instructions of the block as described by  $BI(B2) = [m5, \mp, \mp, \mp]$ , the leaving cache state of B2 is cs' = [m5, m2, m3, m4]. This transformation can be described as follows. First, if a block b does not have an instructions mapped to a cache line  $c_i$   $(BI(b)[i] = \mp)$ , then after execution of the block, the contents of the cache corresponding to that cache line  $c_i$  remains the same. E.g., basic block B2 has no instruction mapped to the cache line  $c_1$ ,  $(BI(B2)[1] = \mp)$ . Thus, after execution, the leaving cache state has the same instruction as the reaching cache state cs'[1] = m2 = cs[1]. Secondly, if a block has an instruction mapped to a cache line  $(BI(b)[i] \neq \mp)$ , then, after execution of the block, the content of the cache corresponding to that cache line is changed to the instruction executed by the block. E.g., basic block B2 has the instruction m5 mapped to the cache line  $c_0$ ,  $(BI(B2)[0] \neq \mp)$ . Thus, after execution, the leaving cache state has the instruction m5, cs' = m5 = BI(B2)[0]. The transfer function,  $T_{NUS}$ , formalises this transformation as follows.

**Definition 8** (NUS transfer function). The NUS transfer function is  $T_{NUS}: B \times CS \rightarrow CS$  where, for a given basic block  $b \in B$  and a cache state cs,

$$T_{NUS}(b, cs) = cs'$$

where for all cache lines  $c_i \in C$  where  $i \in [0, N-1]$ ,

$$cs'[i] = \begin{cases} cs[i] & : if \ BI(b)[i] = \mp \\ BI(b)[i] & : otherwise \end{cases}$$

#### Illustration of the transfer function $T_{NUS}$

Figure 5 illustrates the operation of the transfer function  $T_{NUS}$ . Given block b, with  $BI(b) = [m5, \mp, \mp, \mp]$ , and a reaching cache state cs = [m1, m2, m3, m4], the leaving cache state  $cs' = T_{NUS}(b, cs)$  is computed as follows.

Figure 5: Illustration of the NUS transfer function

For cache line  $c_0$ , block b requires an instruction m5 on cache line  $c_0$  (BI(b)[0] = m5). Thus, irrespective of the reaching cache state, the leaving cache (cs') contains the instruction m2 on its cache line  $c_0$ , i.e., cs'[0] = m5 = BI(b)[0].

For the cache line  $c_1$ , block b has no instruction mapped to cache line  $c_1$   $(BI(b)[1] = \mp)$ . Thus, the instruction m2 on cache line  $c_1$  in cs (m2 = cs[1]), is copied to the cache line  $c_1$  of the leaving cache state cs' i.e., cs'[1] = m2 = cs[1]. Similarly, block b has no instructions mapped to cache lines  $c_2$  and  $c_3$ , resulting in cs'[2] = m3 = cs[2] and cs'[3] = m4 = cs[3]. Thus, given a block b, with  $BI(b) = [m5, \mp, \mp, \mp]$  and a reaching cache state cs = [m1, m2, m3, m4],  $T_{NUS}(b, cs) = cs' = [m5, m2, m3, m4]$ .

The transfer function, as defined in Definition 8, computes a leaving cache state for a basic block given a reaching cache state. During cache analysis, a block may have a set of reaching cache states. E.g., in Figure 3, block B8 has two reaching cache states,  $RCS_{B8} = \{[m5, m2, m3, m4], [m5, m6, m7, m8]\}$ . Thus, we extend the transfer function to compute a set of leaving cache states for a given set of reaching cache states for a block.

**Definition 9** (Extended NUS transfer function). The NUS transfer function is  $T_{NUS}: B \times 2^{CS} \to 2^{CS}$  where, for a given basic block  $b \in B$  and a set of cache states  $CS \subseteq 2^{CS}$ ,

$$T_{NUS}(b, CS) = CS'$$

where for all cache states  $cs_i \in CS$  where  $i \in [1, |CS|]$ ,

$$CS' = \bigcup_{i=1}^{|CS|} \{T_{NUS}(b, cs_i)\}$$

In Figure 3, block B8 has two reaching cache states  $(RCS_{B8} = \{cs_1, cs_2\})$  where  $cs_1 = [m5, m2, m3, m4]$  and  $cs_2 = [m5, m6, m7, m8]$ . In this case,  $T_{NUS}(B8, \{cs_1, cs_2\}) = \{T_{NUS}(B8, cs_1)\} \cup \{T_{NUS}(B8, cs_2)\}$ . In this example,  $T_{NUS}(B8, cs_1) = [m5, m6, m3, m4]$  and  $T_{NUS}(B8, cs_2) = [m5, m6, m3, m4]$ . Thus,  $T_{NUS}(B8, \{cs_1, cs_2\}) = \{[m5, m6, m3, m4]\} \cup \{[m5, m6, m3, m4]\}$

#### 3.3 Fixed point computation

As described in Definition 6, the cache analysis problem consists of two sub problems. The first sub problem is the computation of all reaching cache states for every block  $b \in B$ . The NUS approach [12] solves this problem using a fixed point computation algorithm presented in Algorithm 1. We will present the NUS solution to the second sub problem following the fixed point algorithm (Algorithm 1).

#### Algorithm 1 Fixed point computation for the NUS approach

```

Input: A cache model CM = \langle I, C, CI, G, BI \rangle

Output: RCS_b for every block b \in B.

1: i = 1 {iteration counter}

2: {Initialise the RCS of all blocks}

3: for each b \in B do

if b = b_0 then

4:

RCS_{b_0}^i = \{cs_\top\}

5:

6:

else

RCS_b^i = \{cs_\perp\}

7:

end if

8:

9: end for

10: repeat

{Compute the set of leaving cache states for all blocks for iteration i}

11:

12:

for each b \in B do

13:

LCS_{b}^{i} = T_{NUS}(b, RCS_{b}^{i})

14:

end for

15:

i = i + 1; {Next iteration}

16:

\{Compute RCS\}

for each b \in B do

17:

if b = b_0 then

18:

RCS_b^i = \{cs_\top\}

19:

20:

else

21:

RCS_b^i = \emptyset

for each LCS_{b'}^i, where (b', b) \in E do

22:

RCS_b^i = J_{NUS}(RCS_b^i, LCS_{b'}^{i-1})

23:

end for

24:

25:

end if

26:

end for

27: until \forall b \in B, RCS_b^i = RCS_b^{i-1} {Termination condition}

28: return RCS_b^i for all b \in B

```

In Algorithm 1, we first initialise the reaching cache states for all blocks (lines 3 to 9, Algorithm 1). Since we assume that initially the state of the cache is empty, on line 5 for the initial block  $b_0$  we set its reaching as  $RCS_{b_0}^i = \{cs_{\top}\}$ . Here, the notation  $RCS_b^i$  represents the reaching cache states of block b in iteration i. E.g.,  $RCS_{b_0}^1$  represents the reaching cache states of block  $b_0$  for iteration 1. For rest of the blocks, the execution of the CFG will impact the state of the cache, the state of the cache is unknown. Thus, on line 7, we set their reaching cache states as  $RCS_b^1 = \{cs_{\bot}\}$ .

After initialisation, we compute the leaving cache states of each block, on lines 11 to 14. We apply the transfer function  $T_{NUS}$  to every block and its corresponding reaching cache states.

The iteration index (i) is incremented (line 15) to signal the start of the next iteration. Next, on lines 16 to 26, the reaching cache states of each block are computed. For the initial block  $b_0$ , we know that the reaching cache state is always empty. Thus, on line 19, we always set its reaching as  $RCS_{b_0}^i = \{cs_{\top}\}$ . For rest of the blocks, on lines 22 to 24, the reaching cache states are computed by looking at the leaving cache states of the predecessors (b') of the block b and using the NUS join function.

The iterative process, repeat-until loop on lines 10 to 27, is repeated until a fixed point is

reached, i.e., if two consecutive iterations have the same sets of reaching cache states for all blocks (line 27).

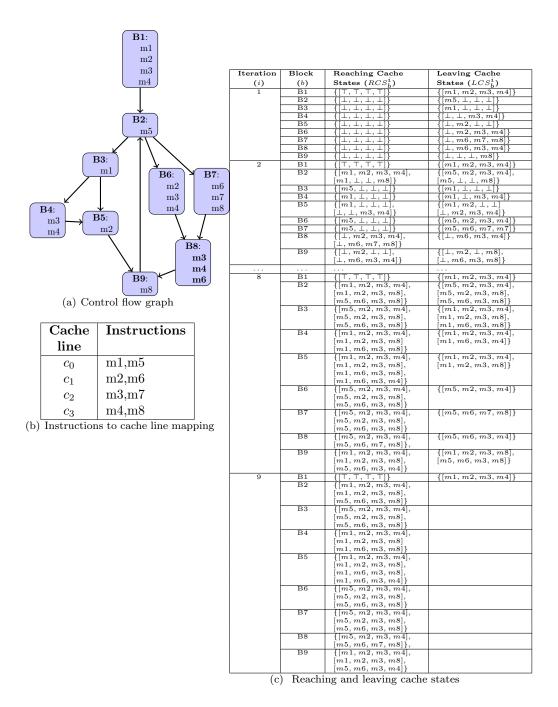

#### Illustration of the fixed point algorithm

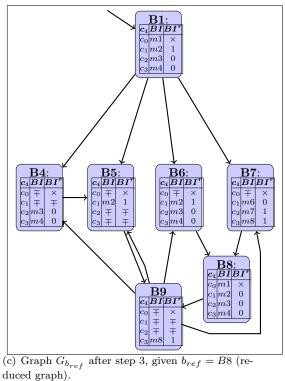

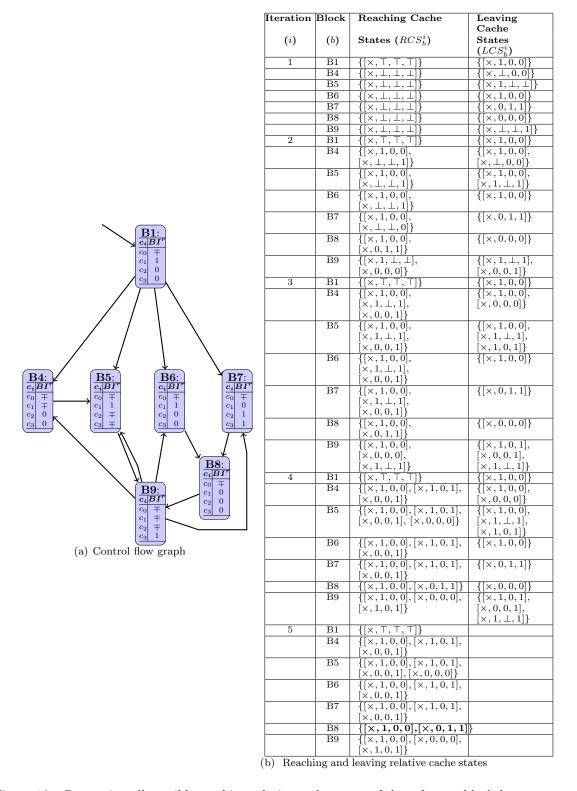

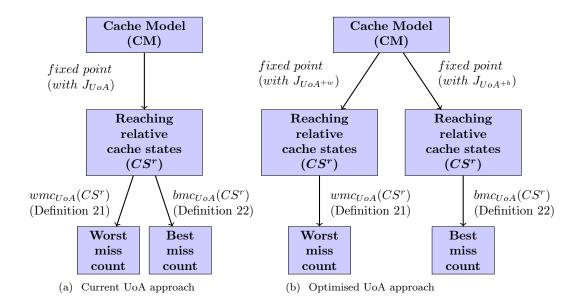

We illustrate the above fixed-point algorithm using the Figure 6. The CFG and the mapping of the instructions to cache lines are presented in Figure 6(a) and Figure 6(b), respectively. These are reproduced from Figure 2. Figure 6(c) presents a table showing the reaching and leaving cache states for all blocks, during each iteration of the algorithm.

We first initialise the reaching cache states for all blocks (lines 3 to 9). For the CFG in Figure 6(a), the initial block is  $b_0$  is B1. Since we assume that initially the state of the cache is empty, on line 5, we set  $RCS_{B1}^1$  as  $\{[\top, \top, \top, \top]\}$ . For rest of the blocks, on line 7, the state of the cache is unknown. Thus, we set their reaching cache states as  $\{[\bot, \bot, \bot, \bot]\}$ .

After initialisation, to compute the leaving cache states of each block, we apply the transfer function  $T_{NUS}$  (lines 11 to 14). For example, in iteration 1 (i=1),  $LCS_{B1}^1 = T_{NUS}(B1, RCS_{B1}^1) = T_{NUS}(B1, \{[\top, \top, \top, \top]\}) = \{[m1, m2, m3, m4]\}$ . For block B2, which has one instruction m5 that is mapped to line  $c_0$ , the leaving cache states  $LCS_{B2}^1 = T_{NUS}(B2, \{[\bot, \bot, \bot, \bot]\}) = \{[m5, \bot, \bot, \bot]\}$ . Similarly, the leaving cache states (column 4) for rest of the blocks are computed for iteration 1 as shown in Figure 6(c).

The iteration index (i) is incremented (line 15) to signal the start of the next iteration (i=2). Next, the reaching cache states of each block, for iteration i=2, are computed (lines 16 to 26). For the initial block B1, we know that the reaching cache state is always  $cs_{\top}$ . Thus, on line 19, we set its reaching cache state as  $RCS_{B1}^2 = \{cs_{\top}\}$ . For rest of the blocks, on lines 22 to 24, the reaching cache states are computed by looking at the leaving cache states of the predecessors (b') of the block b and using the NUS join function. E.g., the predecessors of B2 are B1 and B9,  $b' \in \{B1, B9\}$ , and from the previous iteration (i=1) the  $LCS_{B1}^1 = \{[m1, m2, m3, m4]\}$  and  $LCS_{B9}^1 = \{[\bot, \bot, \bot, m8]\}$ . The process for computing  $RCS_{B2}^2$  is as follows.

- 1. Initialise  $RCS_{B2}^2 = \emptyset$  (line 21).

- 2. Using the NUS join function we process the LCS of each predecessor block (B1, B9), on lines 22 to 24, one at a time (in no particular order). For illustration we will first analyse  $LCS_{B1}^1$  followed by  $LCS_{B9}^1$  as follows.

```

\begin{array}{ll} RCS_{B2}^2 &= J_{NUS}(RCS_{B2}^2, LCS_{B1}^1) \\ &= J_{NUS}(\emptyset, \{[m1, m2, m3, m4]\}) \\ &= \{[m1, m2, m3, m4]\} \\ RCS_{B2}^2 &= J_{NUS}(RCS_{B2}^2, LCS_{B9}^1) \\ &= J_{NUS}(\{[m1, m2, m3, m4]\}, \{[\bot, \bot, \bot, m8]\}) \\ &= \{[m1, m2, m3, m4], [\bot, \bot, \bot, m8]\} \end{array}

```

The iterative process, repeat-until loop on lines 10 to 27, is repeated until a fixed point is reached, i.e., if two consecutive iterations have a same sets of reaching cache states for all blocks (line 27). For our example, it happens at the  $9^{th}$  iteration, where the same sets of reaching cache states are computed for all blocks. As a result, the reaching cache states of the  $9^{th}$  iteration represents all the possible reaching cache states of the program.

Note that during the first iteration, we assumed the reaching cache states for blocks B2 to B9 as unknown ( $\{[\bot, \bot, \bot, \bot]\}$ ), but when we reach the fixed-point, all the unknown cache states are resolved.

Finally, using the functions  $wmc(b, RCS_b^9)$  and  $bmc(b, RCS_b^9)$  (presented in Definitions 4 and Definition 5), the number of cache misses in the worst and the best case is computed. E.g.,

Figure 6: Computing all possible reaching cache states using the NUS approach.

```

in Figure 6(c), at the fix-point, RCS_{B8}^9 = \{[m5, m2, m3, m4], [m5, m6, m7, m8]\} and BI(B8) = [\mp, m6, m3, m4]. Then, mc(B8, [m5, m2, m3, m4]) = 1 and mc(B8, [m5, m2, m3, m4]) = 2. Thus, wmc(B8, RCS_B8^9) = 2 and bmc(B8, RCS_B8^9) = 1.

```

In summary, we have solved the first sub problem of cache analysis (Definition 6) using the fixed-point computation (Algorithm 1). For the second sub problem (Definition 6), we compute the number of cache misses for the worst and the best case using Definitions 4 and Definition 5.

## 4 The Absint approach

In the Absint approach [4], the notion of cache states is different from that of the NUS approach. We first describe the notion of abstract cache states used during the Absint approach.

#### 4.1 Abstract cache states

An abstract cache state describes the possible combination of instructions in the cache at some instance in time. It is described as a vector  $[set_0, set_1, \ldots, set_{N-1}]$  where each  $set_i$  represents a set of instructions, and the set contains a possible instruction contained in cache line  $c_i \in C$  of a cache state.

For the CFG shown in Figure 2(a), when the program starts executing, we assume the cache to be empty. This is represented as  $[\{\top\}, \{\top\}, \{\top\}, \{\top\}]$ . Instructions are loaded into the cache as the basic blocks are executed (starting from the initial block). E.g., After executing the basic block B1 the abstract cache state is  $[\{m1\}, \{m2\}, \{m3\}, \{m4\}]$ .

Generally, the status of the cache may be unknown when a block is being analysed. In the Absint approach, we use the symbol  $\bot$  to represent an unknown instruction in a cache line. E.g.,  $acs_{\bot} = [\{\bot\}, \{\bot\}, \{\bot\}, \{\bot\}]$  represents the status of every cache line is unknown. This notion of unknown cache state is used during the cache analysis and is explained later.

We now define the abstract cache states.

**Definition 10** (Abstract cache state). Given a cache model  $CM = \langle I, C, CI, G, BI \rangle$ , an abstract cache state  $acs \subseteq (2^{I \cup \{\top, \bot\}})^N$ , can be represented as a vector  $[inst_0, inst_1, \ldots, inst_{N-1}]$  where each element acs[i] represents a set of possible instructions in cache line  $c_i$ . Further, we restrict cache states such that, for any  $i \in [0, N-1]$ ,  $acs[i] \subseteq CI(i) \cup \{\top, \bot\}$ . We denote  $acs_{\top} = [\{\top\}, \{\top\}, \ldots, \{\top\}]$  as the empty cache state, where all the elements of acs are  $\{\top\}$ . Similarly, we define  $acs_{\bot} = [\{\bot\}, \{\bot\}, \ldots, \{\bot\}]$ , where all the elements of acs are  $\{\bot\}$ . Also, the set of all possible abstract cache states are referred to as ACS.

Before we illustrate abstract cache states, we introduce two key terms essential to cache analysis. For any basic block b, an abstract reaching cache state represents the abstract state of the cache prior to the execution of b. Abstract leaving cache state represents the abstract state of the cache after the execution of the basic block. We denote the abstract reaching cache state of a basic block b as  $arcs_b$  and the abstract leaving cache state of a basic block b as  $alcs_b$ .

#### Illustration of abstract cache states

Using Figure 7, we illustrate abstract reaching/leaving cache states of a block. Initially the cache is empty. The state of the cache is  $acs_{\top} = [\{\top\}, \{\top\}, \{\top\}, \{\top\}]]$ . After the execution of block B1, cache lines  $c_0$ ,  $c_1$ ,  $c_2$ ,  $c_3$  will contain instructions m1, m2, m3, m4 respectively, resulting in the  $acs = [\{m1\}, \{m2\}, \{m3\}, \{m4\}]$ . The abstract cache state  $[\{\top\}, \{\top\}, \{\top\}, \{\top\}]]$  is the abstract state of the cache prior to the execution of the basic block B1. Thus,  $arcs_{B1} = \{[\{\top\}, \{\top\}, \{\top\}, \{\top\}]\}$  is the abstract reaching cache state of block B1. Similarly,  $alcs_{B1} = [\{m1\}, \{m2\}, \{m3\}, \{m4\}]$  is the abstract leaving cache state of block B1.

Figure 7: Illustration of the abstract cache states.

The abstract leaving cache state of B1 is also the abstract reaching cache state of B2,  $arcs_{B2} = alcs_{B1}$ . Block B2 has only one instruction m5, and is mapped to cache line  $c_0$ . Thus, the previous instruction in line  $c_0$  will be replaced by m5. Since the  $arcs_{B2} = [\{m1\}, \{m2\}, \{m3\}, \{m4\}]$ , after executing the instructions in B2, the resulting abstract leaving cache state  $alcs_{B2} = [\{m5\}, \{m2\}, \{m3\}, \{m4\}]$ .

Now, the control reaches a branch due to which, it is possible to execute either block B6 or block B7. In this case,  $arcs_{B6} = alcs_{B2} = arcs_{B7}$ . After executing blocks B6 or B7, the state of the cache is either  $[\{m5\}, \{m2\}, \{m3\}, \{m4\}]$  or  $[\{m5\}, \{m6\}, \{m7\}, \{m8\}]$ .

Block B8 has two incoming edges: from blocks B6 and B7. To compute  $arcs_{B8}$ , we need to  $join\ alcs_{B6}$  and  $alcs_{B7}$ . In this case, the join function is a pair-wise union over the vector elements. Thus,  $arcs_{B8}[i] = alcs_{B6}[i] \cup alcs_{B7}[i]$ , resulting in  $arcs_{B8} = [\{m5\}, \{m2, m6\}, \{m3, m7\}, \{m4, m8\}]$ . After execution of block B8, the resulting leaving cache state is  $[\{m5\}, \{m6\}, \{m3\}, \{m4\}]$ .

#### 4.2 The Absint join function

The Absint join function computes the abstract reaching cache state of a basic block when the block has more than one incoming edges. E.g., in Figure 7, the abstract reaching cache state of Block B8 has two incoming edges: from blocks B6 and B7. To compute  $arcs_{B8}$  we need to join  $alcs_{B6}$  and  $alcs_{B7}$ . It is possible that during the computation of the abstract reaching cache state of a block b, we may need to join two abstract leaving cache states that contain unknown instructions for some cache lines. E.g.,  $alcs_1 = [\{m1\}, \{\bot\}, \{m2\}, \{\bot\}]$  and  $alcs_2 = [\{m1\}, \{\bot\}, \{\bot\}, \{\bot\}]$ . The join function could be described as an union over the abstract reaching cache states, i.e.,  $arcs_b = alcs_1 \cup alcs_2 = [\{m1\}, \{\bot\}, \{m2, \bot\}, \{\bot\}]$ . However, as described in Section 4.1, in the Absint approach an unknown instruction  $\bot$  is subsumed by any instruction. E.g.,  $[\{m1\}, \{\bot\}, \{m2, \bot\}, \{\bot\}]$ . This join

function for the Absint approach is defined in Definition 11.

**Definition 11** (Absint join function). We define the join function  $J_{Absint}: ACS \times ACS \rightarrow ACS$  where for any two abstract cache states  $acs_1 \in ACS$  and  $acs_2 \in ACS$ ,

$$J_{Absint}(acs_1, acs_2) = acs_3$$

where for all cache lines  $c_i \in C$  where  $i \in [0, N-1]$

$$acs_3[i] = \begin{cases} acs_1[i] & : if \ acs_2[i] = \bot \\ acs_2[i] & : if \ acs_1[i] = \bot \\ acs_1[i] \cup acs_2[i] & : otherwise \end{cases}$$

Given two abstract cache states  $acs_1 = [\{\bot\}, \{m2\}, \{m3\}, \{\bot\}] \text{ and } acs_2 = [\{m5\}, \{m6\}, \{m7\}, \{\bot\}], \text{ then, } J_{Absint}(acs_1, acs_2) = [\{m5\}, \{m2, m6\}, \{m3, m7\}, \{\bot\}].$  The union of sets that correspond to the same cache lines.

#### 4.3 The Absint transfer function

The Absint transfer function describes how an abstract reaching cache state of a basic block is transformed into an abstract leaving cache state, after executing the instructions in the basic block. E.g., in Figure 7, the abstract reaching cache state of block B2 is  $arcs_{B2} =$  $[\{m1\}, \{m2\}, \{m3\}, \{m4\}]$  and after the execution of block B2, where the instructions of the block is described by  $BI(B2) = [m5, \mp, \mp, \mp]$ , the abstract leaving cache state of B2 is  $alcs_{B2} =$  $[\{m5\}, \{m2\}, \{m3\}, \{m4\}]$ . This transformation can be described as follows. Firstly, if a block b does not have an instructions mapped to a particular cache line  $c_i$   $(BI(b)[i] = \mp)$ , then after execution of the block, the contents of the cache corresponding to that cache line remains the same. E.g., basic block B2 has no instruction mapped to the cache line  $c_1$ ,  $(BI(B2)[1] = \mp)$ , thus, after execution, the abstract leaving cache state has the same set of instructions as in the abstract reaching cache state  $alcs_{B2}[1] = \{m2\} = arcs_{B2}$ . Secondly, if the block has an instruction mapped to a particular cache line  $(BI(b)[i] \neq \mp)$ , then, after execution of the block, the content of the cache corresponding to that cache line is changed to the instruction executed by the block. E.g., basic block B2 has the instruction m5 mapped to the cache line  $c_0$ ,  $(BI(B2)[0] \neq \mp)$ , thus, after execution, the abstract leaving cache state has the instruction m5,  $alcs_{B2}[0] = \{m5\} = \{BI(B2)[0]\}$ . The transfer function,  $T_{Absint}$ , formalises this transformation as follows.

**Definition 12** (Absint transfer function). The Absint transfer function is  $T_{Absint}: B \times ACS \rightarrow ACS$  where, for a given basic block  $b \in B$  and an abstract cache states  $acs \in ACS$ ,

$$T_{Absint}(b, acs) = acs'$$

where for all cache lines  $c_i \in C$  where  $i \in [0, N-1]$  then

$$acs'[i] = \left\{ \begin{array}{ll} acs[i] & : if \quad BI(b)[i] = \mp \\ BI(b)[i] & : otherwise \end{array} \right.$$

Figure 8: Illustration of the Absint transfer function

#### Illustration of the transfer function $T_{Absint}$

Figure 8 illustrates the operation of the transfer function  $T_{Absint}$ . Given block b, with  $BI(b) = [m5, \mp, \mp, \mp]$ , and an abstract reaching cache state  $acs = [\{m1, m5\}, \{m2\}, \{m3\}, \{m4, m8\}]$ , the abstract leaving cache state  $cs' = T_{Absint}(b, acs)$  is computed as follows.

For cache line  $c_0$ , block b executes an instruction m5 on cache line  $c_0$  (BI(b)[0] = m5). Thus, irrespective of the reaching cache state, the leaving cache (acs') contains only the instruction m5 on its cache line  $c_0$ , i.e.,  $cs'[0] = \{m5\} = \{BI(b)[0]\}$ .

For the cache line  $c_1$ , block b has no instruction mapped to cache line  $c_1$  ( $BI(b)[1] = \mp$ ). Thus, the instructions set  $\{m2\}$  on cache line  $c_1$  in acs ( $cs[1] = \{m2\}$ ), is copied to the cache line  $c_1$  of the leaving cache state acs' i.e.,  $acs'[1] = \{m2\} = acs[1]$ . Similarly, block b has no instructions mapped to cache lines  $c_2$  and  $c_3$ , resulting in  $acs'[2] = \{m3\} = cs[2]$  and  $acs'[3] = \{m4, m8\} = acs[3]$ . Thus, given block b, with  $BI(b) = [m5, \mp, \mp, \mp]$  and a reaching cache state  $acs = [\{m1, m5\}, \{m2\}, \{m3\}, \{m4, m8\}], T_{Absint}(b, acs) = acs' = [\{m5\}, \{m2\}, \{m3\}, \{m4, m8\}].$

#### 4.4 Fixed-point computation

Cache analysis starts by the computation of abstract reaching cache state for every block  $b \in B$ . The Absint approach [4] solves this problem using a fixed-point computation algorithm presented in Algorithm 2.

In Algorithm 2, we first initialise the abstract reaching cache states for all blocks (lines 3 to 9, Algorithm 2). Since we assume that initially the state of the cache is empty, on line 5 for the initial block  $b_0$  we set its reaching as  $arcs_{b_0}^1 = \{acs_{\top}\}$ . Here, the notation  $arcs_b^i$  represents the abstract reaching cache state of block b in iteration i. E.g.,  $arcs_{b_0}^1$  represents the reaching cache states of block  $b_0$  for iteration 1. For the rest of the blocks, the execution of the CFG will impact the state of the cache, the state of the cache is unknown. Thus, on line 7, we set their reaching cache states as  $arcs_b^1 = \{acs_{\bot}\}$ .

After initialisation, we compute the abstract leaving cache states of each block, on lines 11 to 14. We apply the transfer function  $T_{UoA}$  to every block and its corresponding abstract reaching cache states.

The iteration index (i) is incremented (line 15) to signal the start of the next iteration. Next, on lines 16 to 26, the abstract reaching cache states of each block are computed. For the initial block  $b_0$ , we know that the abstract reaching cache state is always empty. Thus, on line 19, we always set its reaching as  $arcs_{b_0}^i = \{acs_{\top}\}$ . For rest of the blocks, on lines 22 to 24, the reaching cache states are computed by looking at the leaving cache states of the predecessors (b') of the block b and using the Absint join function.

The iterative process, repeat-until loop on lines 10 to 27, is repeated until a fixed point is reached, i.e., if two consecutive iterations have the same sets of abstract reaching cache states for all blocks (line 27).

#### Algorithm 2 Fixed-point computation for the Absint approach

```

Input: A cache model CM = \langle I, C, CI, G, BI \rangle

Output: arcs_b for every block b \in B.

1: i = 1 {iteration counter}

2: {Initialise the arcs of all blocks}

for each b \in B do

if b = b_0 then

4:

arcs_b^i = acs_{\top}

5:

6:

else

7:

arcs_b^i = acs_{\perp}

end if

8:

9: end for

10: repeat

{Compute the set of leaving cache states for all blocks for iteration i}

11:

12:

for each b \in B do

13:

alcs_b^i = T_{Absint}(b, arcs_b^i)

14:

end for

15:

i = i + 1; {Next iteration}

16:

\{Compute \ arcs \}

17:

for each b \in B do

if b = b_0 then

18:

arcs_b^i = acs_{\top}

19:

20:

else

arcs_b^{i+1} = [\emptyset, \emptyset, \dots, \emptyset]  {Empty vector}

21:

for each alcs_{b'}^i, where (b', b) \in E do arcs_b^{i+1} = J_{Absint}(arcs_b^{i+1}, alcs_{b'})

22:

23:

24:

25:

end if

26:

end for

27: until \forall b \in B, \ arcs_b^i = arcs_b^{i-1} \{\text{Termination condition}\}\

28: return arcs_b^i for all b \in B

```

#### 4.4.1 Illustration of the fixed-point algorithm

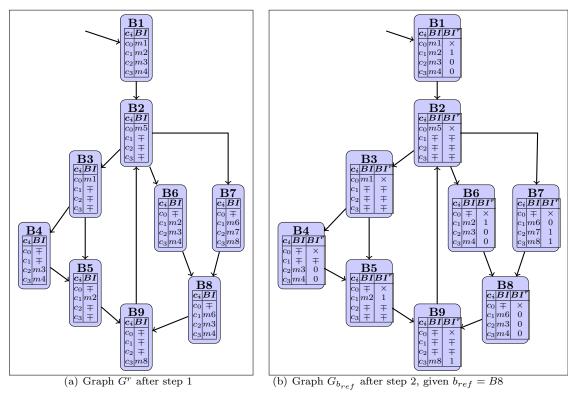

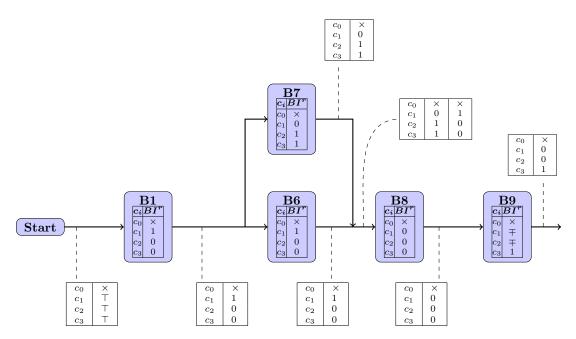

We illustrate the fixed-point algorithm using the Figure 9. The CFG and the mapping of the instructions to cache lines are presented in Figure 9(a) and Figure 9(b) respectively. Figure 9(c) presents a table showing the abstract reaching and abstract leaving cache states for all blocks, during each iteration of the algorithm.

We first initialise the abstract reaching cache states for all blocks (lines 3 to 9). For the CFG in Figure 9(a), the initial block is  $b_0$  is B1. Since we assume that initially the state of the cache is empty, we set  $arcs_{B1}^1$  as  $acs_{\top} = [\{\top\}, \{\top\}, \{\top\}, \{\top\}]]$ . For the rest of the blocks, the state of the cache is unknown. Thus, we set their reaching cache states as  $acs_{\bot} = [\{\bot\}, \{\bot\}, \ldots, \{\bot\}]$ .

After initialisation, to compute the abstract leaving cache state of each block, we apply the transfer function  $T_{Absint}$  (lines 11 to 14). For example, in iteration 1 (i = 1),  $alcs_{B1}^1 = T_{Absint}(B1, arcs_{B1}^1) = T_{Absint}(B1, [\{\top\}, \{\top\}, \{\top\}, \{\top\}]) = [\{m1\}, \{m2\}, \{m3\}, \{m4\}]$ . For block B2, which has one instruction m5 that is mapped to line  $c_0$ , the leaving cache states  $alcs_{B2}^1 = T_{NUS}(B2, [\{\bot\}, \{\bot\}, \{\bot\}, \{\bot\}]) = [\{m5\}, \{\bot\}, \{\bot\}, \{\bot\}]$ . Similarly, the leaving cache states (column 4) for rest of the blocks are computed for iteration 1 as shown in Figure 9(c).

The iteration index (i) is incremented (line 15) to signal the start of the next iteration (i = 2).

| Cache | Instructions  |

|-------|---------------|

| line  |               |

| $c_0$ | m1,m5         |

| $c_1$ | m2,m6         |

| $c_2$ | $_{ m m3,m7}$ |

| $c_3$ | m4,m8         |

(b) Instructions to cache line mapping

|      |          | May analysis                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|