# Minimal Unroll Factor for Code Generation of Software Pipelining

Mounira Bachir, Sid Touati, Brault Frédéric, David Gregg, Albert Cohen

# ▶ To cite this version:

Mounira Bachir, Sid Touati, Brault Frédéric, David Gregg, Albert Cohen. Minimal Unroll Factor for Code Generation of Software Pipelining. International Journal of Parallel Programming, 2012, 10.1007/s10766-012-0203-z . hal-00764521

# HAL Id: hal-00764521 https://inria.hal.science/hal-00764521

Submitted on 14 Dec 2012  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Minimal Unroll Factor for Code Generation of Software Pipelining

Mounira BACHIR, Sid-Ahmed-Ali TOUATI, Frederic BRAULT, David GREGG, Albert COHEN

June 18, 2012

#### Abstract

We address the problem of generating compact code from software pipelined loops. Although software pipelining is a powerful technique to extract fine-grain parallelism, it generates lifetime intervals spanning multiple loop iterations. These intervals require periodic register allocation (also called variable expansion), which in turn yields a code generation challenge. We are looking for the minimal unrolling factor enabling the periodic register allocation of software pipelined kernels. This challenge is generally addressed through one of: (1) hardware support in the form of rotating register files, which solve the unrolling problem but are expensive in hardware; (2) register renaming by inserting register moves, which increase the number of operations in the loop, and may damage the schedule of the software pipeline and reduce throughput; (3) post-pass loop unrolling that does not compromise throughput but often leads to impractical code growth. The latter approach relies on the proof that MAXLIVE registers (maximal number of values simultaneously alive) are sufficient for periodic register allocation [10, 13]. However, the best existing heuristic for controlling this code growth — modulo variable expansion [16] — may not apply the correct amount of loop unrolling to guarantee that MAXLIVE registers are enough, which may result in register spills [10].

This paper presents our research results on the open problem of minimal loop unrolling, allowing a software-only code generation that does not trade the optimality of the initiation interval (II) for the compactness of the generated code. Our novel idea is to use the remaining free registers after periodic register allocation to relax the constraints on register reuse.

The problem of minimal loop unrolling arises either before or after software pipelining, either with a single or with multiple register types (classes). We provide a formal problem definition for each scenario, and we propose and study a dedicated algorithm for each problem.

Our solutions are implemented within an industrial-strength compiler for a VLIW embedded processor from STMicroelectronics, and validated on multiple benchmarks suites.

**Keywords:** Periodic register allocation, software pipelining, code generation, instruction level parallelism, embedded systems, compilation.

# **1** Introduction

Most high performance numerical applications exhibit intensive computations in loops. Software Pipelining (SWP) is an important instruction scheduling technique for improving the execution rate of inner loops. It combines multiple iterations of the loop body into a compact pipelined kernel to facilitate the exploitation of instruction level parallelism (ILP) [18, 16, 19]. The number of cycles between two successive iterations of the kernel loop is called the *initiation interval*.

When a loop is software pipelined, live ranges of variables may extend beyond a single iteration of the loop. As a result, multiple live ranges of the same variable may be in flight at any program point. One may not use regular register allocation algorithms because these different live range instances would create self-interferences in the interference graph [10, 12, 16]. In compiler construction, when no hardware support is available, kernel loop unrolling avoids introducing unnecessary move and spill operations by duplicating the kernel loop body a sufficient number of times

<sup>\*</sup>Professor, University of Nice Sophia-Antipolis. Email: Sid.Touati@inria.fr

to remove live range's self-interference. Computing an adequate unroll factor and allocating registers to the separated live range instances is called *periodic register allocation*.

In this research we are interested in the minimal loop unrolling factor which allows a periodic register allocation for software pipelined loops (without inserting spill or move operations). Having a minimal unroll factor reduces code size, which is an important performance measure for embedded systems because they have a limited memory size. On larger machines, such as desktop, server and supercomputers, total memory size is typically much less limited, but code size is nonetheless important for I-cache performance. In addition to minimal unroll factors, it is necessary that the code generation scheme for periodic register allocation does not generate additional spill; the number of registers required must not exceed MAXLIVE (the number of values simultaneously alive). Spill code can increase the initiation interval and thus reduce performance in the following ways:

- 1. Adding spill code may increase the length of data dependence chains, which may increase the achievable initiation interval.

- 2. Spill code consumes execution resources which restrains the opportunity for achieving a high degree of instructionlevel parallelism.

- 3. Memory requests consume more power than accessing the same values in registers.

- 4. Memory operations (except with scratch-pad local memories) have unknown static latencies. Compilers usually assume short latencies for memory operations, despite the fact that the memory access may miss the cache. Without good estimates of the performance of a piece of code, the compiler may be guided to bad optimisation decisions

When the schedule of a pipelined loop is known, there are a number of known methods for computing unroll factors and performing periodic register allocation, but none of them is fully satisfactory:

- Modulo Variable Expansion (MVE) [12, 16] computes a minimal unroll factor but may introduce spill code because it does not provide an upper bound on register usage.

- Hendren's heuristic [13] computes a sufficient unroll factor to avoid spilling, but with no guarantee in terms of minimal register usage or unrolling degree.

- The meeting graph framework [6] which guarantees that the unroll factor will be sufficient to minimise register usage (reaching MAXLIVE), but not that the unroll factor will itself be minimal.

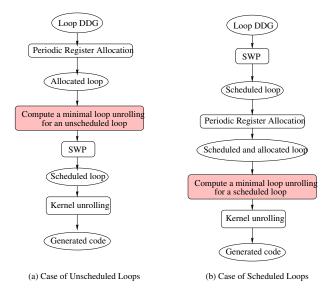

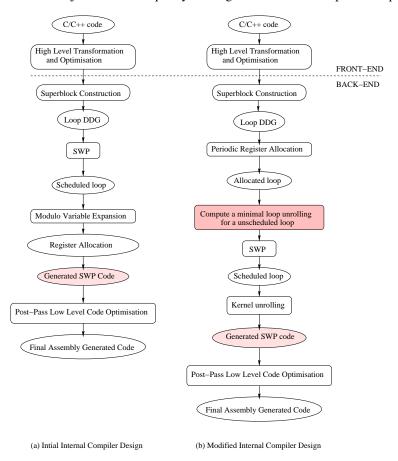

In addition, periodic register allocation can be performed before SWP or after SWP, depending on the compiler construction strategy, as shown in Figure 1. Our article will not debate the best phase order; each compiler has its own characteristic and design implications. Instead we wish to improve the state of the art in loop unrolling minimisation for both possible phase orderings. If periodic register allocation is done before SWP as in Figure 1 (a), the instruction schedule is not fixed, and none of the above periodic register allocation techniques apply.

Contributions. This article advances the state of the art in the following directions:

- 1. We improve the meeting graph method, achieving *significantly smaller unroll factors* while *preserving an optimal register usage* on already scheduled loops. The key idea of our method is to exploit unused registers beyond the minimal number required for periodic register allocation (MAXLIVE [15])

- 2. The existing work in the field of kernel unrolling for periodic register allocation deals with already scheduled loops [6, 13, 12, 16]. As mentioned earlier, we also wish to handle not-yet-scheduled loops, on which the cyclic lifetime intervals are not known by the compiler. This article proposes a method for minimal kernel unrolling when SWP has not yet been carried out, by *computing a minimal unroll factor that is valid for the family of all valid cyclic schedules* of the data dependence graph (DDG). On the other hand, if register allocation is performed after SWP as in Figure 1 (b), the instruction schedule is fixed and hence the cyclic lifetime intervals and MAXLIVE are known.

- 3. We also extend the model of periodic register allocation to handle processor architectures with multiple register types (a.k.a. classes). On such architectures, state-of-the-art algorithms [10, 24] compute the *sufficient unrolling degree*, i.e., the unrolling degree that should be applied to a loop so that it is always possible to allocate the variables of each register type with a minimal number of registers. This article demonstrates that minimising the unroll factor on each register type separately does not define a global minimal unroll factor, and we provide an appropriate problem definition and an algorithmic solution in this context.

- 4. We contribute to the enlightenment of a poorly understood dilemma in back-end compiler construction. First, as mentioned earlier and as shown in Figure 1, we offer the compiler designer more choices to control the register pressure and the unroll factor for periodic register allocation at different epochs of the compilation flow. Second, we greatly simplify the phase ordering problem induced by the interplay of modulo scheduling, periodic register allocation, and post-pass unrolling. We achieve this by providing strong guarantees, not only in terms of register usage (the absence of spills induced by insufficient unrolling), but also in terms of reduction of the unroll factor.

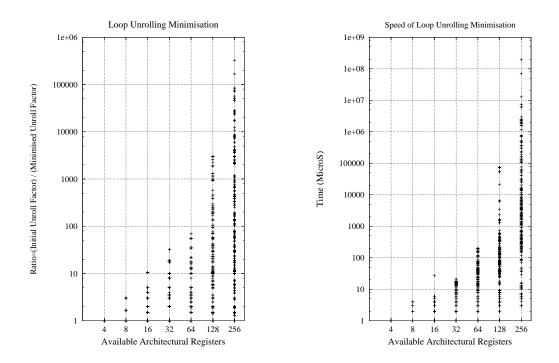

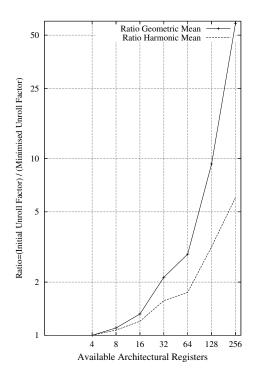

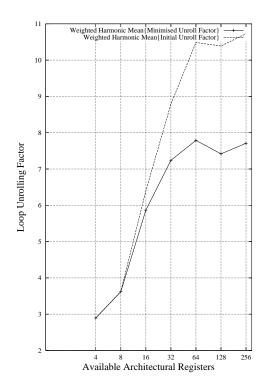

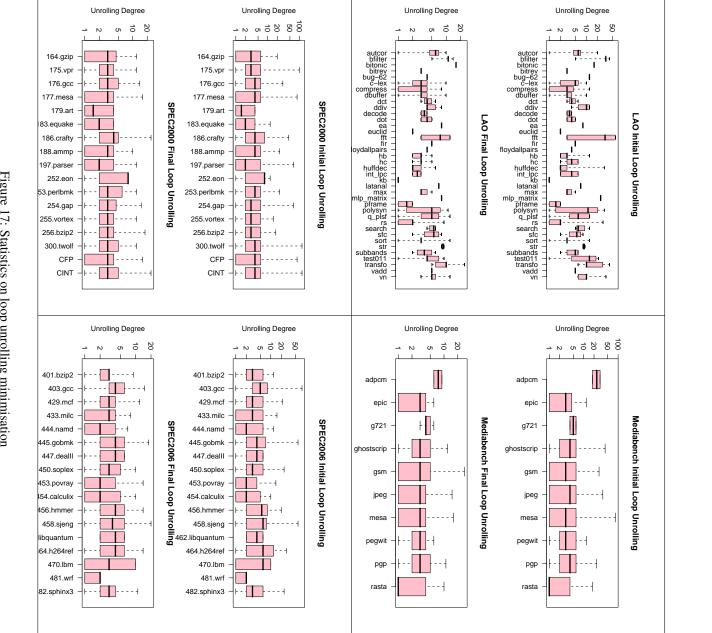

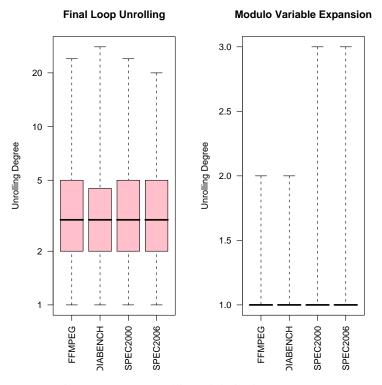

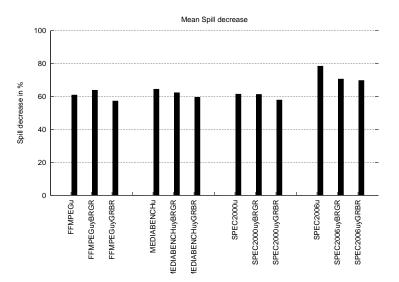

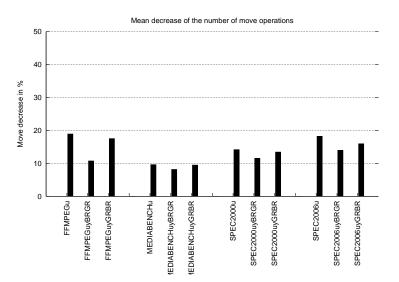

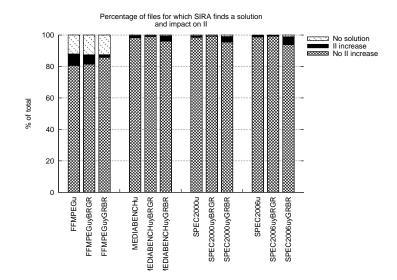

- 5. Our methods are implemented within an industrial-strength compiler for STMicroelectronics' ST2xx VLIW embedded processor family. Our experiments on multiple benchmarks suites LAO, FFMPEG, MEDIABENCH, SPEC CPU2000, and SPEC CPU2006, are unprecedented in scale. They demonstrate the maturity of the techniques and contribute valuable empirical data never published in research papers on software pipelining and periodic register allocation. They also demonstrate the effectiveness of the proposed unroll degree minimisation, both in terms of code size and in terms of initiation intervals (throughput), along with satisfactory compilation times. Better, our techniques outperform the existing compiler for the ST2xx processor family which allocates registers after software pipelining and unrolls using MVE. Our techniques generate less spill code, fewer move operations, and yield a lower initiation interval on average, with a satisfactory code size (loops fitting within the instruction cache). These experiments are also teachful in their more negative results. As expected, they show that achieving strong guarantees on spill-free periodic register allocation yields generally higher unroll factors than heuristics providing no such guarantees like MVE [12, 16]. It was more unexpected (and disappointing) to observe that the initiation intervals achieved with MVE remain generally excellent, despite the presence of spills and a higher number of move operations. This can be explained by the presence of numerous empty slots in the cyclic schedules, where spills and move operations can be inserted, and by the rare occurrence of these spurious operations on the critical path of the dependence graph.

Figure 1: Minimal unroll factor computation depending on phase ordering

**Outline.** The paper is organised as follows. Section 2 describes existing research results that are necessary to understand the rest of this article. Section 3 formalises the problem of minimising the loop unrolling degree in the presence of multiple register types when the loop is unscheduled. For clarity, we start the explanation of our loop-unrolling minimisation algorithm in Section 4 with the case of a single register type. Then, Section 5 generalises the solution to multiple register types. When the loop is already scheduled, an adapted algorithm is provided in Section 6 based on the meeting graph framework. Section 7 presents detailed experimental results on standard benchmark suites. In Section 8 we discuss related work on code generation for periodic register allocation, and we explain our contribution compared to the previous work. Finally, we conclude in Section 9.

# 2 Background

### 2.1 Loop Model and Software Pipelining

A data dependence graph (DDG) is a directed multigraph G = (V, E) where V is a set of vertices representing instructions in a loop (also called statements, nodes, operations) and E is a set of edges representing data dependences (both flow and memory-based).

The modeled processor may have several register types: the set of available register *types* is denoted by  $\mathcal{T}$ . For instance,  $\mathcal{T} = \{BR, GR, FP\}$  for branch, general purpose, and floating point registers respectively. Register types are sometimes called register *classes*. The number of available registers of type t is noted  $\mathcal{R}^t$ ; it may be less than the total number of registers of type t as some architectural registers are often reserved for specific purposes.

For a given register type  $t \in \mathcal{T}$ , we define  $V^{R,t} \subseteq V$  to be the set of statements  $u \in V$  that produce values to be stored inside registers of type t. We  $u^t$  denotes the value of type t defined by an instruction  $u \in V^{R,t}$ . Indeed, a statement u may produce multiple values of distinct types, but we assume a given statement may not produce multiple values of the same type. The value may also be written u when the type is irrelevant or clear from the context.<sup>1</sup>

Concerning the set of edges E, we distinguish *flow* edges of type t — denoted  $E^{R,t}$  — from the remaining edges. A flow edge e = (u, v) of type t represents the producer-consumer relationship between the two statements u and v: u creates a value read by the statement v. Considering a register of type t, the set  $E - E^{R,t}$  of non-flow edges are called memory-based edges.

Since we focus an loops and take into account loop-carried dependences, the DDG G = (V, E) may be cyclic. Each edge  $e \in E$  becomes labeled by a pair of values  $(\delta(e), \lambda(e))$ .  $\delta : E \to \mathbb{Z}$  defines the latency of edges and  $\lambda : E \to \mathbb{Z}$  defines the distance in terms of number of iterations. In order to exploit the parallelism between the instructions belonging to different loop iterations, we rely on periodic scheduling instead of acyclic scheduling, also called *software pipelining* (SWP).

SWP can be modeled by a periodic scheduling function  $\sigma : V \to \mathbb{Z}$  and an *initiation interval II*. The operation u of the  $i^{\text{th}}$  loop iteration is noted u(i), it is scheduled at date  $\sigma(u) + i \times II$ . Here,  $\sigma(u)$  represents the execution (issue) date of u(0), the clock cycle number of u for the first loop iteration. The schedule function  $\sigma$  is valid *if* it satisfies the periodic precedence constraints

$$\forall e = (u, v) \in E : \sigma(u) + \delta(e) \le \sigma(v) + \lambda(e) \times II$$

SWP allows instructions to be scheduled independently of the original loop iterations barriers. The maximal number of values of type t simultaneously alive, noted MAXLIVE<sup>t</sup>, defines the minimal number of registers required to allocate periodically the variables of the loop without introducing spill code. However, since some live ranges of variables span multiple iterations, special care must be taken when allocating registers and colouring an interference graph; this is the core focus of the paper and will be detailed later.

Let  $RC^t$  be the number of registers of type t to be allocated for the kernel of the pipelined loop. If the register allocation is optimal, we must have  $RC^t = MAXLIVE^t$  for all register types  $t \in \mathcal{T}$ . We will see that there are only two theoretical frameworks that guarantee this optimality for SWP code generation. Other frameworks have  $RC^t \ge MAXLIVE^t$ , with no guaranteed upper bound for  $RC^t$ .

<sup>&</sup>lt;sup>1</sup>A few instruction sets allow this, and it can be modeled by node duplication: a node creating multiple results of the same type is split into multiple nodes of the same type.

### 2.2 Loop Unrolling after SWP with Modulo Variable Expansion

Code generation for SWP has to deal with many issues: prologue/epilogue codes, early exits from the loops, variables spanning multiple kernel iterations, etc. In our article, we focus on the last point: how can we generate a compact kernel for variables spanning multiples iterations when no hardware support exists in the underlying processor architecture? When no hardware support exists, and when prohibiting the insertion of additional move operations (i.e., no additional live range splitting), kernel loop unrolling is the only option. The resulted loop body itself is bigger but no extra operations are executed in comparison with the original code. Lam designed a general loop unrolling scheme called *modulo variable expansion* (MVE) [16]. In fact, the major criterion of this method is to minimise the loop unrolling degree because the memory size of the i-WARP processor is low [16]. The MVE method defines a minimal unrolling degree to enable code generation after a given periodic register allocation. This unrolling degree is obtained by dividing the length of the longest of all live ranges  $LT_v$  of variables v defined in the pipelined kernel, by the initiation interval, i.e.,  $\left\lceil \frac{\max_v LT_v}{T} \right\rceil$ .

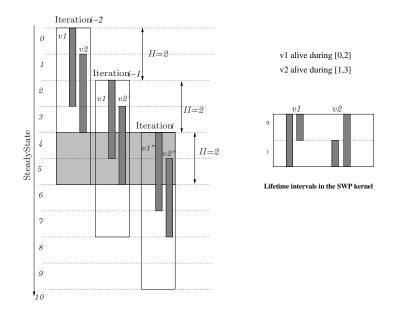

MVE is easy to understand and implement, and it is practically effective in limiting code growth. This is why it has been adopted by several SWP frameworks [5, 15], and included in commercial compilers. The problem with MVE is that it does not guarantee a register allocation with MAXLIVE<sup>t</sup> registers of type t, and in general it may lead to unnecessary spills breaking the benefits of software pipelining. A concrete example of this limitation is illustrated in Figures 2 and 3; we will use it as a running example in this section. Figure 2 is a SWP example with two variables  $v_1$ and  $v_2$ . For simplicity, we consider here a single register type t. New values of  $v_1$  and  $v_2$  are created every iteration. For instance, the first value of  $v_1$  is alive during the time interval [0, 2], the other values ( $v'_1$  and  $v'_1$ ) are created every multiple of II. This figure shows a concrete example with a SWP kernel having two variables  $v_1$  and  $v_2$  spanning multiple kernel iterations. In the SWP kernel, we can see that MAXLIVE<sup>t</sup> = 3.

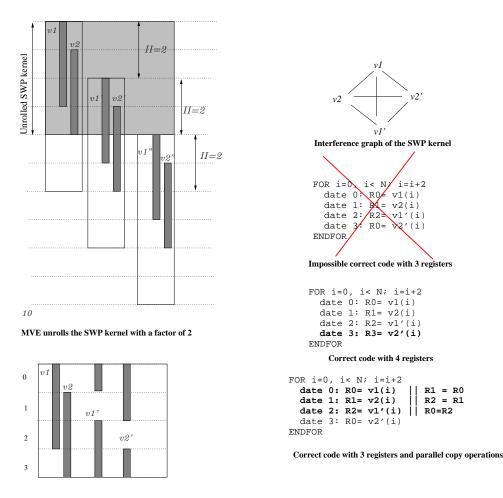

To generate a code for this SWP kernel, MVE unrolls it with a factor of  $\left[\frac{\max(LT_{v_1}, LT_{v_2})}{II}\right] = \left[\frac{\max(3,3)}{2}\right] = 2$ .

Figure 3 illustrates the considered unrolled SWP kernel. The values created inside the SWP kernel are  $v_1$ ,  $v_2$ ,  $v'_1$ , and  $v'_2$ . Because of the periodic nature of the SWP kernel, the variables  $v'_1$  and  $v'_2$  are alive as entry and exit values (see the figure of the lifetime intervals in the SWP kernel). Now, the interference graph of the SWP kernel is drawn, and we can see that it cannot be coloured with less than 4 colours (a maximal clique is  $\{v_1, v_2, v'_1, v'_2\}$ ). Consequently, it is impossible to generate a code with  $RC^t = 3$  registers, except if we add extra copy operations in parallel. If inserting copy operations is not allowed or possible (no free slots, no explicit ILP), then we need  $RC^t = 4$  registers to generate a correct code. This example gives a simple case where  $RC^t > MAXLIVE^t$ , and it is not known if  $RC^t$  is bounded. As consequence, it is possible that the computed SWP schedule has  $MAXLIVE^t \leq \mathcal{R}^t$ , but the code generation performed with MVE requires  $RC^t > \mathcal{R}^t$ . This means that spill code has to be inserted even if  $MAXLIVE^t \leq \mathcal{R}^t$ , which is unfortunate and unsatisfactory.

Fortunately, an algorithm exists that achieves an allocation with a minimal number of registers equal to  $RC^t = MAXLIVE^t$  [6, 10]. This algorithm exploints the meeting graph, introduced in the next section.

### 2.3 Meeting Graphs (MG)

The algorithm of Eisenbeis et al. [6, 10] can generate a periodic register allocation using MAXLIVE<sup>t</sup> registers if the kernel is unrolled, thanks to a dedicated graph representation called the *meeting graph* (MG). It is a more accurate graph than the usual interference graph, as it holds information on the number of clock cycles of each live range and on the succession of the live ranges along the loop iterations. It allows us to compute an unrolling degree which enables an allocation of the loops with  $RC^t = MAXLIVE^t$  registers.

Intuitively, the meeting graph is useful because it captures information about pairs of values where one value dies on the same clock cycle that another value becomes alive. If we try to allocate such values to the same register, then there is no dead time when the register contains a dead value. By identifying circuits in the meeting graph, we find sets of live values that can be allocated to one or more registers with no dead time.

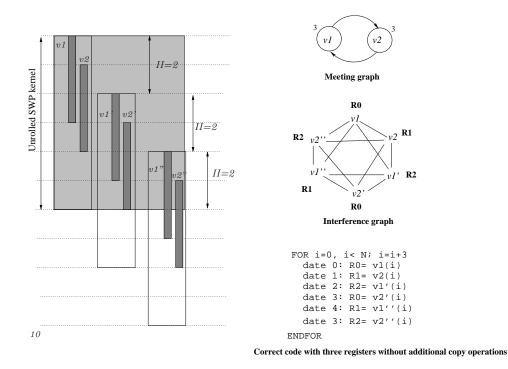

Let us consider again the running example in Figure 2. The meeting graph that corresponds to that SWP is illustrated in Figure 4: a node is associated to every variable created in the SWP kernel. Hence we have two nodes  $v_1$  and  $v_2$ . A node u is labeled with a weight  $\omega(u)$  corresponding to the length og its respective live range, here 3 clock cycles for variables  $v_1$  and  $v_2$ . There is an edge connecting a source node to a sink node *if and only if* the lifetime

Figure 2: Example to highlight the short-comings of the MVE technique

interval of the first node ends when the sink one starts. By examining the SWP kernel in Figure 2, we see that the copies of  $v_1$  end when those of  $v_2$  start, and vice-versa. Consequently, in the MG of Figure 4, we have an edge from  $v_1$  to  $v_2$  and vice-versa to model an abstraction of the register reuse for this fixed SWP schedule.

Now, the question is: what is the benefit of such graph structure? Using this graph structure we are able to compute a provably sufficient unrolling factor to apply in order to achieve an optimal register allocation, that is  $RC^t = MAXLIVE^t$  [6, 10].

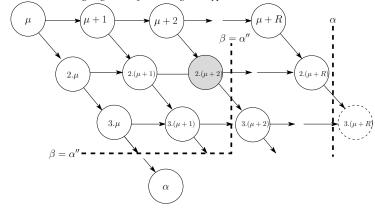

Let us consider the set of the strongly connected components (SCC) of the MG. In our simple example, there is a single SCC. The weight of every SCC numbered k is defined as  $\mu_k = \frac{\sum_{v \in SCC_k} \omega(v)}{II}$ . Note that one of the properties of the MG is that  $\sum_{v \in SCC_k} \omega(v)$  is always a multiple of II, and  $\frac{\sum_{\forall v} \omega(v)}{II} = \text{MAXLIVE}^t$ . In our simple example with a single SCC, its weight is equal to  $\mu_1 = \frac{3+3}{2} = 3$ .

Then, the *sufficient* unrolling factor computed using the MG is equal to  $\alpha = lcm(\mu_1, ..., \mu_k)$ , where *lcm* denotes the least common multiple [10]. It has been proved that if the SWP kernel is unrolled  $\alpha$  times, then we can generate code with  $RC^t = MAXLIVE^t$  registers. In the example illustrated in Figure 4, we have a single SCC so  $\alpha = \mu_1 = 3$ , which means that the kernel has to be unrolled with a factor equal to 3. The interference graph shows that three colours are sufficient, which allows us to generate correct code with only three registers, rather than the four required with modulo variable expansion (compared to Figure 3).

Without formally proving the correctness of the unrolling factor defined above (the interested reader is invited to study [6, 10]), the intuition behind the least common multiple (LCM) formula comes from the following fact: if we successfully generate code for a SCC by unrolling the kernel  $\mu_i$  times, then we can generate a correct code for the same SCC by unrolling the kernel with any multiple of  $\mu_i$ . Hence, if we are faced with a set of SCCs, it is sufficient to consider the LCM of the  $\mu_i$ 's to have a correct unrolling factor for all the SCCs.

In addition to the previous unroll factor formula, the MG also allows us to guarantee that MAXLIVE<sup>t</sup> or MAXLIVE<sup>t</sup> + 1 are sufficient unrolling factors. In the example of Figure 4, we have the coincidence that  $\alpha = MAXLIVE^t$ , but this is not always the case. Indeed, one of the purposes of MG is to have unrolling factors  $\alpha$  lower than MAXLIVE<sup>t</sup>. This objective is not always reachable if we want to have  $RC^t = MAXLIVE^t$ , Eisenbeis et al. [10] try to reach it by decomposing the MG into a maximal number of elementary circuits. In practice, it turns out that  $\alpha$  may be very high, reducing the practical benefit of register optimality  $RC^t = MAXLIVE^t$ .

The next section recalls a theoretical framework that applies periodic register allocation before SWP, while allowing the computation of a sufficient unrolling degree for a complete set of possible SWP schedules.

Lifetime intervals in the SWP kernel

Figure 3: SWP kernel unrolled with MVE

### 2.4 SIRA and Reuse Graphs

*Reuse graphs* are a generalisation of previously work by de Werra et al. and Hendren et al. [6, 13]. They are used inside a framework called SIRA [23, 24]. Unlike the previous approaches for periodic register allocation, reuse graphs are used before software pipelining to generate a move-free or a spill-free periodic register allocation in the presence of multiple register types. Reuse graphs provide a formalised approach to generating code which requires neither register spills nor move operations. Of course, it is not always possible to avoid spill code, some DDGs are complex enough to always require spilling, the SIRA framework is able to detect such situations before SWP.

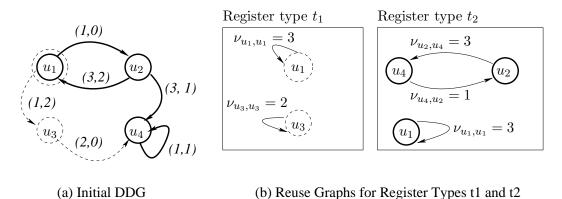

A simple way to explain SIRA is to provide an example. All the theory has already been presented in Touati and Eisenbeis [24], and we recently showed that optimising the register requirement for multiple register types in one go is a better approach than optimising for every register type separately [23]. Figure 5(a) provides an initial DDG with two register types  $t_1$  and  $t_2$ . Statements producing results of type  $t_1$  are in dashed circles, and those of type  $t_2$  are in bold circles. Statement  $u_1$  writes two results of distinct types. Flow dependence through registers of type  $t_1$  are in dashed edges, and those of type  $t_2$  are in bold edges.

Each edge e in the DDG is labeled with the pair of values  $(\delta(e), \lambda(e))$ . Now, the question is how to compute a periodic register allocation for the loop in Figure 5(a) without hurting the instruction level parallelism if possible.

Periodic register constraints are modeled using *reuse graphs*. We associate a reuse graph  $G^{\text{reuse},t}$  to each register type t, see Figure 5(b). The reuse graph is computed by the SIRA framework, Figure 5(b) is one of the examples that

Figure 4: Example to explain the optimality of the meeting graph technique

Figure 5: Example for SIRA and reuse graphs

SIRA may produce. Note that the reuse graph is not unique, other valid reuse graphs may exist.

A reuse graph  $G^{\text{reuse},t} = (V^{R,t}, E^{\text{reuse},t})$  contains  $V^{R,t}$ , i.e., only the nodes writing to registers of type t. These nodes are connected by *reuse edges*. For instance, in  $G^{\text{reuse},t_2}$  of Figure 5(b), the set of reuse edges is  $E^{\text{reuse},t_2} = \{(u_2, u_4), (u_4, u_2), (u_1, u_1)\}$ . Also,  $E^{\text{reuse},t_1} = \{(u_1, u_3), (u_3, u_1)\}$ . Each reuse edge  $e_r = (u, v)$  is labeled by an integral distance  $\nu^t(e_r)$ , that we call *reuse distance*. The existence of a reuse edge  $e_r = (u, v)$  of distance  $\nu^t(e_r)$  means that u(i) (iteration i of u) and  $u(i + \nu^t(e_r))$  (iteration  $i + \nu^t(e_r)$  of v) share the same destination register of type t. Hence, reuse graphs allow to completely define a periodic register allocation for a given loop. In the example of Figure 5(b) and for register type  $t_2$ , we have  $\nu^{t_2}((u_2, u_4)) = 3$  and  $\nu^{t_2}((u_4, u_2)) = 1$ .

Let C be a circuit in the reuse graph  $G^{\text{reuse},t}$  of type t; we call C a *reuse circuit*. We note  $\mu^t(C) = \sum_{e_r \in C} \nu^t(e_r)$  the weight of the reuse circuit C. The following corollary provides a sufficient unrolling factor for all register types.

**Corollary 1** [24] Let G = (V, E) be a loop DDG with a set of register types  $\mathcal{T}$ . Each register type  $t \in \mathcal{T}$  is associated with a valid reuse graph  $G^{\text{reuse},t} = (V^{R,t}, E^{\text{reuse},t})$ . The loop can be allocated with  $RC^t = \sum_{e_r \in E^{\text{reuse},t}} \nu^t(e_r)$  registers for each type t if we unroll it  $\alpha$  times, where:

$$\alpha = lcm(\alpha_1^t, \cdots, \alpha_n^t)$$

$\alpha^{t_i}$  is the unrolling degree of the reuse graph of type  $t_i$ , defined as

$$\alpha^t = lcm(\mu^t(C_1), \cdots, \mu^t(C_n))$$

The above corollary seems to be close to the meeting graph result. This is not exactly true, since here we are generalizing the meeting graph result to unscheduled loops in the presence of multiple registers types. Unlike the meeting graph, the above defined unrolling factor is valid for a whole set of SWP schedules, not for a fixed one. In addition, the reuse graph allows us to guarantee that prior to software pipelining  $RC^t = \sum_{e_r \in E^{\text{reuse},t}} \nu^t(e_r) \leq \mathcal{R}^t$  for any register type, while maintaining instruction level parallelism if possible (by taking care not to increase the critical circuit of the loop, known as the  $MII_{dep}$ ).

Note that when compilation time matters, we can avoid unrolling the loop before the SWP step. This avoids increasing the DDG size, which would result in significantly more work for the scheduler. Because we allocate registers directly on the DDG by inserting loop carried anti-dependencies, the DDG can be scheduled without unrolling it. In other words, loop unrolling can be applied at the code generation step (after SWP) in order to apply the register allocation computed before scheduling.

**Example 1** Let consider as illustration the example of Figure 5. Here  $\alpha_{t_1} = lcm(3,2) = 6$  and  $\alpha_{t_2} = lcm(3+1,3) = 12$ . That is, the register type  $t_1$  requires that we unroll the loop 6 times if we want to consume  $RC^{t_1} = 3 + 2 = 5$  registers of type  $t_1$ . At this compilation step, SWP has not been carried out but SIRA guarantees that the computed unroll factor and register count are valid for any subsequent SWP. As an illustration, a valid sequential trace for the for the register type  $t_1$  is given in Listing 1 (we do not show the trace for register type  $t_2$ , and we omit the prologue/epilogue of the trace).

The reader may check that we have used 5 registers of type  $t_1$ . According to the reuse graph, every pair of statements  $(u_1(i), u_1(i+3))$  uses exactly the same destination register, because there is a reuse edge  $(u_1, u_1)$  with a reuse distance  $\nu^{t_1}(u_1, u_1) = 3$ ; Every pair of statements  $(u_3(i), u_3(i+2))$  uses the same destination register too, because there is a reuse edge  $(u_3, u_3)$  with a reuse distance  $\nu^{t_1}(u_3, u_3) = 2$ . We can check in the generated code that the reuse circuit  $(u_1, u_1)$ , which contains a single reuse edge in this example, uses three registers  $(R_1, R_2 \text{ and } R_3)$ ; The reuse circuit  $(u_3, u_3)$  uses two registers  $(R_4 \text{ and } R_5)$ .

Regarding the register type  $t_2$ , it requires an unrolling factor equal to 12 if we want to consume  $RC^{t_2} = 3+1+3 = 7$  registers of type  $t_2$ . Consequently, a common valid unroll factor for both the register types  $t_1$  and  $t_2$  is equal to  $\alpha = lcm(6, 12) = 12$ . For space reasons, we do not show the full code generation for the loop in Figure 5 with an unrolling factor of 12. However, later in Section 5, we will show how we will minimise the unrolling degree to get a reasonable value equal to 4, it will be then possible to write a reasonably short code for the example.

The main advantage of the meeting graph and reuse graph approaches over MVE is their ability to guarantee spillfree and move-free code generation, before or after SWP. However, they have an important drawback, which is that the unroll factor may be very large. The next section defines the problem of unroll degree minimisation for unscheduled loops. Later, we will extend the problem to scheduled loops.

# **3** Problem Description of Unroll Factor Minimisation for Unscheduled Loops

The reuse graph method, which guarantees a register allocation with exactly MAXLIVE registers, may result in a large unrolling factor. However, there may be additional unused registers:: each register type t may have some remaining registers  $R^t = \mathcal{R}^t - RC^t$  (where  $\mathcal{R}^t$  is the number of available architectural registers of type t). We have developed a method to use any remaining registers to reduce the unrolling factor. This method is applied after the periodic register allocation step performed by the SIRA framework. This post-pass minimisation consists in adding zero or more unused registers to each reuse circuit in order to minimise the least common multiple of the size of the circuits (denoted  $\alpha^*$ ). This idea is described in the next problem.

Listing 1: Example of a sequential kernel code generation for the register type  $t_1$

FOR i=0, i<N, i=i+6  $u_1(i)$  : R1 = ...u\_2(i) : u\_3(i) : R4 = R2... u\_4(i) : ...= R4...  $u_1(i+1): R2 = ...$ u\_2(i+1):  $u_3(i+1): R5 = R3...$ u\_4(i+1): ...= R5...  $u_1(i+2): R3 = ...$ u\_2(i+2): u\_3(i+2): R4 = R1... u\_4(i+2): ...= R4...  $u_1(i+3): R1 = ...$ u\_2(i+3):  $u_3(i+3): R5 = R2...$ u\_4(i+4): ...= R5...  $u_1(i+4): R2 = ...$ u\_2(i+4):  $u_3(i+4): R4 = R3...$ u\_4(i+4): ...= R4...  $u_1(i+5): R3 = ...$ u\_2(i+5):  $u_3(i+5): R5 = R1...$ u\_4(i+5): ...= R5... ENDFOR

**Problem 1 (Loop Unroll Minimisation (LUM))** Let  $\alpha$  be the initial loop unrolling degree and let  $\mathcal{T} = \{t_1, \ldots, t_n\}$  be the set of register types. For each register type  $t_j \in \mathcal{T}$ , let  $\mathbb{R}^{t_j} \in \mathbb{N}$  be the number of remaining registers after a periodic register allocation for this register type. Let  $k_j$  be the number of reuse circuits of type  $t_j$ . We note  $\mu_{i,t_j} \in \mathbb{N}$  as the weight of the *i*<sup>th</sup> reuse circuit of the register type  $t_j$ . For each reuse circuit *i* and each register type  $t_j$ , we must compute the added registers  $r_{i,t_j}$  such that we find a new periodic register allocation with a minimal loop unrolling degree. This is described by the following constraints:

1.  $\alpha^* = lcm(lcm(\mu_{1,t_1} + r_{1,t_1}, \dots, \mu_{k_1,t_1} + r_{k_1,t_1}), \dots, lcm(\mu_{1,t_n} + r_{1,t_n}, \dots, \mu_{k_n,t_n} + r_{k_n,t_n}))$  is minimal (optimality constraint).

2.

$$\forall t_j \in \mathcal{T}, \ \sum_{i=1}^{k_j} r_{i,t_j} \leq R^{t_j} \ (validity \ constraints)$$

That is, this formal problem describes the idea of increasing the number of allocated registers without exceeding the number of available ones (to guarantee the absence of spilling), with the goal of minimising the global unroll factor. Increasing the number of allocated registers is done by increasing the weights of the reuse circuit. If a reuse circuit consists of multiple edges, then increasing the weigth of any edge inside this reuse circuit is a valid solution. This solution is valid as proved in the next lemma. Intuively, this lemma says that if we succeed in building a periodic register allocation with  $RC_1^t$  registers of type t, then we can build a periodic register allocation with  $RC_2^t$  registers of type t, where  $RC_1^t \leq RC_2^t \leq \mathcal{R}^t$

**Lemma 1** Let G = (V, E) be a loop data dependence graph. Let  $G^{reuse}$ , be a valid reuse graph of each register type  $t \in \mathcal{T}$  associated with the loop G. Let  $\mathcal{R}$  be the number of available registers of type t. Let  $(u_i^t, u_j^t)$  a single arbitrary reuse arc in  $G^{reuse,t}$  with its associated reuse distance  $\nu_{i,j}^t \in \mathbb{Z}$ . Then:

$$\nu_{i,j}^t \leq \mathcal{R}^t \Longrightarrow \forall x \in [0, \mathcal{R}^t - \nu_{i,j}^t], \nu_{i,j}^t + x \text{ is a valid reuse distance for the reuse arc } (u_i^t, u_j^t)$$

### **Proof:**

The proof comes from the formal linear constraints defining the validity of  $\nu$  variables. These constraints have been defined in [24, 23], that we summarise here. The proof is organised in three subsections. Subsection 3.1 recalls the integer linear program that defines the validity constraints of a reuse graph. Then, Subsections 3.2 and 3.2 prove that  $\nu_{i,j}^t + x$  does not violate these validity conditions.

Our processor model considers both UAL (Unit Assumed Latencies) and NUAL (Non UAL) semantics [21]. Given a register type  $t \in \mathcal{T}$ , we model possible delays when reading from or writing into registers of type t. We define two delay functions  $\delta_{r,t} : V \mapsto \mathbb{N}$  and  $\delta_{w,t} : V^{R,t} \mapsto \mathbb{N}^2$  These delay functions model NUAL semantics. Thus, the statement u reads from a register  $\delta_{r,t}(u)$  clock cycles after the schedule date of u. Also, u writes into a register  $\delta_{w,t}(u)$  clock cycles after the schedule date of u. In UAL, the code semantics is sequential, these delays are not visible to the compiler, so we have  $\delta_{w,t} = \delta_{r,t} = 0$ .

In this proof, we consider G = (V, E) to be a loop DDG, and  $G^{\text{reuse},t}$  an associated reuse graph to be computed using integer linear constraints as defined below.

### **3.1** Linear Constraints for $\nu$ Variables

This section briefly recalls the construction of the reuse graph. A recent description for multiple register types can be found in Touati et al. [23, 24]. We say that a value is killed when all its consumers have already read it, and consequently, it does not have to occupy a register anymore. Any last reading instruction is called its killer. If the DDG is already scheduled, then it is easy to compute the killing instruction and the killing date of each value. However, if the DDG is not already scheduled as in our case, then the killing instruction is not known. For each value v, we create a virtual killer K, adding edges from all the consumers of v to the killer node K, and we also introduce reuse edges from K to all subsequent iterations of the consumers of v.

$<sup>^{2}</sup>w$  is a write to a register of type t, hence the restriction to  $V^{R,t}$  for  $\delta_{w,t}$ .

#### 3.1.1 Basic variables

• We define a schedule variable  $\sigma_i \in \mathbb{N}$  for each statement  $u_i \in V$ , including  $\sigma_{K_i}$  for each killer  $K_i$ . We consider L as a maximal value for  $\sigma$  variables, L is sufficiently large (for instance  $L = \sum_{e \in E} \delta(e)$ ).

Since our instruction scheduling function is a modulo schedule with initiation interval II, we only consider the integer execution date of the first operation occurrence  $\sigma_i = \sigma(u_i(0))$  and the execution date of any other occurrence  $u_i(k)$  becomes equal to  $\sigma(u_i(k)) = \sigma_i + k \times II$ .

- A binary variable  $\theta_{i,j}^t$  for each pair of statements  $(u_i^t, u_j^t) \in V^{R,t} \times V^{R,t}$ . It is set to 1 if and only if  $(u_i^t, u_j^t)$  is a reuse arc;

- A reuse distance  $\nu_{i,j}^t \in \mathbb{N}$  for each pair of statements  $(u_i^t, u_j^t) \in V^{R,t} \times V^{R,t}$  that is a reuse arc.

#### 3.1.2 Linear constraints

#### • Data dependences

The schedule must at least satisfy the precedence constraints defined by the DDG.

$$\forall e = (u_i, u_j) \in E : \sigma_j - \sigma_i \ge \delta(e) - II \times \lambda(e) \tag{1}$$

#### • Flow dependences

Each flow dependence  $e = (u_i^t, u_j^t) \in E^{R,t}, \forall t \in \mathcal{T}$  means that the statement occurrence  $u_j(k + \lambda(e))$  reads the data produced by  $u_i(k)$  at time  $\sigma_j + \delta_{r,t}(u_j) + (\lambda(e) + k) \times II$ . Then, we must schedule the killer  $K_i$  of the statement  $u_i$  after all  $u_i$ 's consumers.  $\forall t \in \mathcal{T}, \forall u_i \in V^{R,t}, \forall u_j \in \{v \mid (u_i, v) \in E^{R,t}\} | e = (u_i, u_j) \in E^{R,t}$ :

$$\sigma_{K_i} \ge \sigma_j + \delta_{r,t}(u_j) + II \times \lambda(e) \tag{2}$$

#### • Storage dependences

There is a storage dependence between  $K_i$  and  $u_j^t$  if  $(u_i^t, u_j^t)$  is a reuse arc of type t.  $\forall t \in \mathcal{T}, \forall (u_i, u_j) \in V^{R,t} \times V^{R,t}$ :

$$\theta_{i,j}^t = 1 \Longrightarrow \sigma_{K_i} - \delta_{w,t}(u_j) \le \sigma_j + II \times \nu_{i,j}^t$$

This involvement can result in the following inequality:  $\forall t \in \mathcal{T}, \forall (u_i^t, u_i^t) \in V^{R,t} \times V^{R,t}$ ,

$$\sigma_j - \sigma_{K_i} + II \times \nu_{i,j}^t + M_1 \times (1 - \theta_{i,j}^t) \ge -\delta_{w,t}(u_j) \tag{3}$$

where  $M_1$  is an arbitrarily large constant.

If there is no register reuse between two statements  $u_i$  and  $u_j$ , then  $\theta_{i,j}^t = 0$  and the storage dependence distance  $\nu_{i,j}^t$  must be set to 0 in order to not be accumulated in the objective function.

$$\forall (u_i, u_j) \in V^{R,t} \times V^{R,t} : \nu_{i,j}^t \le M_2 \times \theta_{i,j}^t \tag{4}$$

where  $M_2$  is an arbitrarily large constant.

### • Reuse relations

The reuse relation of type t must be a bijection from  $V^{R,t}$  to  $V^{R,t}$ . A register of type t can be reused by one statement and a statement can reuse one released register:

$$\forall u_i^t \in V^{R,t} : \sum_{u_j^t \in V^{R,t}} \theta_{i,j}^t = 1$$

(5)

$$\forall u_j^t \in V^{R,t}: \sum_{u_i^t \in V^{R,t}} \theta_{i,j}^t = 1$$

(6)

From the above integer linear program, we see that the  $\nu$  variables are constrained by Inequality 4 and 3. The two following subsections treat them separately.

### **3.2** Valid Upper Bounds of $\nu$ Variables (Inequality 4)

From the above linear constraints, we prove here that increasing the values of  $\nu$  variables does not violate the upper bounds of  $\nu$  variables.

The constraints which define an upper bound for  $\nu$  variables are defined by Inequality 4:

$$\forall (u_i, u_j) \in V^{R,t} \times V^{R,t} : \nu_{i,j}^t \leq M_2 \times \theta_{i,j}^t$$

We have two cases regarding  $\theta_{i,j}^t \in \{0,1\}$  value:

- 1.  $\theta_{i,j}^t = 0 \Longrightarrow \nu_{i,j}^t \le 0$ . Since  $\nu_{i,j}^t \in \mathbb{N} \Longrightarrow \nu_{i,j}^t = 0$ . This means that if  $(u_i^t, u_j^t)$  is not a reuse arc, then its reuse distance is equal to zero.

- 2.  $\theta_{i,j}^t = 1 \Longrightarrow \nu_{i,j}^t \le M_2$ . Since  $M_2$  is arbitrarily large, this means that  $\nu_{i,j}^t$  can arbitrarily verify this condition. In other words, this means that if  $(u_i^t, u_j^t)$  is a reuse arc, then its reuse distance can be arbitrarily large too.

We can decide for a proper finite value for  $M_2$  that verifies Inequality 4:

By assumption  $\nu_{i,j}^t \leq \mathcal{R}^t \Longrightarrow \nu_{i,j}^t \leq \max_{t \in \mathcal{T}} \mathcal{R}^t$ . We can deduce a finite value for  $M_2$  as  $M_2 = \max_{t \in \mathcal{T}} \mathcal{R}^t$ . The formal result of our lemma is directly deduced from the assumption that  $\nu_{i,j}^t \leq \mathcal{R}^t$ , and by setting the natural number  $x = \mathcal{R}^t - \nu_{i,j}^t$ , we have obviously  $\nu_{i,j}^t + x \leq M_2$ . The next section checks that  $\nu_{i,j}^t + x$  also verifies the other linear constraints.

### **3.3** Storage Constraints on $\nu^t$ Variables (Inequality 3)

The other constraints on  $\nu$  variables are those of Inequality 3:

$$\begin{split} \sigma_j - \sigma_{K_i} + II \times \nu_{i,j}^t + M_1 \times (1 - \theta_{i,j}^t) &\geq -\delta_{w,t}(u_j) \Longrightarrow \nu_{i,j}^t \geq \frac{-\sigma_j + \sigma_{K_i} - M_1 \times (1 - \theta_{i,j}^t) - \delta_{w,t}(u_j)}{II} \\ \text{Since } x = \mathcal{R}^t - \nu_{i,j}^t \geq 0 \Longrightarrow \nu_{i,j}^t + x \geq \frac{-\sigma_j + \sigma_{K_i} - M_1 \times (1 - \theta_{i,j}^t) - \delta_{w,t}(u_j)}{II} \end{split}$$

This means that the value  $\nu_{i,j}^t + x$  verifies the storage constraints too. Consequently, it constitutes a valid reuse distance.

┛

For clarity, we first present a solution to Problem 1 in the case of a single register type.

### 4 Algorithmic Solution for Unroll Factor Minimisation: Single Register Type

In this section, we solve the problem of minimal unroll degree in the case of a single register type, based on reuse graphs (unscheduled loops). When we consider a single register type, then we have a single reuse graph for the considered register type. The formula for computing the unrolling degree becomes equal to a single LCM of the weights of the reuse circuits of the implicit register type. By replacing the notations of  $\mu_{i,t}$  ( $r_{i,t}$  and  $R^t$  resp.) by  $\mu_i$  ( $r_i$  and R resp.), Problem 1 amounts to the following one.

**Problem 2 (LCM-MIN)** Let  $R \in \mathbb{N}$  be the number of remaining registers. Let  $\mu_1, \ldots, \mu_k \in \mathbb{N}$  be the weights of the reuse circuits. Compute the added registers  $r_1, \ldots, r_k \in \mathbb{N}$  such that:

- 1.  $\sum_{i=1}^{k} r_i \leq R$  (validity constraints)

- 2.  $lcm(\mu_1 + r_1, \ldots, \mu_k + r_k)$  is minimal (optimisation objective).

To our knowledge, Problem 2 has no simple, closed-form solution, and its algorithmic complexity is still an open problem<sup>3</sup>.

Before stating our solution for Problem 2, we propose to find a solution for a sub-problem that we call *Fixed* Loop Unrolling Problem. The solution of this sub-problem constitutes the basis of the solution of Problem 2. The Fixed Loop Unrolling Problem proposes to find, for a fixed unrolling degree  $\beta$ , the number of registers that should be added to each circuit to ensure that the size of each circuit is a divisor of  $\beta$ . That is, we find the number of registers added to each circuit  $r_1, ..., r_k$  such that  $\sum_{i=1}^k r_i \leq R$  and  $\beta$  is a common multiple of the different updated weights  $\mu_1 + r_1, ..., + \mu_k + r_k$ . A formal description is given in the next section.

### 4.1 Fixed Loop Unrolling Problem

We formulate the Fixed Loop Unrolling Problem as follow:

**Problem 3 (Fixed Loop Unrolling Problem)** Let  $R \in \mathbb{N}$  be the number of remaining registers. Let  $\mu_1, \ldots, \mu_k \in \mathbb{N}$  be the weights of the reuse circuits. Given a positive integer  $\beta$ , compute the different added registers  $r_1, \ldots, r_k \in \mathbb{N}$  such that:

1.  $\sum_{i=1}^{k} r_i \leq R$

2.  $\beta$  is the common multiple of the news circuits weights  $\mu_1 + r_1, \ldots, \mu_k + r_k$

To improve readability, we use CM to denote common multiple.

Before describing our solution for Problem 3, we state Lemma 2 and Lemma 3 that we need to use afterwards.

Lemma 2 Let us note some properties of the Fixed Loop Unrolling Problem:

- 1.  $\beta \ge \max_i \mu_i \Longrightarrow \exists (r_1, \ldots, r_k) \in \mathbb{N}^k$  such that:  $CM(\mu_1 + r_1, \ldots, \mu_k + r_k) = \beta$

- 2. Let  $r_1, \ldots, r_k$  be the solution of Problem 3 such that  $\sum_{i=1}^k r_i$  is minimal. If  $\sum_{i=1}^k r_i > R$  then Fixed Loop Unrolling Problem *cannot be solved*.

#### **Proof:**

• The first issue can be proved by finding an obvious list of added registers

$(r_1,\ldots,r_k) \in \mathbb{N}^k$  such that:  $CM(\mu_1+r_1,\ldots,\mu_k+r_k) = \beta$

Let us assume that  $\beta \geq \max_i \mu_i$ . If we put  $\forall i = 1, k : r_i = \beta - \mu_i$  then

$$orall i=1,k:\ r_i\geq 0$$

and  $CM(\mu_1+r_1,\ldots,\mu_k+r_k)=eta$  because  $orall i=1,k:\ \mu_i+r_i=eta$

• The second issue can be proved by contradiction.

<sup>&</sup>lt;sup>3</sup>Indeed, a similar reduced problem exists in cryptography theory: Given two natural numbers a, b, compute  $x \le R^t \in \mathbb{N}$  such that gcd(a, b+x) is maximal (gcd denotes the greatest common divisor, GCD). This GCD maximisation problem is defined for two integers only, it is equivalent to minimising the LCM of two integers because  $lcm(a, b) = \frac{a \times b}{gcd(a, b)}$ . The GCD maximisation problem of two integers is known to be equivalent to the integer factorisation problem: the decision problem of integer factorisation has unknown complexity class till now. It is currently solved with approximate methods devoted to very large numbers [14]. Problem 2 is a generalisation of the GCD maximisation problem. The heuristic presented in [14] is not appropriate in our case because: 1) The problem tackled in [14] deals with two integers only, that we cannot generalise to minimise the LCM to multiple integers because  $LCM(x_0, \dots, x_k) \neq \frac{x_0 \times \dots \times x_k}{gcd(x_0, \dots, x_k)}$  for k > 2. 2) We deal with multiple small numbers (in practice,  $R \leq 128$ ), allowing to design optimal methods efficient in practice instead of heuristics.

Let us assume that we find another solution  $r'_1, \ldots, r'_k$  for the problem 3 such that  $\sum_{i=1}^k r'_i \leq R$ . However, in the second part of Lemma 2, we find a list of added register  $r_1, \ldots, r_k$  such that  $\sum_{i=1}^k r_i$  is minimal. Consequently,

$$\sum_{i=1}^{k} r_i \leq \sum_{i=1}^{k} r'_i \text{ (by assumption, it is minimal)} \implies R < \sum_{i=1}^{k} r_i \leq \sum_{i=1}^{k} r'_i$$

which constitues a contradiction with  $\sum_{i=1}^{k} r'_i \leq R$ .

Thus, if there exists a list of added registers which fulfill the constraints of the problem 3 such that  $\sum_{i=1}^{k} r_i$  minimal > R then Fixed Loop Unrolling Problem cannot be resolved.

**Lemma 3** Let  $\beta$  be a positive integer and  $D_{\beta}$  be the set of its divisors. Let  $\mu_1, \ldots, \mu_k \in \mathbb{N}$  be the weights of the reuse circuits. If we find a list of the added registers  $r_1, \ldots, r_k \in \mathbb{N}$  for Problem 3, then we have the following results:

$$1. \ \beta = CM(\mu_1 + r_1, \dots, \mu_k + r_k) \Rightarrow \forall i = 1, k : \beta \ge \mu_i$$

$$2. \ \beta = CM(\mu_1 + r_1, \dots, \mu_k + r_k) \Rightarrow \forall i = 1, k : \exists d_i, \ r_i = d_i - \mu_i \text{ with } d_i \in D_\beta \land d_i \ge \mu_i.$$

#### **Proof:**

The first issue can be proved as follows:

$\beta$  is the common multiple (CM) of the news circuits weights  $\mu_1 + r_1, \ldots, \mu_k + r_k$

$$\Rightarrow \forall i = 1, k: \ \beta \ge \mu_i + r_i \tag{7}$$

From (7) we have:

$$\forall i = 1, k: \ \beta \ge \mu_i + r_i \Rightarrow \forall i = 1, k: \ \beta - \mu_i \ge r_i$$

(8)

From (8) we have:

$\forall i = 1, k: \ \beta \ge \mu_i \text{ because } \forall i = 1, k: \ r_i \ge 0 \text{ (each } r_i \in \mathbb{N})$

The first issue is proved.

The second issue can be proved by using the definition of the common multiple (CM) of a set of positive integers. Hence, we have:

$\beta$  is the common multiple (CM) of the news circuits weights  $\mu_1 + r_1, \ldots, \mu_k + r_k$

$$\Rightarrow \forall i = 1, k: \ \mu_i + r_i \text{ is a divisor of } \beta \tag{9}$$

From (9) we have:

$\forall i = 1, k : \mu_i + r_i \text{ is a divisor of } \beta$

$$\Rightarrow \forall i = 1, k : \exists d_i \in D_\beta \mid \mu_i + r_i = d_i \tag{10}$$

From (10) we find:

$$\begin{cases} \forall i = 1, k : r_i \ge 0 \\ \exists d_i \in D_\beta \mid \mu_i + r_i = d_i \end{cases} \Rightarrow \begin{cases} \forall i = 1, k \\ \exists d_i \in D_\beta \\ r_i = d_i - \mu_i \\ \text{with } d_i \ge \mu_i \end{cases}$$

The second issue of Lemma 3 is proved.

After proving Lemma 3 and by using Lemma 2, we describe our solution for the *Fixed Loop Unrolling Problem* in the next section.

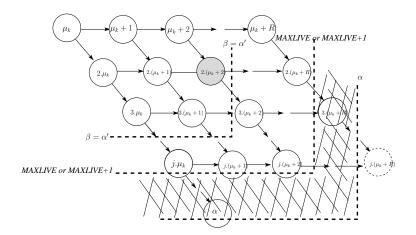

Figure 6: Graphical solution for the fixed loop unrolling problem

#### 4.2 Solution for the Fixed Loop Unrolling Problem

**Proposition 1** Let  $\beta$  be a positive integer and  $D_{\beta}$  be the set of its divisors. Let R be the number of remaining registers. Let  $\mu_1, \ldots, \mu_k \in \mathbb{N}$  be the weights of the reuse circuits. A minimal list of the added registers  $(r_1, \ldots, r_k \in \mathbb{N}$  with  $\sum_{i=1}^k r_i$  is minimal ) can be found by adding to each reuse circuit  $\mu_i$  a minimal value  $r_i$  such as  $r_i = d_i - \mu_i$  with  $d_i = \min\{d \in D_{\beta} \mid d \ge \mu_i\}$ . If we denote CM as common multiple then the two following implications are true:

- 1.  $\beta = CM(\mu_1 + r_1, \dots, \mu_k + r_k) \land \sum_{i=1}^k r_i \leq R \Rightarrow we find a solution for Problem 3;$

- 2.  $\beta = CM(\mu_1 + r_1, \dots, \mu_k + r_k) \land \sum_{i=1}^k r_i > R \Rightarrow Problem 3 has no solution.$

#### **Proof:**

In Lemma 3, we have proved that:

$$\beta = CM(\mu_1 + r_1, \dots, \mu_k + r_k) \Longrightarrow \forall i = 1, k : \exists d_i \in D_\beta \mid r_i = d_i - \mu_i \land d_i \ge \mu_i$$

(11)

From Equation (11) we have:

$$r_i$$

is minimal  $\Rightarrow d_i$  is the smallest divisor of  $\beta \ge \mu_i$  (12)

From Equation (12) a list of the added registers  $r_1, \ldots, r_k$  with  $\sum_{i=1}^k r_i$  is minimal can be defined as follows:

$$\forall i = 1, k : r_i \text{ is minimal } \Longrightarrow \forall i = 1, k : r_i = d_i - \mu_i \land d_i = \min\{d \in D_\beta \mid d \ge \mu_i\}$$

According to Lemma 2, if we find a list of the added registers (the different values of  $r_i$ ) among the remaining registers such as  $\sum_{i=1}^{k} r_i$  is minimal  $\leq R$  then these different values of  $r_i$  can be a solution for the *Fixed Loop Unrolling Problem*. Otherwise, if  $\sum_{i=1}^{k} r_i$  is minimal > R then we are sure that there are no solution for Problem 3.

┛

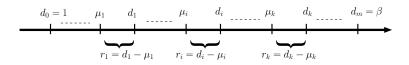

Figure 6 represents a graphical solution for the *Fixed Loop Unrolling Problem*. We assume that the different weights and the different divisors of  $\beta$  are sorted on the same axis in an ascending order.

Algorithm 1 implements our solution for the *Fixed Loop Unrolling Problem*. This algorithm tries to divide R the remaining registers among the circuits to achieve a fixed common multiple of k integers (the different weights of reuse circuits  $\mu_i$ ). It checks if  $\beta$  can become the new loop unrolling degree. For this purpose, Algorithm 1 uses Algorithm 2 that returns the smallest divisor just after an integer value. Algorithm 1 finds out the list of added registers among the remaining registers R between the reuse circuits (the different values of  $r_i \forall i = 1, k$ ), if such list of added registers exists. It returns also a boolean *success* which takes the following values:

$$success = \begin{cases} \mathbf{true} & \text{if } \sum_{i=1}^{k} r_i \leq R \\ \mathbf{false} & \text{otherwise} \end{cases}$$

The maximal algorithmic complexity of the Fixed Loop Unrolling Problem is then dominated by the while loop:  $\mathcal{O}((\mathcal{R}^t)^2)$ .

Algorithm 1 Fixed loop unrolling problem

**Require:** *k*: the number of reuse circuits;  $\mu_i$ : the different weights of reuse circuits;  $\mathcal{R}^t$ : the number of architectural registers, and  $\beta$ : the loop unrolling degree

**Ensure:** the different added registers  $r_1, \ldots, r_k$  with  $\sum_{i=1}^k r_i \text{ minimal if it exists and a boolean success}$  $R = \mathcal{R}^t - \sum_{1 \le i \le k} \mu_i \{ \text{the remaining register} \}$  $\text{sum} \leftarrow 0$ success  $\leftarrow$  true {defines if we find a valid solution for the different added registers}  $i \leftarrow 1$  {represents the number of reuse circuits}  $D \leftarrow \text{DIVISORS}(\beta, \mathcal{R}^t)$  {calculate the sorted list of divisors of  $\beta$  that are  $\leq \mathcal{R}^t$  including  $\beta$ } while  $i \leq k \wedge success$  do  $d_i \leftarrow \text{DIV}_\text{NEAR}(\mu_i, D)$  {DIV\_NEAR returns the smallest divisors of  $\beta$  greater or equal to  $\mu_i$ }  $r_i \leftarrow d_i - \mu_i$  $\operatorname{sum} \leftarrow \operatorname{sum} + r_i$ if sum > R then  $success \leftarrow false$ else  $i \leftarrow i + 1$ end if end while return  $(r_1, \ldots, r_k)$ , success

#### Algorithm 2 DIV\_NEAR

**Require:**  $\mu_i$ : the weight of the reuse circuits;  $D = (d_1, \ldots, d_n)$ : the *n* divisors of  $\beta$  sorted by ascending order **Ensure:**  $d_i$  the smallest divisors of  $\beta$  greater or equal to  $\mu_i$  $i \leftarrow 1$  {represents the index of the divisor of  $\beta$ }

while  $i \le n$  do if  $d_i \ge \mu_i$  then return  $(d_i)$ end if  $i \leftarrow i + 1$ end while

### Algorithm 3 DIVISORS

**Require:**  $\beta$ : the loop unrolling degree;  $\mathcal{R}^t$ : the number of architectural registers **Ensure:** D the list of the divisors of  $\beta$  that are  $\leq \mathcal{R}^t$ , including  $\beta$ bound  $\leftarrow \min(\mathcal{R}^t, \beta/2)$   $D \leftarrow \{1\}$  **for** d = 2 to bound **do if**  $\beta \mod d = 0$  **then**   $D \leftarrow D \cup \{d\}$  {Keep the list ordered in ascending order} **end if end for**   $D = D \cup \{\beta\}$ **return** (D)

#### Analysis of the Complexity of Algorithm 1

- Regarding the DIVISORS algorithm:

- The maximal number of iterations is bound  $\leq \mathcal{R}^t$ .

- Inserting an element inside the list costs at most  $\log(\mathcal{R}^t)$ .

- The maximal complexity of DIVISORS algorithm is  $O(\mathcal{R}^t \times \log(\mathcal{R}^t))$ .

- Regarding the DIV\_NEAR algorithm:  $O(n) \leq O(\mathcal{R}^t)$ .

- Regarding the Fixed Loop Unrolling Problem algorithm:

- Calling DIVISORS costs  $O(\mathcal{R}^t \times \log(\mathcal{R}^t))$ .

- The while loop iterates at most  $k \leq \mathcal{R}^t$  times.

- At each iteration, calling DIV\_NEAR costs  $O(\mathcal{R}^t)$ .

- The maximal algorithmic complexity of the Fixed Loop Unrolling Problem is then dominated by the while loop:  $O((\mathcal{R}^t)^2)$ .

The solution of the *Fixed Loop Unrolling Problem* constitutes the basis of a solution for the *LCM-MIN Problem* explained in the next section.

### 4.3 Solution for LCM-MIN Problem

For the solution of the *LCM-MIN Problem* (Problem 2) we use the solution of the *Fixed Loop Unrolling Problem* and the result of Lemma 3. According to Lemma 3, the solution space S for  $\alpha^*$  (the solution of *LCM-MIN Problem*) is bounded by  $\alpha$ , the initial unroll factor.

$$\begin{cases} \forall i = 1, k : \alpha^* \ge \mu_i \text{ (From Lemma 3)} \\ \alpha^* \le \alpha \end{cases} \Rightarrow \max_{1 \le i \le k} \mu_i \le \alpha^* \le \alpha \end{cases}$$

In addition,  $\alpha^*$  is a multiple of each  $\mu_i + r_i$  with  $0 \le r_i \le R$ . If we assume that  $\mu_k = \max_{1 \le i \le k} \mu_i$  then  $\alpha^*$  is a multiple of  $\mu_k + r_k$  with  $0 \le r_k \le R$ . Furthermore, the solution space S can be defined as follows:

$$S = \{\beta \in \mathbb{N} \mid \beta \text{ is multiple of } (\mu_k + r_k) \forall r_k = 0, R \land \mu_k \le \beta \le \alpha \}$$

After describing the set S of all possible values of  $\alpha^*$ . The minimal  $\alpha^*$ , that is the solution for Problem 2, is defined as follows:

$$\alpha^* = \min\{\beta \in S | \exists (r_1, \dots, r_k) \in \mathbb{N}^k \land lcm(\mu_1 + r_1, \dots, \mu_k + r_k) = \beta \land \sum_{i=1}^k r_i \le R\}$$

Figure 7 portrays all values of the set S as a partial lattice. An arrow between two nodes means that the value in the first node is less than the value of the second node:  $a \to b \Longrightarrow a < b$ . The value  $\mu_k$  represents the value of the reuse circuit number k. Because we assumed that  $\mu$  values are sorted in ascending order,  $\mu_k$  is the highest weight of all reuse circuits.  $\alpha$  is the initial loop unrolling value. Each node is a potential solution ( $\beta$ ) which can be considered as the minimal loop unrolling degree. A dashed node can not be a potential candidate because its value is greater than  $\alpha$ . Let  $\tau = \alpha \operatorname{div} \mu_k$  be the number of the lines of the lattice. Each line describes a set of multiples. For example, the line j describes a set of multiples  $S_j = \{\beta | \exists r_k, 0 \le r_k \le R^t, \beta = j \times (\mu_k + r_k) \land \beta \le \alpha\}$

In order to find  $\alpha^*$ , the minimal unroll factor, our solution consists in checking if each node of S can be a solution for the *Fixed Loop Unrolling Problem*: at last we are sure that the minimum of all these values is the minimal loop unrolling degree.

Despite traversing all the nodes of S, we describe in Figure 7 an efficient way to find the minimal  $\alpha^*$ . We proceed line by line in the figure. In each line, we apply Algorithm 1 to each node until the value of the predicate success returned by Algorithm 1 is **true** or until we arrive at the last line when  $\beta = \alpha$ . If the value  $\beta$  of the node i of the line j verifies the predicate (success = **true**), then we have two cases:

- 1. If the value of this node is less than the value of the first node of the next line then we are sure that this value is optimal ( $\alpha^* = \beta$ ). This is because all the remaining nodes are greater than  $\beta$  (by construction of the lattice S).

- Else we have found a unroll factor less than the original α. We note this new value α' and we try once again to minimise it until we find the minimal (the first case). The search space shrinks: S' = {β ∈ N|∀r<sub>k</sub> = 0..R : β is multiple of (μ<sub>k</sub> + r<sub>k</sub>) ∧ (j + 1) × μ<sub>k</sub> ≤ β ≤ α'}.

Algorithm 4 implements our solution for the *LCM-MIN Problem*. This algorithm minimises the loop unrolling degree  $\alpha$  which is the least common multiple of k reuse circuits whose weights are  $\mu_1, \ldots, \mu_k$ . Our method is based on using the remaining registers R. This algorithm computes  $\alpha^*$  the minimal value of loop unrolling degree and the minimal list  $r_1, \ldots, r_k$  of the added registers to the different reuse circuits.

Figure 7: How to traverse the lattice S

Listing 2: Example of a sequential kernel code generation for the register type  $t_1$

```

FOR i=0, i<N, i=i+3

u 1(i)

: R1 = ...

u_2(i)

:

u 3(i)

: R4 = R3...

u_4(i)

: ...= R4...

u_1(i+1): R2 = ...

u_2(i+1):

u_3(i+1): R5 = R1...

u_4(i+1): ...= R5...

u_1(i+2): R3 = ...

u_2(i+2):

u_3(i+2): R6 = R2...

u_4(i+2): ...= R6...

ENDFOR

```

Algorithmic Complexity Analysis of Algorithm 4 In the worst case, Algorithm 1 is processed on all the nodes of the set S in Figure 7. The set S has  $\frac{R \times \alpha}{\mu_k}$  nodes  $(\mu_k = \max \mu_i \text{ and } \alpha = lcm(\mu_1, ..., \mu_k))$ . We know that  $1 \le \mu_k \le \mathcal{R}^t$ . Consequently, the size of the set S is less or equal to  $R^t \times \alpha$ . On each node, we process Algorithm 1. Hence, the maximal algorithmic complexity of is  $O(R \times \alpha \times (\mathcal{R}^t)^2) = O(R \times (\mathcal{R}^t)^2 \times lcm(\mu_1, ..., \mu_k))$ .

**Example 2** Let us come back to the example of Figure 5 on page 8, but we focus on the single register type  $t_1$ , and we neglect the other register type  $t_2$ . There are initially two reuse circuits with two costs  $\mu_1 = \nu^{t_1}(u_1, u_1) = 3$ , and  $\mu_2 = \nu^{t_1}(u_3, u_3) = 2$ . Thus, as shown in Ex. 1, the initial unroll factor is equal to lcm(3, 2) = 6. It is easy to see that if we increment the reuse distance  $\nu^{t_1}(u_3, u_3)$  from 2 to 3, then the cost of the reuse circuit  $(u_3, u_3)$  becomes equal to 3, and hence the unroll factor becomes equal to lcm(3, 3) = 3 instead of 6. The new number of allocated registers becomes equal to  $RC^{t_1} = 3 + 3$  instead of 5 initially. A valid kernel code generation with 6 registers of type  $t_1$  and an unroll factor equal to 3 is given in Listing 2.

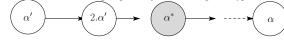

**Example 3** Let us consider a more complex example with a set of five reuse circuits with the respective weights:  $\mu_1 = 3, \mu_2 = 4, \mu_3 = 5, \mu_4 = 7, \mu_5 = 8$ . The initial number of allocated registers is equal to RC = 3 + 4 + 5 + 7 + 8 = 27. The loop unrolling degree  $\alpha$  is their least common multiple ( $\alpha = lcm(3, 4, 5, 7, 8) = 840$ ). Let us assume that we have  $\mathcal{R}^t = 32$  architectural registers in the target processor. So hence we have R = 32 - 27 = 5 remaining registers. By applying Algorithm 4, we find that the minimal numbers of registers added to each reuse

### Algorithm 4 LCM-MIN algorithm

```

Require: k: the number of reuse circuits; \mu_i: the weights of the reuse circuits; \mathcal{R}^t: the number of architectural registers; \alpha: the

initial loop unrolling degree

Ensure: the minimal loop unrolling degree \alpha^* and a list r_1, \ldots, r_k of added registers with \sum_{i=1}^k r_i minimal

R = \mathcal{R}^t - \sum_{1 \le i \le k} \mu_i \{\text{The remaining registers}\}

\alpha^* \leftarrow \mu_k \{ \min \overline{\text{mal}} \text{ value of loop unrolling } \alpha^* \}

if \alpha = \alpha^* \lor R = 0 then

if R = 0 then

\alpha^* \leftarrow \alpha \{\alpha \text{ nothing can be done, no remaining registers}\}

end if

else

r_k \leftarrow 0 {number of registers added to the reuse circuit \mu_k}

\beta \leftarrow \mu_k {value of the first node in the set S}

j \leftarrow 1 {line number j in the set S}

\tau \leftarrow \alpha \ div \ \mu_k {total number of lines in the set S}

stop \leftarrow false \{stop = true \text{ if the minimal is found}\}

success \leftarrow false \{ predicate returned by Algorithm 1 \}

while \beta \leq \alpha \land \neg stop \operatorname{do}

{Traversing the set S until we find the minimal loop unrolling factor}

success \leftarrow Fixed_Unrolling_Problem(k, \mu_i, \mathcal{R}^t, \beta) {Apply for each node the Algorithm 1}

if \neg success then

if r_k < R then

r_k ++ \{we go to the next node on the same line\}

else

r_k \leftarrow 0 {we go to the first node of the next line}

j^{++}

end if

\beta \leftarrow j \times (\mu_k + r_k) {compute the new value of the potential new unrolling factor \beta}

if \beta > \alpha \wedge j < \tau then

{ignore the dashed node}

r_k \leftarrow 0 {dashed node, we go to the first node of the next line}

j^{++}

\beta \leftarrow j \times \mu_k

end if

else

\alpha^* \leftarrow \beta \{ \beta \text{ may be the minimal loop unrolling degree} \}

if \alpha^* \leq (j+1) \times \mu_k then

stop \leftarrow true \{ we are sure that \alpha^* is the minimal loop unrolling degree \} \}

else

\alpha \leftarrow \alpha^* {we find a new value of \alpha to minimise}

\tau \leftarrow \alpha \ div \ \mu_k

r_k \leftarrow 0

j^{++}

\beta \leftarrow j \times \mu_k

end if

end if

end while

end if

```

circuits are  $r_1 = 1, r_2 = 0, r_3 = 3, r_4 = 1, r_5 = 0$ . The new reuse circuits' weights become  $\mu_1 = 3 + 1 = 4$ ,  $\mu_2 = 4 + 0 = 4, \mu_3 = 5 + 3 = 8, \mu_4 = 7 + 1 = 8, \mu_5 + 0 = 8$ . The new number of allocated registers become equal to 4 + 4 + 8 + 8 = 32. The new unroll factor becomes equal to  $\alpha^* = lcm(4, 4, 8, 8, 8) = 8$ , which means that we reduced it by a ratio  $= \frac{\alpha}{\alpha^*} = 105$ .

The next section extends the algorithm of unroll factor minimisation to the case of multiple register types.

### **5** Unroll Factor Minimisation in the Presence of Multiple Register Types

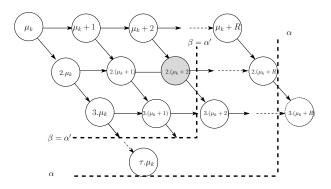

In the presence of multiple register types, minimising the loop unrolling degree of each type separately does not lead to the minimal loop unrolling degree for the whole loop, as illustrated in the following example.

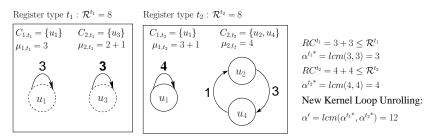

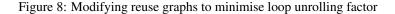

**Example 4** Let us return to the example in Figure 5 on page 8. We want to minimise the loop unrolling degree of the initial reuse graph in Figure 5(b), where two register types  $t_1$ ,  $t_2$  are considered. The initial kernel loop unrolling degree  $\alpha = 12$  is the LCM of  $\alpha^{t_1} = 6$  and  $\alpha^{t_2} = 12$  which are respectively the LCM of the different reuse circuits weights for each register type. In this configuration, let us assume that we have  $\mathcal{R}^{t_j} = 8$  available architectural registers in the processor for each register type  $t_j$ . Hence we have  $\mathcal{R}^{t_1} = 8 - 5 = 3$  (resp  $\mathcal{R}^{t_2} = 1$ ) remaining registers for register type  $t_1$  (resp  $t_2$ ). By applying the loop unrolling minimisation for each register type separately as studied in Section 4, the minimal loop unrolling degree for each register type becomes:  $\alpha^{t_1*} = 3$  for register type  $t_1$  and  $\alpha^{t_2*} = 4$  for register type  $t_2$ , see Figure 8(a). However, the global kernel loop unrolling degree is not minimal  $\alpha' = lcm(\alpha^{t_1*}, \alpha^{t_2*}) = 12$ . The minimal global kernel loop unrolling degree is computed below.

In Figure 8(b), we provide a solution where the minimal loop unrolling degree is  $\alpha^* = 4 < \alpha'$ . The unroll factor of  $t_1$  is equal to 4, which is not its minimal value (equal to 3 as shown above). However, the global unroll factor that satisfies both  $t_1$  and  $t_2$  is minimal and equal to 4. The minimal number of registers added to each reuse circuit of each type are:  $r_{1,t_1} = 1$ ,  $r_{2,t_1} = 0$ ,  $r_{1,t_2} = 1$ ,  $r_{2,t_2} = 0$ . Note that  $r_{i,t_j}$  is the number of registers added to the  $i^{th}$  reuse circuit of the type  $t_j$ . Our method explained in the following sections guarantees that the new number of allocated registers will not exceed the number of architectural registers for each register type  $t_j$ .

Now let us examine an example of a valid code generation associated to the reuse graphs of Figure 8(b), even though at this stage of compilation, the loop is not yet scheduled. Listing 3 shows a kernel code generation for the register type  $t_1$  only: registers of type  $t_1$  are named with the prefix R. The number of allocated registers is  $RC^{t_1} =$ 4 + 2 = 6 and the unroll factor is equal to 4. Listing 4 shows a kernel code generation for the register type  $t_2$  only: registers of type  $t_2$  are named with the prefix S. The number of allocated registers is  $RC^{t_2} = 4 + (1 + 3) = 8$  and the unroll factor is equal to 4. The kernel code generation that is correct for both  $t_1$  and  $t_2$  is given in Listing 5 and the unroll factor is minimal and equal to 4: note that the statement  $u_1$  has two destination registers of two distinct types, as previously illustrated in the DDG of Figure 5(a). As can be seen, the initial unroll factor was equal to 12, as computed in Example 1 in page 9, we minimise it here to 4, which is the optimal value. We also guarantee that the number of extra used registers does not exceed the number of remaining registers.

| Listing 5. Kerner code generation for register type $t_1$                      | Eisting 4. Reflet code generation for register type $t_2$ |

|--------------------------------------------------------------------------------|-----------------------------------------------------------|

| FOR i=0, i <n, i="i+4&lt;/td"><td>FOR i=0, i<n, i="i+4&lt;/td"></n,></td></n,> | FOR i=0, i <n, i="i+4&lt;/td"></n,>                       |

| u_1(i): R1 =                                                                   | $u_1(i): S1 = S7 + \dots$                                 |

| u_2(i):                                                                        | $u_2(i): S5 = S1 + \dots$                                 |

| $u_3(i): R5 = R4 + \dots$                                                      | u_3(i):                                                   |

| u_4(i):= R5 +                                                                  | $u_4(i): S6 = S8 + S5$                                    |

|                                                                                |                                                           |

| u_1(i+1): R2 =                                                                 | $u_1(i+1): S2 = S8 + \dots$                               |

| u_2(i+1):                                                                      | $u_2(i+1): S6 = S2 + \dots$                               |

| u_3(i+1): R6 = R1 +                                                            | u_3(i+1):                                                 |

| u_4(i+1):= R6 +                                                                | u_4(i+1): S7= S5 + S6                                     |

|                                                                                |                                                           |

| u_1(i+2): R3 =                                                                 | $u_1(i+2): S3 = S5 + \dots$                               |

| u_2(i+2):                                                                      | $u_2(i+2): S7 = S3 + \dots$                               |

| u_3(i+2): R5= R2 +                                                             | u_3(i+2):                                                 |

| u_4(i+2):= R5 +                                                                | $u_4(i+2): S8 = S6 + S7$                                  |

|                                                                                |                                                           |

| u_1(i+3): R4=                                                                  | $u_1(i+3): S4 = S6 + \dots$                               |

| u_2(i+3):                                                                      | $u_2(i+3): S8 = S4 + \dots$                               |

| $u_3(i+3): R6 = R3 + \dots$                                                    | u_3(i+3):                                                 |

| u_4(i+4):= R6 +                                                                | $u_4(i+4): S5 = S7 + S8$                                  |

| ENDFOR                                                                         | ENDFOR                                                    |

|                                                                                |                                                           |

Listing 3: Kernel code generation for register type  $t_1$

Listing 4: Kernel code generation for register type  $t_2$

(a) Minimising Loop Unrolling for Each Register Type Separately

(b) Minimising Loop Unrolling for all Register Types Conjointly

Listing 5: Kernel code generation for the two register types conjointly

```

FOR i=0, i<N, i=i+4

u_1(i): R1, S1 = S7

u_2(i): S5 = S1

u_3(i): R5 = R4

u_4(i): S6 = S8 + S5 + R5

u_1(i+1): R2, S2 = S8

u_2(i+1): S6 = S2

u_3(i+1): R6 = R1

u_4(i+1): S7= S5 + S6 + R6

u_1(i+2): R3, S3 = S5

u_2(i+2): S7 = S3

u_3(i+2): R5 = R4

u_4(i+2): S8 = S6 + S7 + R5

u_1(i+3): R4, S4 = S6

u_2(i+3): S8 = S4

u_3(i+3): R6 = R3

u_4(i+4): S5 = S7 + S8 + R6

ENDFOR

```

The following section defines the search space S for the minimal kernel loop unrolling  $\alpha^*$ .

### 5.1 Search Space for Minimal Kernel Loop Unrolling

According to the properties of LCM and to the formulation of Problem 1, the search space S for the minimal kernel loop unrolling  $\alpha^*$  is bounded. In fact, three cases arise:

Case 1: No remaining registers for all the different register types In this case, the initial loop unrolling degree cannot be minimised  $\alpha^* = \alpha$ .

Case 2: No remaining registers for some register types Assume that  $\alpha^j$  is the loop unrolling degree for the register type  $t_j \in \mathcal{T}$ . In this way,  $\alpha = lcm(\alpha^1, \ldots, \alpha^n)$ . We define the subset  $\mathcal{T}'$  which contains all the register types such that there are no remaining registers for these register types after periodic register allocation ( $\mathcal{T}' \subset \mathcal{T}$  such that  $\mathcal{T}' = \{t \in \mathcal{T} \mid R^t = 0\}$ ). If there are no registers left for these register types, we cannot minimise their loop unrolling degrees, see Section 4. Therefore, the minimal global loop unrolling degree  $\alpha^* \geq \alpha^j \forall t_j \in \mathcal{T}'$ . By considering  $\alpha' = lcm_{t\in\mathcal{T}'}(\alpha^t)$ , we have the following inequality:

$$\alpha' \le \alpha^* \le \alpha \tag{13}$$

In addition, from LCM properties:

$$\alpha^*$$

is multiple of  $\alpha'$  (14)

From Equation 13 and Equation 14, the search space S is defined as follows:

$$S = \{\beta \in \mathbb{N} \mid \beta \text{ is multiple of } \alpha' \land \alpha' \leq \beta \leq \alpha\}$$

Here, each value  $\beta$  can be a potential final loop unrolling degree.

**Case 3: All register types have some remaining registers** From the associative property of LCM, we have:

$$\alpha^* = lcm(lcm(\mu_{1,t_1} + r_{1,t_1}, \dots, \mu_{k_1,t_1} + r_{k_1,t_1}), \dots, lcm(\mu_{1,t_n} + r_{1,t_n}, \dots, \mu_{k_n,t_n} + r_{k_n,t_n}))$$

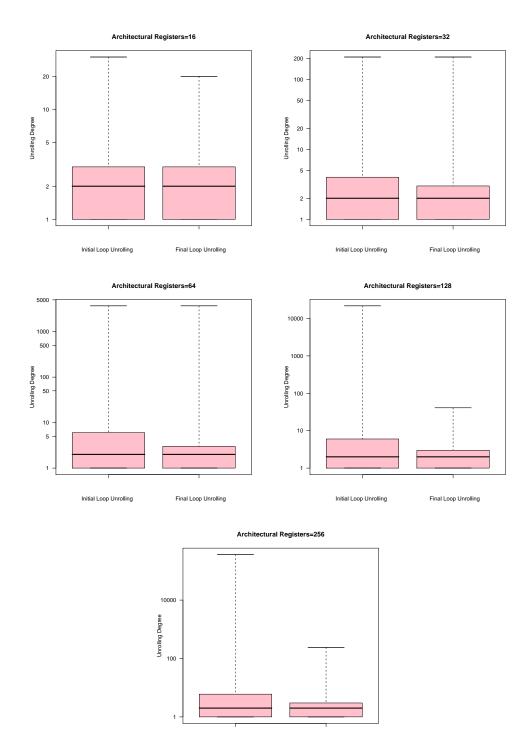

$$\implies \alpha^* = lcm(\mu_{1,t_1} + r_{1,t_1}, \dots, \mu_{k_1,t_1} + r_{k_1,t_1}, \dots, \mu_{1,t_n} + r_{1,t_n}, \dots, \mu_{k_n,t_n} + r_{k_n,t_n})$$