# Efficient Compilation of Esterel for Multi-core Execution Simon Yuan, Li Hsien Yoong, Partha S. Roop

# ▶ To cite this version:

Simon Yuan, Li Hsien Yoong, Partha S. Roop. Efficient Compilation of Esterel for Multi-core Execution. [Research Report] RR-8056, INRIA. 2012. hal-00728149

# HAL Id: hal-00728149 https://inria.hal.science/hal-00728149

Submitted on 5 Sep 2012

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# Efficient Compilation of Esterel for Multi-core Execution

Simon Yuan, Li Hsien Yoong, Partha S Roop

RESEARCH REPORT N° 8056 September 5, 2012 Project-Teams POP ART

# Efficient Compilation of Esterel for Multi-core Execution

Simon Yuan \*, Li Hsien Yoong  $^{\dagger}$ , Partha S Roop  $^{\ddagger}$

Project-Teams POP ART

Research Report n° 8056 — September 5, 2012 — 49 pages

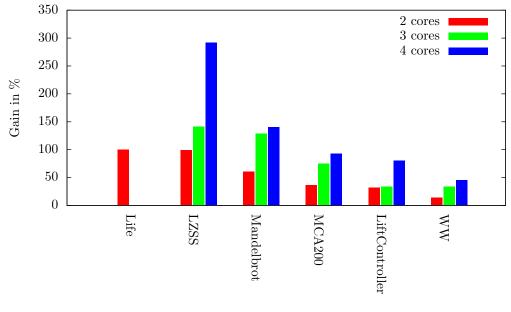

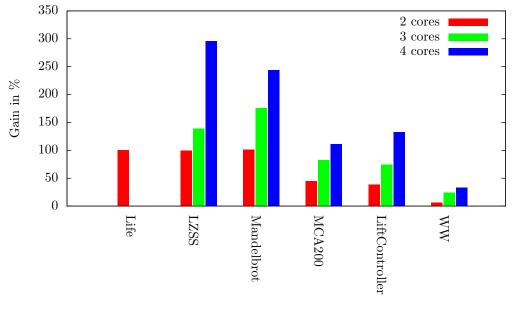

**Abstract:** Recent advances in processor technology have lead to affordable multi-core processors, which could even be used in embedded applications. However, many embedded applications are safety-critical and require suitable abstractions such as the synchronous abstraction. Esterel is one such language belonging to the synchronous family and has been used extensively in the design of safety critical systems. While several compilation techniques of Esterel have been proposed, these are unsuitable for multi-cores due to the inherently sequential approach of *compiling away* the concurrency. We overcome this limitation by proposing two distinct approaches that distribute Esterel threads evenly across multi-core architectures. The first approach statically distributes threads based on the computation intensity approximated by the number of instructions generated from each thread. The second approach distributes threads dynamically using a thread queue that dispatches a thread whenever a core becomes idle. We have performed extensive benchmarking over large Esterel programs to illustrate that, using the static approach, achieving throughput with parallel execution of Esterel is benchmark dependent. However, the dynamic approach not only benefits data-dominated Esterel programs, but also large control-dominated ones. In particular, gains in performance of 36% and 93% were attained for a large control-dominated program using a dual-core and quad-core Microblaze processor, respectively.

Key-words: Multi-core, synchronous languages, Esterel, compilation.

#### RESEARCH CENTRE GRENOBLE – RHÔNE-ALPES

Inovallée 655 avenue de l'Europe Montbonnot 38334 Saint Ismier Cedex

<sup>\*</sup> Department of ECE, University of Auckland, New Zealand iyua002@aucklanduni.ac.nz

$<sup>^\</sup>dagger$  Department of ECE, University of Auckland, New Zealand <code>lyoo002@aucklanduni.ac.nz</code>

<sup>&</sup>lt;sup>‡</sup> Department of ECE, University of Auckland, New Zealand p.roop@auckland.ac.nz. INRIA Pop Art external collaborator funded by the AFMES associated team.

# Compilation efficace d'Esterel pour exécution sur multi-cœurs

Résumé : Les récentes avancées technologiques des processeurs ont rendu abordables les processeurs multi-cœurs qui ont pu être utilisés dans les systèmes embarqués. Cependant, beaucoup de systèmes embarqués ont des contraintes de sécurité qui demandent des abstractions adaptées, comme les abstractions de synchronisation. Esterel est un langage de la famille des langages synchrones, largement utilisé dans l'élaboration de système avec des contraintes de sécurité. Plusieurs techniques de compilation ont été proposées pour Esterel, mais elles ne sont pas adaptables pour les processeurs multi-cœurs en raison du caractère séquentiel intrinsèque à la compilation, loin de la simultanéité. Cette limitation est franchie grâce à deux approches distinctes qui distribuent les threads Esterel uniformément sur l'architecture multi-cœurs. La première approche distribue statiquement les threads issues de l'intensité calculée approximée par le nombre d'instructions générées par chaque thread. La seconde approche distribue dynamiquement les threads en utilisant une file qui envoie les threads lorsqu'un cœur est inactif. Nous avons réalisé d'importants benchmarking sur un grand nombre de programmes Esterel pour illustrer que la réalisation de débit avec l'exécution en parallèle statique de Esterel est dépendante du benchmark. En revanche, l'approche dynamique ne profite pas qu'aux programmes Esterel à dominance de donnée, mais aussi bien à ceux à large dominance de contrôle. En particulier, des gains de performance de 36% et de 93% ont été atteints pour des programmes Esterel à dominance de contrôle en utilisant respectivement un processeur dual-core et un processeur quad-core Microblaze.

Mots-clés : Multi-cœur, programmation synchrone, Esterel, compilation.

Although Esterel is inherently concurrent, Esterel compilers have typically removed the currency away in their implementations and execute sequentially. Parallelizing Esterel programs for better performance is notoriously difficult due to the synchronous semantics of the language. In particular, causality issues introduced by instantaneous broadcast communication put significant effort on the compiler to correctly handle the communication. Hence, there are very minimal attempts to achieve this objective [7, 3, 11]. This paper proceeds to present techniques for implementing the concurrency in Esterel with true parallelism (see [12] for the distinction between concurrency and parallelism).

Implementing parallelism for Esterel in hardware is simpler than software as the synchronous approach is a convenient paradigm for digital hardware design. A global clock is used to advance sequential states, while propagating signals via parallel combinational paths. In software, however, this approach is less natural, as it is difficult to efficiently implement concurrent threads with lock-step synchronization using an OS. This traditional approach of implementing the concurrency with an OS is highly inefficient as large Esterel programs may easily consist of hundreds of threads. If each of these threads are implemented separately on an OS, context-switching cost will be prohibitively high. This is due to each thread having to be scheduled at least once in each clock cycle, and possibly more if inter-thread communication is required. Consequently, software implementations of Esterel have typically compiled the explicit concurrency to yield statically scheduled sequential code that can run directly on a single-core processor [6, 10, 14], including STARPro introduced in [19, 20].

Recent advancements in microelectronics, however, have led to the increasing use of multicore processors to achieve better power-performance tradeoff. As the power consumption of a processor increase by a power of two with respect to its hardware clock frequency, heat and power consumption have become increasingly more difficult to manage. In order to keep up with the demand for more computation power, an alternative approach is to increase the number of core processing units with little to no increase in the processor clock speed. This is possible thanks to the ever advancing silicon processing technologies keeping up with the rate described by Moore's law [13].

To take advantage of multi-core architectures, execution of Esterel has to be distributed. Unfortunately, the static schedule generated by most Esterel compilers is poorly-suited for multicore processors. This paper will present two approaches to overcome this limitation by compiling Esterel in a manner that preserves the concurrency at the source level so that the resulting code can run in parallel on the available cores.

The task of compiling Esterel for efficient parallel execution is challenging due to the following:

- 1. Frequent thread synchronization that is required at the boundary of each clock cycle.

- 2. Instantaneous communication that occurs within a *tick* between multiple threads.

- 3. Distribution of threads to processor cores is intertwined with problem 1 and 2.

These factors limit the amount of parallel execution that can actually take place, irrespective of the number of cores available. Problem 1 and 2 deal with thread scheduling such that the semantics of instantaneous broadcast is strictly obeyed while executing threads in parallel. The implementation of thread scheduling also heavily influences the way threads are distributed as described in problem 3. Despite thread scheduling being tightly coupled to thread distribution, the techniques introduced in this paper is able to divide thread scheduling and distribution into problems that can be solved independently. The key is to resolve the statuses of signals at runtime so that threads can be scheduled dynamically. The dynamic scheduling approach gives more freedom to the thread distribution problem by allowing threads to execute in any arbitrary order. Two approaches for thread distribution will be presented: an approach that statically distribute to cores based on a greedy heuristic, and a dynamic approach where threads are distributed to idle cores at run-time using a FIFO queue.

The remaining of the paper will proceed by introducing Esterel through a small example in Section 1. We will describe dynamic scheduling using the run-time signal resolution technique and its correctness in Section 2. Then, the implementation of run-time signal resolution and the intermediate format used will be explained in Section 3. The static thread distribution approach and the dynamic approach will be described in Section 4 and 5 respectively. Evaluation of the effectiveness of these two approaches will be presented in Section 6, and then finally concluded in Section 7.

## 1 An Esterel Example

The *ParallelData* example shown in Fig. 1, is a parallel data processing pipeline consisting of three threads, demarcated by the || operator. These threads communicate via the local signals S and S2. The first thread begins by waiting for the Start signal. Once received, the program starts to process the data by calling the processData1 procedure with result passed to the procedure by reference (the arguments in the first pair of parentheses are passed by reference while the second pair pass by value). The output of the procedure is then stored in result and sent using signal S to the second thread for further processing. The second thread waits for S using the await statement. Note that the data sent from the first thread is buffered and retrieved in the next *tick* using the pre keyword. This results in a software pipeline: while the second thread works on the data received from the first, the first thread continues to produce new data in parallel. As soon as the second thread completes its processing, the final result is sent to the third thread using the signal S2. If the CheckStatus input is activated, the body of the every statement in the third thread will start to execute. It takes the data from the second thread, does a self-diagnostic test with the given data, and then indicates whether the process is working normally. The program can be stopped at any time by activating the Stop signal.

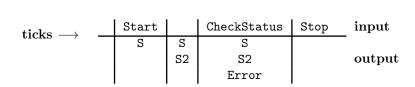

Fig. 2 shows a timeline of an example execution trace given a set of inputs. Tick boundaries are represented as the vertical lines and time progress along the horizontal line towards the right hand side. No inputs were given in the first *tick* as ParallelData does not react to any input in the first *tick*. In the second *tick*, Start becomes present and detected by the await Start statement on line 11. The first thread enters the loop, calls processData1, emits S and finally stops at the pause statement on line 15. The second thread does not react to S as it reacts to the *previous* status of the S, which was absent in the first *tick*. The third thread remains awaiting for CheckStatus on line 24.

From the third *tick* onwards, processData2's buffer is filled with data produced by processData1 in the first thread in the previous tick. As S became present in the second tick, the await pre(S) statement detects the presence of S, calls processData2 with the data embedded in S and finally emits S2. Both S and S2 are emitted in the third *tick*.

On the forth tick, CheckStatus becomes present. The first two threads continue to process the data and emit S and S2. The third thread detects CheckStatus and calls selfDiagnose on the data embedded in S2 on line 25. The selfDiagnose host function detects an error in the data, returns false and finally emits Error on line 28.

On the fifth tick, Stop becomes present. The Stop *conditional* node detects the signal and takes the present branch. Finally, the program terminates in this *tick*.

```

1 module ParallelData:

2 input Start, CheckStatus, Stop;

3 output Good, Error;

4 type Data;

5 procedure processData1(Data)();

6 procedure processData2(Data)(Data);

7 function selfDiagnose(Data) : boolean;

8 abort

signal S : Data, S2 : Data in

9

var result : Data, final : Data in

10

await Start;

11

loop

12

call processData1(result)();

13

emit S(result);

14

pause;

15

end loop

16

\mathbf{17}

18

loop

19

await pre(S);

call processData2(final)(pre(?S));

\mathbf{20}

emit S2(final);

\mathbf{21}

end loop

22

23

every CheckStatus do

24

if selfDiagnose(?S2) then

\mathbf{25}

emit Good;

26

\mathbf{27}

else

emit Error;

28

29

end if

30

end every

end var

\mathbf{31}

end signal

\mathbf{32}

33 when Stop

34 end module

```

Figure 1: The ParallelData example written in Esterel

Figure 2: A reaction timeline of the ParallelData example

# 2 The run-time signal resolution approach

Static scheduling techniques [8, 14, 10] rely on analyzing the dependencies between threads at compile-time. Attempting to parallelize a statically scheduled Esterel program would yield little performance gain due to the *sequentialization*. Enforcing a strong execution order would defeat any performance gain through parallel execution. To maximize the number of threads that can execute in parallel, a scheduling technique must satisfy the following:

- The ability to execute as many threads as possible, only enforcing an execution order at the points of communication.

- Threads are able to freely execute in any arbitrary order at any other time. This would allow load distribution be decoupled into an independent problem.

Given the requirements above, one can quickly arrive at the conclusion that, a key to effective parallelization lies in the ability to resolve signal dependencies at run-time, instead of having threads statically sequentialized.

The run-time signal resolution approach works on the principle that a signal is not read until its status is known. If the status of the signal is still unknown when a thread attempts to read a signal, the scheduler freezes the thread and picks another thread to start execution. Using this approach, the threads can be executed in any arbitrary order, and an execution order is only enforced at the points of communication.

A signal is *resolved* when it is emitted or its emission is ruled out. Detecting the presence of a signal is straightforward; it takes only one emission of the signal to confirm the status. Unlike detecting for presence of a signal, detecting the absence of a signal requires concerted effort from all threads who may potentially emit to the same signal. These threads, called potential emitters, must collectively agree on the absence of the signal in order to resolve the signal as absent. To schedule threads at run-time, a thread must be suspended when a signal being accessed is still unresolved. While the thread is suspended, its potential emitters have a window of opportunity to execute. As each potential emitter execute, it may removes itself as a potential emitter when the emission of the signal has been ruled out. If the unresolved signal is not emitted while the potential emitters execute, the number of potential emitters will eventually reduce to zero and the signal can be eventually concluded as absent.

With the run-time signal resolution mechanism, the order threads execute become irrelevant. The scheduler only has to ensure that any suspended thread is eventually rescheduled by executing each thread in a round-robin fashion. A high-level representation of such cyclic executive is presented in Fig. 3. The scheduler itself forms the skeleton of *reactive function*. It is called once every *tick*, and returns the termination status of the *tick*.

The reactive function, on line 4, starts by initializing the number of potential emitters for each signal. The number of potential emitters of a signal can be calculated by counting the number of threads that can potentially emit to the signal. Then the root thread of the program is added to a set of threads T as the candidates to be scheduled. The cyclic executive on line 8 is used to continuously schedule a threads until T becomes empty. Within the cyclic executive, the first thread t is selected and removed from T for execution. A thread t is a sequential composition of Esterel statements represented as a function t(). It would return to the cyclic executive for one of the following reasons:

- t has reached a tick boundary.

- t has terminated normally, by exception or preemption.

- t has been blocked due to an unresolved signal.

1  $\,T$  denotes a vector of active threads as candidates to be scheduled

$\mathbf{2}$  t denotes a sequential composition of Esterel statements represented as a function

3 function reactive\_function

```

foreach signal s shared by threads in T do

4

n_s := the number of potential emitters of s

5

6

end

7

add the root thread to T

while T \neq \phi do

8

select and remove the first thread t \in T

9

10

term \ code := t()

if term code = \infty then

11

add t to the back of T

12

end

\mathbf{13}

14

end

15

return term code

16 end

```

Figure 3: The high-level representation of the cyclic executive for run-time signal resolution

The termination status represented by  $term\_code$  indicates the reason for t's return. Threads in T are removed as they are selected for execution. However, t may be added back to T if it has been blocked due to an unresolved signal. Then, t has to be rescheduled by pushing t to the back of T. Eventually, when all threads are removed from T, the *reactive function* completes a *tick* by returning the termination code of the last executed thread. Due to reasons that will be explained later, the last executed thread will always be the root thread. A thread t interacts with the cyclic executive in Fig. 3 in four kinds of ways during execution:

- Forks into more threads saves itself in a buffer f, then add all child threads of the fork to T. To ensure all child threads terminate synchronously, each child thread has to check the the number of remaining child threads that are alive before it terminates. The last child thread to terminate is responsible to resume and reschedule its parent thread by adding f to T.

- Attempts to read a signal returns  $\infty$  if the attempt to read failed due to unresolved signal due to  $n_s \neq 0$  (some potential emitters may still emit). Otherwise, the thread proceeds to read the signal and continue execution normally.

- **Emits a signal** emits the signal s and reset the number of potential emitters by  $n_s := 0$ . Note that  $n_s$  is initialized by the cyclic executive on line 4 in Fig. 3.

- Rules out emission of a signal removes itself as a potential emitter by decrementing  $n_s := n_s 1$ .

The hierarchical structure of threads are preserved by the first kind of behaviour described above. During the execution of t, if it forks into more threads, the address of the parent t is saved to f prior to suspending it and adding its child threads to T. Suspension of the parent is done implicitly by not adding it to T until all its child threads complete. The last child thread to terminate will resume its parent thread by adding f to T.

For example, the following sketch Esterel program

RR n° 8056

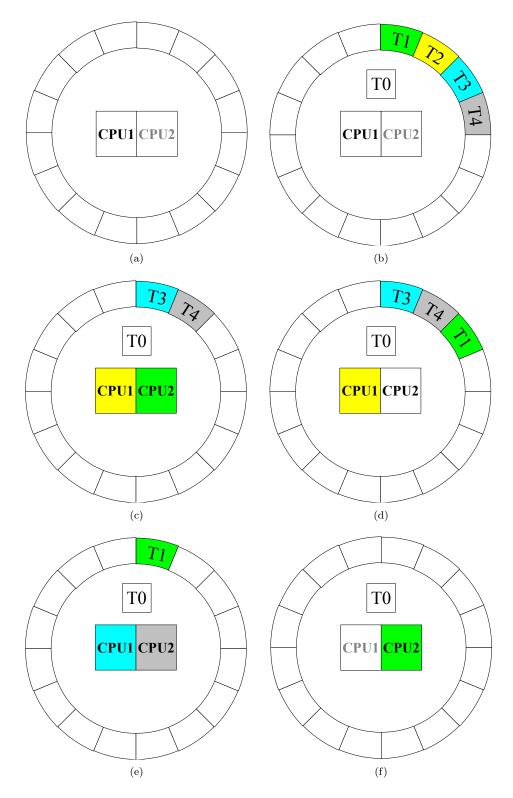

1 [ 2 T3 3 || 4 T4 5 ] 6 || 7 T2

consists of five threads represented by T0 (root thread), T1 (parent of two threads), T2, T3 and T4. As T0 and T1 are implicit in this example, they do not appear in the code. T0, being the root thread, is added to the vector T first by the cyclic executive in Fig. 3, i.e.,  $T = \{T0\}$ . Initially, T0 is the only thread in T. Then, T0 is selected and removed from T for execution. T becomes empty momentarily before T0 spawns T1 and T2 by adding these two thread to T and suspends T0 by adding it to a buffer F, i.e.,  $T = \{T1, T2\}$  and  $F = \{T0\}$ . When T1 is removed from T for execution, T1 immediately spawns T3 and T4 followed by adding itself to F, i.e.,  $T = \{T2, T3, T4\}$  and  $F = \{T0, T1\}$ . Assuming T2 terminates normally, T0, T1, T3 and T4 remain alive with T0 and T1 being suspended, i.e.,  $T = \{T3, T4\}$  and  $F = \{T0, T1\}$ . When T3 and T4 terminate in their respective order, T4 removes T1 from F and adds T0 to T in order to resume its parent thread, i.e.,  $T = \{T1\}$  and  $F = \{T0\}$ . Then, when T1 executes, as the last child thread of T0 to terminate, it resumes T0 by removing T0 from F and adds it to T, i.e.,  $T = \{T0\}$  and  $F = \phi$ . Finally, T0 terminates immediately when resumed, the cyclic executive terminates as the loop condition  $T \neq \phi$  on line 8 in Fig. 3 no longer holds.

The suspension and resumption of forked parent threads implement the normal synchronous termination of threads. This ensures that the parent threads will always terminate after their child threads. Subsequently, the last thread to execute in the cyclic executive will always be the root thread.

The run-time signal resolution approach is correct, so long as the Esterel program is known a priori to be causal. The definition of a causal program and the formalization of this statement is given in Definition 1 and Lemma 1 respectively.

**Definition 1.** A program without any instantaneous cyclic dependencies in its control-flow is defined as causal [5]. This implies that the statuses of all signals in a causal program can be constructively derived from the facts established about other signals without having to make any assumptions regarding their statuses.

**Lemma 1.** Let C be a causal Esterel program. Further, let T be the set of parallel threads in C, and S be the set of signals shared (emitted and tested) between two or more threads in T. The cyclic executive will resolve at least one signal in S in each iteration.

*Proof.* The proof for Lemma 1 proceeds by first presenting a number of axioms regarding the scheduling algorithm described earlier:

Axiom 1. The scheduling algorithm schedules threads in T in a round-robin fashion within a cyclic executive in each tick. Since C is causal, there will not be any dependency cycles between threads that would cause the program to deadlock. This implies that all threads will eventually get scheduled.

**Axiom 2.** At the start of each scheduling cycle corresponding to a new tick, all signals in S that are potentially tested are prevented from doing so until the statuses of the signals have been conclusively determined. This ensures that signals can never be tested prematurely. Signals can never be tested before they are emitted or before all their potential emitters have been ruled out, irrespective of the order that threads get scheduled.

**Axiom 3.** Each scheduled thread completes by returning a termination code. Threads that are blocked due to an unresolved signal will return a termination code of  $\infty$ , or a finite positive integer otherwise. Threads that return a termination code of  $\infty$  will be rescheduled in the next iteration of the cyclic executive.

Based on these axioms, the proof can now be done by induction. Since C is causal, the execution of threads in T will result in at least one of the following outcomes during a *tick*:

- 1. At least one shared signal is resolved to be present due to its emission, or absent when all its potential emitters collectively agree that the signal can no longer be emitted in that *tick*. In either case, |S| will decrement by the number of resolved signals.

- 2. The thread gets blocked from reading a signal due to that signal being unresolved. That thread will be rescheduled in the next iteration of the cyclic executive. |S| remains unchanged in this case.

- 3. The thread gets removed from T because it neither emits nor tests a signal in S. Consequently, |S| remains unchanged.

#### Base case

Consider the case where  $S = \{s_1\}$  is shared among a set of threads,  $T = \{t_0, t_1, \ldots, t_M\}$ . There are two possible scenarios:

- If  $t_i \ (i \in \{0, 1, \dots, M\})$  only tests but does not emit  $s_1, |S|$  remains the same (Outcome 2).

- If  $t_i$  is a potential emitter of  $s_1$ , then by Axiom 2, there are two possibilities:

- 1. Signal  $s_1$  is emitted.

- 2. Thread  $t_i$  rules itself out as a potential emitter of  $s_1$ .

If  $s_1$  gets emitted, all signals are resolved and |S| becomes zero. Otherwise, each  $t_i$  will rule itself out as a potential emitter, as the cyclic executive schedules them consequtively within the first iteration. Hence, after one iteration,  $s_1$  will either be emitted, or have all its potential emitters ruled out. Therefore, the number of unresolved signals will decrease to zero after at most one iteration of the cyclic executive.

#### Hypothesis

Assume that Lemma 1 holds for the case where  $S = \{s_1, s_2, \ldots, s_j\}$ .

#### Inductive step

Now, consider the case where  $S = \{s_1, s_2, \ldots, s_j, s_{j+1}\}$  is shared among a set of threads, T. After j iterations of the cyclic executive, at least j signals would have been resolved, leaving at most one unresolved signal, say,  $s_u$ . Then, in the (j + 1)th iteration of the cyclic executive, the execution of thread  $t_i$  will again result in one of two scenarios as before:

- Thread  $t_i$  gets blocked while attempting to read  $s_u$  (Outcome 2).

- Thread  $t_i$ , by Axiom 2, either:

- 1. emits  $s_u$ ; or

- 2. rules itself out as a potential emitter of  $s_u$ .

If  $s_u$  gets emitted, all signals are resolved and |S| becomes zero. Otherwise, each  $t_i$  will rule itself out as a potential emitter.

At the end of the (j+1)th iteration,  $s_u$  will either be emitted, or have all its potential emitters ruled out. It cannot happen that  $s_u$  is still unresolved, since the statuses of all other signals in S are already known. The first scenario can only perpetuate after the (j + 1)th iteration if the test of  $s_u$  itself determines its resolution (a contradiction of the causal assumption). Therefore, the cyclic executive will always resolve at least one signal in S in each iteration.

**Theorem 1.** For any execution order of all threads  $t_i \in T$   $(i \in \mathbb{N})$  in each tick, the number of signals in S that are unresolved will decrease monotonically, and eventually converge to zero after at most |S| iterations of the cyclic executive used for dynamic scheduling.

Lemma 1 can now be used to prove Theorem 1.

*Proof.* This will again be done by induction.

#### Base case

For the case where T consists of only one thread, there is no need for any signal resolution. Hence, we begin with the base case, where  $T = \{t_0, t_1\}$ .

- If the execution of either  $t_0$  or  $t_1$  results in Outcome 3 at any time, the proof is degenerate, as it implies that |S| has either become zero, or the remaining thread in T will decrement |S| to zero without getting blocked any further.

- Otherwise, assume  $S = \{s_1, s_2, \ldots, s_N\}$ . Then, based on Lemma 1,  $t_0$  and  $t_1$  will either resolve one or more signals in S (Outcome 1) before getting blocked, or will get blocked without resolving any signal (Outcome 2) in each iteration of the cyclic executive. However, both threads will not get blocked in the same iteration without resolving any signal, since C is causal. In this case, |S| will decrement by an integer value between [1, N] in each iteration. Therefore, the number of unresolved signals will decrease monotonically and eventually converge to zero after at most |S| iterations of the cyclic executive.

#### Hypothesis

Assume that the theorem holds for the case where  $T = \{t_0, t_1, \ldots, t_k\}$ , with the number of iterations required to reduce |S| to zero being less or equal to N.

#### Inductive step

Then, consider the case where  $T = \{t_0, t_1, \ldots, t_k, t_{k+1}\}$ :

- If the execution of  $t_{k+1}$  immediately results in Outcome 3, the number of iterations of the cyclic executive required to resolve all signals in S will still be the same as in the case where  $T = \{t_0, t_1, \ldots, t_k\}$ , since  $t_{k+1}$  does not affect any signal in S.

- Otherwise, two scenarios are possible:

- 1.  $t_{k+1}$  only tests for signals in S, and is not a potential emitter of any signal in S. As before, since  $t_{k+1}$  does not affect any signal in S, the number of iterations of the cyclic executive required to resolve all signals in S will still be the same, as in the case where  $T = \{t_0, t_1, \ldots, t_k\}$ . In particular, if all signals in S can be resolved within N iterations for the set of threads  $\{t_0, t_1, \ldots, t_k\}$ , they will also be resolved within N iterations for the set  $\{t_0, t_1, \ldots, t_k, t_{k+1}\}$ .

2.  $t_{k+1}$  is a potential emitter of one or more signals in S. The addition of more potential emitters for a given signal can only result in that signal being potentially resolved in fewer iterations, but never more. Consequently, if at most N iterations were originally required to reduce |S| to zero when  $T = \{t_0, t_1, \ldots, t_k\}$ , the inclusion of  $t_{k+1}$  to T will also only at most require N iterations.

Since both the base and inductive cases have been proven, Theorem 1 will hold for any causal Esterel program with two or more threads.  $\hfill \Box$

Due to theorem 1 and Axiom 2, the semantics of instantaneous broadcast is preserved. The resulting behaviour of a dynamically scheduled program would be completely the same as a statically scheduled program. In the following section, the actual implementation of the run-time signal resolution algorithm will be described.

# 3 Implementation of run-time signal resolution

Implementing the run-time signal resolution algorithm involves two stages of the compilation process. One stage is during the construction of the intermediate format, and the second is the code generation stage. This section will proceed by describing the GRC intermediate format [14] in the next subsection.

#### 3.1 The GRC intermediate format

The graph code (GRC) format represents an Esterel program with an acyclic directed graph. It consists of two parts: (1) a hierarchical state graph (HSG), and (2) a concurrent control-flow graph (CCFG). As the discussions of the compilation techniques in this paper do not involve the HSG, from here on, the term GRC will always be referred to the CCFG part of the representation.

The construction process of GRC introduces a unique distinction between the initial behaviour and the resumption behaviour of each Esterel statement, called the *surface* and *depth* behaviour respectively. We elaborate these terms with the following:

- The *surface* behaviour describes the micro-steps performed in the first *tick* of any composition of Esterel statements.

- The *depth* behaviour describes the micro-steps performed in the subsequent *ticks* of any composition of Esterel statements.

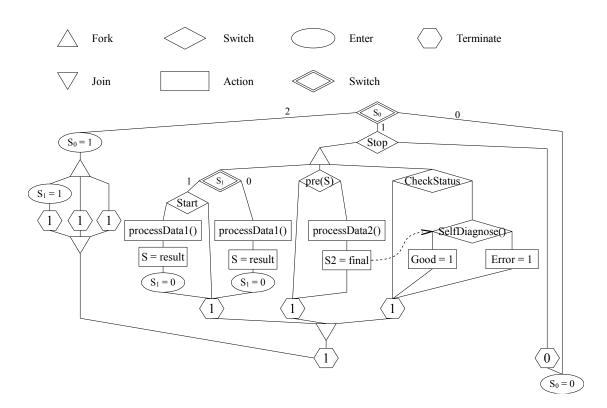

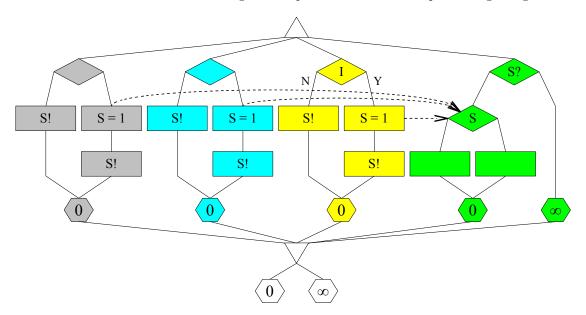

We will first describe the types of GRC nodes that exist in GRC followed by its control-flow. A list of GRC nodes is illustrated along the top of Fig. 4. These nodes are described as the following:

Fork and Join: Create and destroy threads respectively.

**Test:** The graphical representation of the **present** or the **if** statement.

Action: Performs an action such as variable assignment, emitting a signal and calling a procedure.

Switch: Encodes the state of a thread. Each branch under this node represents a tick.

Enter: Sets the state encoded in a *switch* node of a thread.

RR n° 8056

Figure 4: The ParallelData example represented in the Graph Code Format

**Terminate:** This node, introduced in [10], is a variant of the *sync* node introduced in [14]. A *terminate* node encodes the completion status of a thread. A completion code of zero denotes a normal termination; a value of one indicates the thread has been paused for a *tick*; and a value greater than one indicates the thread has been terminated by an exception or preemption. This clever encoding scheme (courtesy of Berry [4]) succinctly captures the *meet at the rendezvous* behaviour of concurrent statements and the *winner-take-all* behaviour of simultaneously thrown exceptions and preemption. Within a pair of *fork* and *join* nodes, *terminate* nodes immediately precede the *join* node and dictate the continuation context the *join* node must take when threads terminate. This is the primary mechanism for compilation of nested exception and preemption. The hierarchical nesting of the exception and preemption constructs determine the priorities of their reactions when triggered simultaneously. The higher the priority the larger the value a *terminate* node returns. The highest value will take precedence when *terminate* nodes merge at a *join* node.

Nodes in GRC are connected by *control arcs* (solid lines) and *data dependency arcs* (dashed line) to describe the control-flow and communication between nodes respectively. A GRC graph is traversed from top to bottom once every *tick*. There are no loops in GRC as the repetition is achieved by controlling of the states of the program in the subsequent *tick* using *switch* and *enter* nodes. *Switch* nodes are later translated into state variables that are assigned by *enter* nodes.

As an example, the GRC shown in Fig. 4 represents the ParallelData Esterel module. We will assume the same input trace as Fig. 2 to describe the control-flow. The program starts from

the *switch* node at the top. The nodes residing on the left branch of the top *switch* node define the *surface* behaviour of the program. The program immediately pauses for one *tick* due to the await statements. Two *enter* nodes are inserted to setup the states of the subsequent *tick* by assigning  $S_0 = 1$  and  $S_1 = 1$ .

In the second *tick*, the top *switch* node reads the value of  $S_0$  and selects the middle branch. Start is now present and the program follows the present branch of the *test* Start node.  $S_1$  is set to 0 to ensure that Start will no longer be tested in the subsequent *ticks*. Then, S is emitted before the first *tick* ends.

From the third *tick* onwards, processData2's buffer, implicitly created by the pre operator, is filled with data produced by processData1 in the first thread in the previous tick. The pre(S2) *test* node in the second thread detects the presence of S and selects the present branch. Then, S2 is emitted before the third *tick* ends. Both the first and the second thread now repeat these execution paths indefinitely unless stopped by the Stop signal.

On the forth tick, CheckStatus becomes present. The first two threads continue to process the data and emit S and S2. The third thread detects CheckStatus, follows the present branch, then calls selfDiagnose. The procedure takes the data emitted via S2 by the second thread and analyzes the data and discovers an anomaly. The thread takes the else branch of the selfDiagnose *conditional* node and emits Error.

On the fifth tick, Stop becomes present, which preempts the program due to the abort-when Stop statements. The program follows the present branch and exits the program via the *enter* node at the bottom. This *enter* sets  $S_0 = 0$  and forces the program to forever take the right branch of the top *switch* node in the subsequent *ticks*. This effectively terminates the program as the program will no longer react unless reset.

#### 3.1.1 Extensions to GRC

To schedule Esterel threads, an Esterel program is represented in a variant of GRC [14]. GRC features a unique way of determining execution path using termination codes from each statement in Esterel. The run-time signal resolution approach elegantly piggy-backs on this special encoding scheme of the termination codes by partially capture scheduling information within the intermediate format. GRC represent synchronous termination of threads by encoding the termination code of each thread in *termination* nodes at the end of each thread. The *termination* nodes provide a mechanism for the program to react differently based on the values stored within the *termination* nodes. The termination mechanism in GRC is augmented with an additional termination code for resolving signals at run-time. Hence, the use of GRC would minimizes the effort required to implement a mechanism for resolving signals at run-time and does not require inserting control logic into the graph for run-time signal resolution.

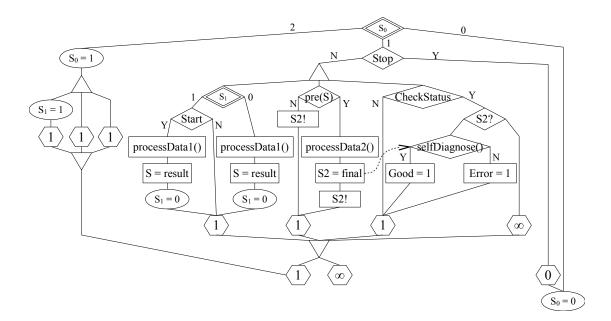

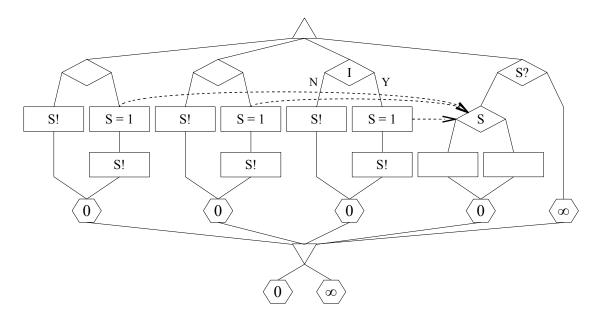

To support resolving signals at run-time, the GRC format has been augmented with two additional nodes. We will illustrate the two additional nodes using the the ParallelData example presented in Fig. 1 and its corresponding representation in GRC augmented with run-time signal resolution nodes is presented in Fig.5.

The program starts by testing  $S_0$ , which is initially set to 2, using the *switch* node at the top of the graph. The *switch* node determines the current state of the program. Here, branch 2 of  $S_0$  represents the initial state of the program. A guard (S2?) node is inserted in places where a signal must be protected from being read prematurely. A *resolution* (S!) node is inserted at suitable points to remove a thread from the set of potential emitters for S2. For this example, a guard node has been inserted immediately before the *test* node of selfDiagnose(?S2), while *resolution* nodes have been inserted immediately after the *emit* (S2 = final) node, and on all paths that would not lead to S being emitted. The *resolution* nodes inserted immediately below

Figure 5: The ParallelData example represented in the Graph Code Format

signal emissions *immediately declares the signal as present*. However, other *resolution* nodes *removes the thread from the set of potential emitters*.

Synchronizing threads to *tick* boundaries is achieved explicitly in GRC as part of the controlflow by forking and joining threads at the start and the end of of each *tick* respectively. This behaviour is exemplified by the *fork-join* pair in each *tick* when concurrent statements execute in Fig. 5. In the **ParallelData** example, both the initial *tick* (the left branch under the top *switch* node) and the subsequent *ticks* (the middle branch under the top *switch* node) start by forking into two threads and joining them at the bottom of the GRC graph. This explicit *tick* synchronization mechanism at the intermediate representation level saves the cyclic executive in Fig. 3 from having to handle *tick* synchronization. The cyclic executive requires only the value of the termination code when the program reaches the bottom of the GRC graph to determine whether a *tick* has elapsed based on the following:

- A value of ∞ indicates some threads are still alive but blocked due to unresolved signals. These threads must be scheduled for execution in the next iteration of the cyclic executive.

- A value of zero indicates the program has terminated normally.

- A value of one indicates the program has reached a *tick* boundary. During a *tick*, the internal states (represented by the *switch* nodes) of the threads in the program are assigned for resumption in the subsequent *tick*. At the end of a *tick*, the *reactive function* returns to its caller. Calling the *reactive function* again starts a new *tick* and the previously paused threads will resume from the states assigned by the previous *tick*.

Implementing run-time signal resolution at the GRC representation level requires inserting *guard* nodes and *resolution* nodes at appropriate places. While inserting *guard* nodes is simple, inserting *resolution* nodes is more involved. A *guard* node is inserted before a *test* node whenever the *test* node reads a signal that is potentially emitted from at least one other thread. In contrast, inserting *resolution* nodes involves an algorithm that will be described in the next subsection.

#### 3.2 The insertion algorithm for signal resolution nodes

During the compilation process, the compiler inserts a guard node before a test node to prevent the signal from being tested prematurely, i.e., when the signal status is yet unresolved. To get past a guard node, the status of the signal must be resolved. It takes only one potential emitter that emits the signal in order to confirm the presence of the signal. However, determining absence of a signal requires confirmation from all potential emitters. To further complicate the matter, threads often communicate back and forth. Such threads cannot wait till the tick boundary to determine status of the shared signals if those signals are guarded. Those threads would deadlock due to indefinitely waiting for each other to resolve the statuses of the signals. For this reason, the compiler must insert resolution nodes for each potential emitter to ensure they keep the signal readers informed about the status of the shared signal.

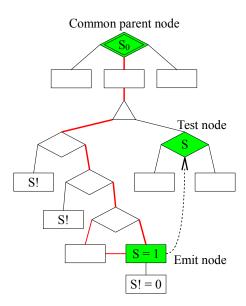

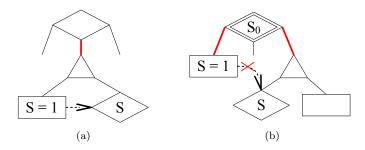

To insert resolution nodes, the insertion algorithm has to find the closest common parent node. A common parent is a conditional node under which the signal producer and consumer are attached. The highlighted switch node at the top of Fig. 6 is an example of a common parent of the emit S (i.e., S = 1) node and the test node for S. The highlighted node at the bottom is the signal producer, and the highlighted node in the middle is the consumer. The producer and the consumer execute concurrently under the common parent node as they are in two different branches of the fork node. Hence, a dependency exists in the example in Fig. 6 that needs to have guarded access to the shared signal.

Figure 6: Illustration of places to insert *resolution* nodes

Finding the *common parent* node is only the first step to insert *resolution* nodes. Not all paths from the *common parent* node would lead to the *emit* node. As soon as the potential emitter deviates from the paths to the *emit* node, it must go through a *resolution* node. For example, the paths to the *emit* node are highlighted in red in Fig. 6. From the *common parent* onward, any path deviating from the path in red needs to have a *resolution* node inserted. The intuition is to find all the *conditional* nodes on the path from the *emit* node to the *common parent* node, and then insert *resolution* nodes under the branches of those *conditional* nodes except the branch that leads to the *emit* node. This is the basis for the insertion algorithm in

Fig. 7.

```

1 Let C denote a set of nodes in a causal program

procedure insert_resolution_nodes

2

foreach node t \in C do

3

if t is a test node then

4

foreach data predecessor e of t do

\mathbf{5}

insert_nodes(t,e)

6

7

end

end

8

end

9

10 end

procedure insert_nodes(t,e)

1

insert a resolution node under e

2

3

P := \mathtt{path\_to\_node}(e)

4

Q := \mathtt{path\_to\_node}(t)

c := \texttt{common_parent_node}(P,Q)

5

6

n := e

foreach conditional node p \in P do

7

8

if p = c then return

9

mark_path_to_node(n, p, e)

n := p

10

for

each branch b under p do

11

if b is not on the path to e and

12

a resolution node r for e has not been

inserted under b then

insert r at the top of b

13

end

14

end

15

end

16

17 end

```

Figure 7: Algorithm for inserting signal resolution nodes

This algorithm starts with insert\_resolution\_node in Fig. 7. The auxiliary functions used by insert\_nodes are presented separately in Fig. 8. the algorithm is initiated with the insert\_resolution\_nodes procedure. On line 3, the algorithm traverses through the GRC of a program searching for *test* nodes. On line 5, the procedure follows each *data predecessor* e of the *test* node t and passes both t and e to the insert\_nodes procedure. The term *data predecessor* refers to those nodes that have data dependency arcs leading to other nodes.

Within insert\_nodes, it immediately inserts a resolution node under the e. The resolution (i.e., S! = 0) node inserted under e propagates the presence of the signal, allowing the signal to be consumed. An example of this node is the node labeled with S! attached immediately below the highlighted *emit* node in Fig. 6. The path\_to\_node function on Lines 3 and 4 create two vectors of nodes on the paths to the *emit* node (the P vector) and the *test* node (the Q vector) respectively. The common\_parent\_node function on line 5 finds the closest *common parent* node of the *emit* node and the *test* node by comparing P and Q. Once the *common parent* node is found, common\_parent\_node returns to the insert\_nodes procedure. Line 6 and the loop on line 7 start searching from the *emit* node towards the *common parent* node to find additional

```

1 P denotes a vector of conditional nodes on the path to a node from the root node

2 function path_to_node(e)

n := e

3

while control predecessors of n > 0 do

4

n := the first control predecessor of n

5

if n is not a fork node then

6

add n to P

7

end

8

end

9

return P

\mathbf{10}

11 end

1 function common_parent_node(P,Q)

foreach p \in P do

\mathbf{2}

for

each q \in Q do

3

4

if p = q then return p

\mathbf{end}

\mathbf{5}

6

\mathbf{end}

7 end

1 function mark_path_to_node(n,c,e)

if n = c then return true

\mathbf{2}

for

each control predecessor p of n do

3

if mark_path_to_node(p,c,e) then

4

5

mark the branch under c that n belongs to as a path to e

end

6

\mathbf{end}

7

8

return false

9 end

```

Figure 8: Auxiliary functions for the insertion algorithm

places to insert resolution (i.e., S!) nodes. Line 8 checks whether the common parent node has been reached. The procedure then returns to insert\_resolution\_nodes and move on to the next data predecessor; otherwise, the search continues. The mark\_path\_to\_node function on line 9, presented in Fig. 8, recursively traverses each path of the given node 'n' upward. It stops traversing as soon as the target node c is reached, and marks the branch under c that n belongs to as a path that will eventually reach e. The insert\_nodes procedure calls mark\_path\_to\_node on a segment of the path between the common parent node and the emit node at a time, starting from the emit node to the nearest conditional node in vector P. The segment being searched is changed by line 10 in Fig. 7. The segments between c and e that are marked by mark\_path\_to\_node are illustrated with the paths highlighted in red in Fig. 6. Lines 11 ~15 then insert resolution nodes under each conditional node for each branch that deviates from the path to the emit node.

Running through the insertion algorithm on the example in Fig. 6 would result in *resolution* node being added under each brach of each *conditional* node on the path between the *common* parent node and the *emit* node. The algorithm would correctly identify the path marked in red, and avoid inserting *resolution* nodes on this path. However, the insertion algorithm assumes that all dependencies are valid. It would not work if the dependency is false. An example of both a valid and a false dependency is illustrated in Fig. 9.

Figure 9: An example of (a) a valid and (b) false dependency

Fig. 9(b) shows an example of false dependency. In this example, the *emit* and the *test* nodes are located in different *ticks* as they are located on different branches of the *switch* node. The signal is emitted and tested in different *ticks*. Due to the compiler plainly inserting dependency between nodes by tracing the data successors or predecessors of a node, some of the matched dependencies are not real dependencies. This will create problems for dynamic signal resolution in two ways: (1) it creates extra scheduling overhead, or worse, (2) potentially produce incorrect behaviours due to attempts to resolve signals due to false dependencies. Hence, the algorithm in Fig. 10 is applied prior to the insertion algorithm to remove any false dependencies.

Determining whether a dependency is valid is very simple. The algorithm would only need to find the closest *common parent* of the *emit-test* node pair that are linked by a data dependency arc. Then, it determines whether the paths to each of the node of the pair reside on the same branch under the *common parent* node. If the pair reside on the same branch like the highlighted branch in the example in Fig. 9(a), the dependency is valid. If the dependency is invalid, the pair of nodes would reside on different branches of the *common parent* node, as illustrated in Fig. 9(b). This is precisely what the algorithm in Fig. 10 does.

The algorithm for removing false dependencies starts by looking for *emit* nodes that has at least one data successor. It then finds the closest *common parent* node on lines  $6\sim8$ . The branches that lead to the pair of nodes are compared to determine whether they reside on the

```

1 C denotes a set of nodes in a causal program

procedure remove_false_dependencies

2

foreach emit node e \in C do

3

4

if data successors of e > 0 then

foreach data successor t of e do

5

N := \mathtt{path\_to\_node}(e)

6

M := \mathtt{path\_to\_node}(t)

7

8

c := \text{common_parent_node}(N, M)

p := the branch under c that leads to e

9

q := the branch under c that leads to t

10

if e and t are in the same thread or p \neq q then

11

break the dependency between e and t

12

end

13

end

14

end

15

end

16

17 end

```

Figure 10: Algorithm for removing false dependencies

same branch on line 11. In addition to that condition, line 11 also checks if the pair of nodes reside in the same thread. If either of these conditions is true, the dependency between the nodes would be removed.

#### 3.3 Generating code with run-time signal resolution

The second stage of the implementation for run-time signal resolution takes place during code generation. We will first describe the implementation for sequential execution before we extend this scheduling scheme for parallel execution in Section 4 and 5.

To avoid complicating the discussion of the implementation with the full details of an actual generated code, we will illustrate a sketch of an Esterel program using the example in Fig. 11. The sketch example consists of four threads communicating via the local signal S. The thread at the top is the only reader of S while the other three are potential emitters to S. The GRC representation of this example is presented in Fig. 12 to reveal a little more detail of each thread. The GRC representation consists of a *fork* node spawning four threads. The left three branches of the *fork* node in Fig. 12 lead to the potential emitters of S while the consumer of S is located on the right most branch of the *fork* node. The *test* node in each potential emitter represents some condition that decides whether S is emitted. A resolution node has been inserted under each emit S node to inform the consumer about the presence of S. Additional *resolution* node has been inserted on the non-emitting side of the *test* nodes inside the potential emitters to decrement the number of potential emitters to S. These *resolution* nodes have completely covered all paths within their respective threads such that these threads would not be able to terminate without first hitting a resolution node. To protect against premature access to S, a quard has been inserted above the 'test S' node. Assuming the compiler unwisely schedules the consumer thread before the potential emitters, the signal would be unresolved when this thread reaches the *quard* node. It then takes the right branch of the *quard* node and reaches a *termination* node with a value of  $\infty$ . This special termination code *falls through* the *join* node when threads join at the *join* node and the program exits the graph with a value of  $\infty$ . Due to this, the cyclic executive

```

1 module sketch:

2 input I;

signal S in

3

% ...

4

present S then

5

% ...

6

end

7

8

present I then

9

10

emit S

11

end

12

\% potentially emit S ...

13

14

potentially emit S ...

15

16 end

17 end module

```

Figure 11: An sketch of an example Esterel program

detects the special termination code and reschedules the consumer thread in the next iteration.

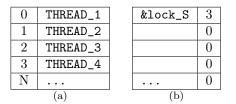

When the compiler generates code from the GRC representation, the *guard* nodes are translated into counting semaphores around the shared signals. Each unique shared signal in the program has an associated counting semaphore. The counting semaphores are initialized to the number of potential emitters of their corresponding signal at the beginning of each *tick*. The counting semaphores are decremented by the *resolution* nodes in the potential emitters. The *guard* nodes are used for blocking the program when it attempts to read a signal with a non-zero counting semaphore. This locking and unlocking mechanism is exemplified by the generated code of the **sketch** example in Fig. 13.

The generated code implements the **sketch** Esterel module in a *reactive function* called **esterel\_module**. The *reactive function* is called once every *tick*. The generated code presents the four threads of the **sketch** example as four functions. The actual implementation of the compiler would inline these functions into the *reactive function*. However, threads are shown as functions to aid the presentation of the program structure in the generated code.

The first thing the *reactive function* does is to initialize the program counters of the four threads. The program counters are used for resuming the threads when they are blocked by a signal guard. Following that, the signal guard is initialized by assigning the lock lock\_S with the number of potential emitters on line 3. The name of the lock suggests that it is used for protecting the signal S. The cyclic executive is implemented by the loop on lines  $5 \sim 11$ . On every iteration, the loop condition checks the termination code. The loop will continue as long as the value of the termination code equals infinity. Within the loop body, threads execute one after the other in a sequential order. The returned termination code from each thread is combined at the end of each iteration. The combination of termination codes implements the *join* node in Fig. 12, and a value of infinity from a thread would always overide the termination code from other threads. The combined value is then checked by the loop condition on line 11 to reschedule the *blocked* threads. The implementation of the cyclic executive bears some resemblance of its abstract form in Fig. 3 of Section 2. The difference is that the abstract algorithm removes a thread from the vector when a thread dies; whereas the implementation of the algorithm in Fig. 13 controls the threads via their program counters. In the implementation, a thread would not execute if its program counter is zero and it would immediately return to the cyclic executive

Figure 12: The GRC representation of the sketch example

in esterel\_module.

To illustrate how signal locking and unlocking is performed, consider the consumer thread that has been deliberately scheduled before the potential emitters. The actual implementation of the compiler attempts with its best effort to schedule potential emitters before their consumers. In Fig. 13, when thread\_1 executes, lock\_S has still not been released. This causes thread\_1 to store the program counter for resumption in the next iteration, and returns a value of infinity (lines 18~20). Returning to esterel\_module, the next thread thread\_2 gets scheduled. Depending on the status of the input signal I, S may or may not be emitted. If S is emitted, the code generated from the *resolution* node unlocks the *quard* node by setting the counting semaphore to zero. As soon as the signal guard is released, the dependency of the first thread is resolved. The first thread can then be freely rescheduled at any time within the *tick*. However, if the input signal I is absent, line 33 which corresponds to the *resolution* node on the else branch is executed and decrements the counting semaphore. With one potential emitter terminated and two remaining, the value of the counting semaphore drops to two and the signal guard stay locked. Assuming both thread\_3 and thread\_4 do not emit S, the counting semaphore is decremented twice by these two threads and becomes zero. When thread\_1 gets rescheduled on the second iteration of the cyclic executive, it resumes at the address pointed by its previous program counter. Then, it successfully get through the signal guard this time. Since the cyclic executive merely iterates through a static list of threads, threads that have already completed their *local ticks* are not removed from the list. For this reason, program counters are used to keep those threads at the completion state. Whenever a completed thread is rescheduled, it immediately returns.

#### 3.4 Preservation of the scheduling algorithm

In Section 2, a sketch scheduling algorithm using run-time signal resolution has been presented. The preservation of the algorithm in Fig.3 are achieved by the following implementation of the

```

1 int esterel_module() {

\label{eq:constraint} thread\_1\_pc \ = \ thread\_2\_pc \ = \ thread\_3\_pc \ thread\_4\_pc \ = \ 0;

2

lock_S = 3; // 3 potential emitters

3

4

// The fork node spawns four threads

do \hspace{0.1in} \{

5

6

term_1 = thread_1();

term_2 = thread_2();

term_3 = thread_3();

7

8

9

10

} while (term_0 = INIFINITY);

11

12 }

13 int thread_1() {

14 if (thread_1_pc)

15

goto *thread_1_pc;

16

. . .

17 RESUME:

if (lock_S) {

18

thread_1_pc = &&RESUME;

return INIFINITY;

19

20

} else {

21

22

Inside guarded body

23

}

return 0;

\mathbf{24}

25 }

26 int thread 2() {

if (thread_2_pc)

27

goto *thread_2_pc;

28

if (signal.I) {

29

30

signal.S = 1;

\mathbf{31}

lock\_S = 0;

32

} else

33

lock S --;

34 END:

35

thread 2 pc = \& END;

36

return 0;

37 }

38 int thread _3() {

if (thread_3_pc)

goto *thread_3_pc;

39

40

\mathbf{41}

. .

42

lock_S --;

43

// ...

44 END:

thread 3_pc = &&END;

return 0;

\mathbf{45}

\mathbf{46}

47 }

48 int thread_4() {

49 if (thread_4_pc)

goto *thread_4_pc;

50

51

. . .

\mathbf{52}

lock_S - -;

53

// ...

54 END:

thread 4 pc = \& END;

return 0;

55

56

57 }

```

Figure 13: The generated code of the sketch example with run-time signal resolution

axioms presented in Section 2:

- Axiom 1: The cyclic executive is implemented as a while-loop that encloses a set of threads ordered sequentially. Each thread is executed once in each iteration until the combined termination code from all threads result in a non-infinite value. If a thread does not communicate with any other thread, that thread will not interact with the signal locks in the generated code. When a thread terminates, the program counter remains at the end of the thread and would immediately return to the cyclic executive if rescheduled (lines 35, 45 and 55 in Fig. 13).

- Axiom 2 Premature access to a protected signal is prevented by marking a signal as present due to emission, or absent when all potential emitters collectively agree that the signal can no longer be emitted in that *tick*. The number of unresolved signals is decremented by 1. This behaviour is achieved by resetting or decrementing the counting semaphore in the generated code, every time this condition holds (lines 31, 33, 42 and 52 in Fig. 13).

- Axiom 3 A thread gets blocked from reading an unresolved signal is a candidate to be scheduled in the next iteration of the cyclic executive. In the generated code, the blocked thread saves its program counter and returns to the cyclic executive with a termination code of  $\infty$  (line 20 in Fig. 13). The cyclic executive detects the blocked thread and the threads within the cyclic executive are rescheduled.

Hence, guarding shared signals with counting semaphores is a precise implementation of the run-time signal resolution algorithm sketch presented in Fig. 2. Given a causal Esterel program, every thread will have the opportunity to progress over each iteration of the cyclic executive. As threads progress, the number of unresolved signals decrease monotonically. Eventually, the number of unresolved signals converge to zero.

The previous sections and this section have discussed the dynamic scheduling approach using run-time signal resolution, provided a proof of its correctness, and the associated implementation. While the dynamic scheduling approach allows Esterel threads to execute in any order for any number of times, the macro behaviour of the program remain the same as a statically scheduled Esterel program. This flexibility elegantly decouples scheduling from thread distribution for executing Esterel programs on a multi-core. Thus, thread distribution can be solved as an independent research topic. The next two sections propose a static and a dynamic approach to distribute Esterel programs.

## 4 Static load distribution

The static distribution approach is the an attempt in this research to study the feasibility of executing Esterel on a multi-core. Threads are statically grouped together based on the amount of computation within each thread approximated by a heuristic guided algorithm. Each group is distributed to a dedicated core and no thread will be migrated between cores at run-time. We will describe the partitioning algorithm in the next subsection, followed by the implementation for the partitioned programs in section 4.2.

#### 4.1 The static load distribution algorithm

The process of grouping threads together, called partitioning, takes place after the GRC of the program has been constructed. The GRC representation of the program is analyzed by a distribution heuristics to partition the nodes under the parallel branches of a *fork* node. When

the compiler generates the code from the GRC, each partition is enclosed in an cyclic executive such that threads within a partition is scheduled independently of other partitions. As each processor execute its assigned partition in parallel, they synchronize at the each *tick* boundary. However, the barrier synchronization of the partitions at *tick* boundaries imposes some rules over how threads should be partitioned:

- The atomicity of threads: A thread should not be divided to execute in multiple partitions. The whole thread should be allocated to one partition. Failing to follow this rule would incur performance penalties due to resolving control dependencies in addition to data dependencies.

- The hierarchic ordering of threads: If a program (p||q) is distributed to partitions P1 and P2 respectively, any child thread forking from p should not be allocated to P2, and vice versa for q. Failing to follow this rule would incur performance penalties due to synchronization for starting forks in addition to synchronous joins.

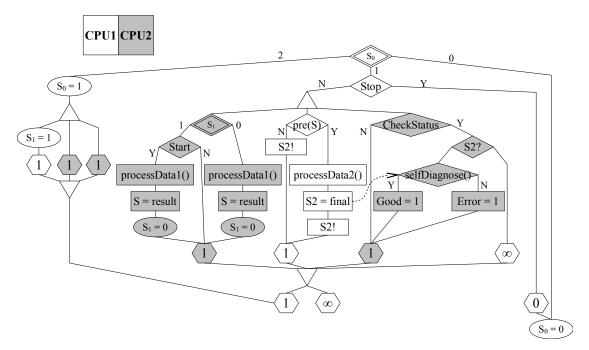

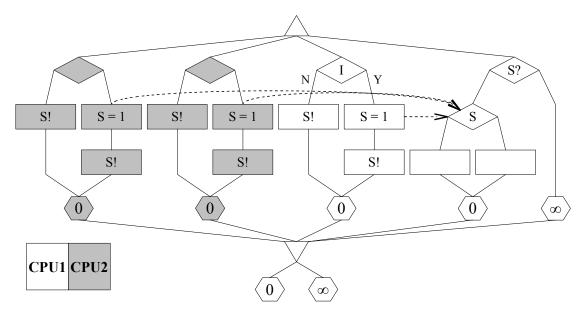

Based on these rules, the distribution algorithm only distributes the threads spawned by the top level *fork* nodes in the root thread. An example of a partitioned program is illustrated in Fig. 14. The GRC representation shows the ParallelData example partitioned to execute on two CPUs. When the program starts, the root thread executes on the first CPU. As soon as the program reaches a *fork* node, the nodes shaded in gray are spawned on the second CPU, while the non-shaded nodes are spawned on the first CPU.

Figure 14: The partitioned GRC of the ParallelData example

Base on the amount of code the compiler would generate for each type of node in GRC, a relative cost is assigned to each type of node. The cost of a node is approximated by the number of instructions required for that node and normalized against the node with the least cost. For example, an *emit* node would in general have the lowest cost. It require only an assignment operation in the generated code. Hence, an *emit* node would have a cost of one unit. For a *fork* node, an operation is required to initialize each thread it spawns. The cost of a *fork* is then approximately the number of threads it spawns. That is, for spawning four threads, the cost of a *host* procedure call is difficult to determine without exhaustive timing analysis. For nodes that call host procedures, the compiler makes an approximation of the cost by summing up the number of instructions of the host procedures. Other types of nodes have the same cost of one unit. Then, the partitioning algorithm computes the total cost of each thread by summing up the cost of each node within each thread under the top level *fork* node. Only top level *fork* nodes in the root thread are partitioned due to the rules described earlier.

After the cost of each node (represented by c in the algorithm presented in Fig. 15) in the GRC has been approximated, the partition\_dfs algorithm in Fig. 15 starts partitioning using a depth-first search through the GRC. The algorithm distinguishes only *fork* and *join* nodes from the other types of nodes. More specifically, the algorithm looks for the top level *fork* and *join* nodes in the root thread. Other types of nodes are treated as ordinary nodes and their cost is added to the total cost of the thread being traversed. The identification of the top level *fork* is done on line 10. If a top level *fork* node, r, is found, lines 11 and 17 keep track of r until the costs of all branches under r have been estimated. Any *fork* node nested under r will cause the condition on line 10 to fail and the nested *fork* nodes are treated as ordinary nodes.

When a top level *fork* node is found, the loop on line 12 starts traversing the threads under r on a branch-by-branch (thread-by-thread) basis and assigns the reference of the root *fork* node to r. In the  $r \neq 0$  state, the algorithm recursively traverses down each branch (thread) under r until it is stopped by the condition on line 8 when the corresponding *join* node of r has been reached. Before traversing through each thread under r, line 13 initialize a new cost c with zero for the thread about to be visited and adds c to C. Then, the algorithm recursively calls partition\_dfs on the first node of each thread. For each node partition\_dfs visits, the ordinary nodes would fail both conditions on line 8 and 10 and start from line 23. As C is not empty in the  $r \neq 0$  state, the cost  $c_{node}$  of each node is added to the total cost c of the current thread being traversed on line 24. Then, the algorithm continues to recursively call partition\_dfs on each control successor of *node* on line 26.

When all branches (threads) under r have been visited, the algorithm goes back to the r = 0 state on line 17 and cost is not calculated until the next top level *fork* node is reached. The reason cost is not calculated in the r = 0 state is due to the root thread being the only thread executing during this state. Then, the vector C, which represents the costs for each branch under r, is sorted in ascending order on line 18 before passing to the load\_balance procedure. The load\_balance procedure sorts the partitions based on their current associated costs. It then distributes each branch in C to the partition with the least cost in P. This is repeated until all branches in C have been distributed. Once load\_balance returns to partition\_dfs, C is cleared and remains empty until a *fork* node is encountered.

#### 4.2 Generating code from GRC

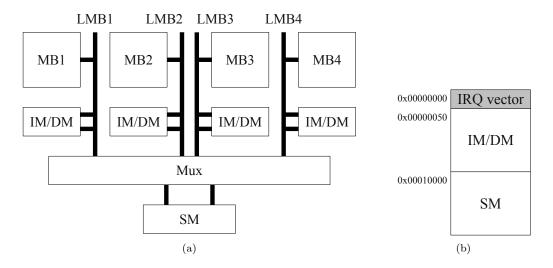

To execute the partitioned code in parallel, the code may be generated either as POSIX threads that require an OS to run, or as custom code for a dual-core Xilinx Microblaze platform that can run without an OS. The number of thread partitions that is generated will depend on the number of processor cores that the execution platform offers. These thread partitions are created only once throughout the lifetime of the program. Both the OS and non-OS implementations are based on the same principle that will be described next.

Generating code from GRC for execution in parallel is an incremental step from the imple-

```

1 r denotes the top level fork in the root thread

\mathbf{2} c denotes the cost of the current branch being traversed

3 c_n denotes the cost of the current node being visited

4 C denotes a vector of costs associated with each branch under a fork

5 procedure partition_dfs(node)

if node is visited then return

6

add node to the visited set

7

if node = the corresponding join of r and r \neq 0 then

8

return

9

else if node = fork and r = 0 then

10

r = node

11

for

each control successor s of node do

\mathbf{12}

13

c := 0

add c into C

14

partition_dfs(s)

15

\mathbf{16}

end

r := 0

17

sort C in ascending order

\mathbf{18}

load_balance(C)

19

empty C

\mathbf{20}

return

\mathbf{21}

22

end

if C \neq \emptyset then

23

c := c + c_{node}

\mathbf{24}

\mathbf{end}

\mathbf{25}

foreach control successor s of node do

26

partition_dfs(s)

\mathbf{27}

\mathbf{28}

\mathbf{end}

29 end

1 p denotes the total cost of the partition

\mathbf{2} P denotes a vector of total costs associated with each partition

3 procedure load_balance(C)

foreach branch cost c \in C do

4

sort P in ascending order

5

6

assign the branch corresponding to c to the first partition p \in P

p := p + c

7

\mathbf{end}

8

9 end

Figure 15: The distribution algorithm

```

mentation of a dynamically scheduled Esterel program, described in Section 3.3. We will use the same sketch<sup>1</sup> example presented in Fig. 11 to highlight the incremental changes. In 16, the sketch example has been divided into two partitions to executes on two processors. The shaded nodes execute on CPU2 and the non-shaded nodes execute on CPU1. The generated code corresponding to this partitioned GRC is presented in Fig. 17. Compared to the sequentially

Figure 16: The partitioned GRC of the sketch example

executed version in Fig. 13, there are a few additions in Fig. 17:

- Coordination and synchronization between processors have been added.

- There are more than one cyclic executive such that each partition executes within its own cyclic executive.

Initially, only the first processor executes the root thread. The first processor therefore, is appointed as the *master* processor. The master processor is responsible for coordinating the *slave* processors by instructing them to start executing when the root thread forks. To allow multiple processors executing from the same binary, the *reactive function* of an Esterel program is translated into a *reentrant* function. The *reactive function* is then called from each processor. Subsequently, processors could share the same address space and communication between processors can be implemented using shared memory.

The *reactive function*, esterel\_module, requires only one argument to indicate whether it is executing on a master processor or one of the slave processors. The slave processors are immediately blocked on line 4 until the master processor instructs them to start. When the master processor reaches the fork on line 11, it instructs the slave processors to begin execution by sending the starting addresses of the partitions allocated to the slave processors. For the master processor, it continues at the label CPUO, while the slave processor begins from the label

<sup>&</sup>lt;sup>1</sup>Note that we present a more abstracted example than the example in Fig. 14 so as to be able to present the generated code (see Fig.17) within a one page limit.

```

1 int esterel_module(int isSlaveCPU) {

\mathbf{2}

if (isSlaveCPU) {

3

WAIT FORK:

wait_fork(pc); // Blocking

4

goto *pc;

\mathbf{5}

6

}

thread_1_pc = 0;

\mathbf{7}

thread 2 pc = 0;

lock S = 3; // Three potential emitters

8

9

\mathbf{10}

fork_cpu1(&&CPU1);

11

goto CPU0;

12

13 CPU1:

term\_p1 \ = \ 0\,;

14

\mathbf{15}

do {

term_1 = thread_1();

term_2 = thread_2();

term_p1 = term_1 | term_2;

16

17

\mathbf{18}

19

} while (term_p1 = INIFINITY);

\mathbf{20}

join_cpu1();

\mathbf{21}

goto WAIT FORK;

22 CPU0:

term\_p0~=~0;

\mathbf{23}

\mathbf{24}

do {

term 3 = thread 3(); // Definitions of thread 3() and thread 4()

term 4 = thread 4(); // are omitted to conserve space

term p0 = term 3 | term 4;

\mathbf{25}

\mathbf{26}

\mathbf{27}

} while (term_p 0 = INIFINITY);

\mathbf{28}

join_all(); // Blocking

term_0 = term_p0 | term_p1;

29

30

31

// ...

\mathbf{32}

}

33 int thread _1() {

\mathbf{34}

if (thread_1_pc)

goto *thread_1_pc;

35

36

. . .

37 RESUME:

if (lock_S) {

thread_1_1

38

pc = \& RESUME;

39

return INIFINITY;

\mathbf{40}

41

} else {

Inside the guarded body

\mathbf{42}

}

\mathbf{43}

44

// ...

\mathbf{45}

}

46 int thread _2() {

if (thread_2_pc)

47

goto *thread_2_pc;

\mathbf{48}

49

. .

lock_S = 0;

\mathbf{50}

\mathbf{51}

// ...

52 END:

\mathbf{53}

thread_1 pc = \& END;

54 }

```

Figure 17: The generated code of the partitioned sketch example

CPU1. Both processors initialize their corresponding termination codes before the loop for the cyclic executive is entered.

The cyclic executive of each partition runs independently of each other at their own pace. Like the sequential version in Fig. 13, the termination code of each thread have to be combined when threads join. However, combining is a two step process in Fig. 17: once at the end of each partition on lines 18 and 27, and a second time after processors join on line 30. To synchronously join the two processors, a rendezvous is set up on line 29. This line blocks the master processor until all slave processors are ready to join. In this case, the single slave processor calls join\_cpu1 on line 20 to indicate that it is ready to join.

To illustrate how the semantics of instantaneous broadcast is preserved when threads execute in parallel (on different cores), the consumer thread of the signal S has been deliberately scheduled before the potential emitters of S. More importantly, the example in Fig. 17 also demonstrates the elegance of run-time signal resolution working across processors. When the master processor sends the starting address to the slave processor on line 11, the slave processor has a headstart of a few instructions while the master processor sis being held back by the overhead of coordinating the slave processor. The master processor starts executing the third thread shortly after the slave processor started executing executing the first thread. At this point, lock\_S is locked when the first thread attempts to read S on line 18 and the first thread returns with a termination code of infinity. Assuming S is not emitted by either the third or the forth thread, lock\_S gets decremented twice. Let us also assume the second thread does not emit S when the slave processor execute it and lock\_S becomes zero. The cyclic executive on line 19 detects that the first thread has been locked and reschedules it. Since lock\_S is now released, the first thread is able to successfully terminate and join with other threads.

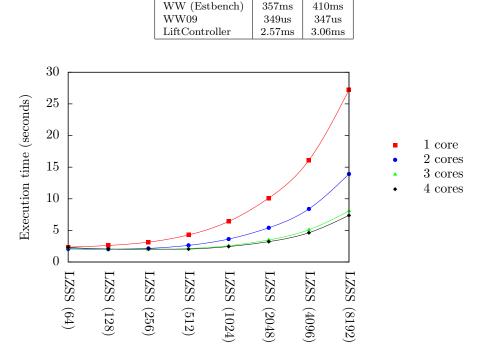

We summarize the static load distribution approach by highlighting the following salient features: